没有合适的资源?快使用搜索试试~ 我知道了~

TI-TPL0102-EP.pdf

需积分: 10 0 下载量 143 浏览量

2022-11-27

16:35:47

上传

评论 4

收藏 1.13MB PDF 举报

温馨提示

试读

36页

TI-TPL0102-EP.pdf

资源推荐

资源详情

资源评论

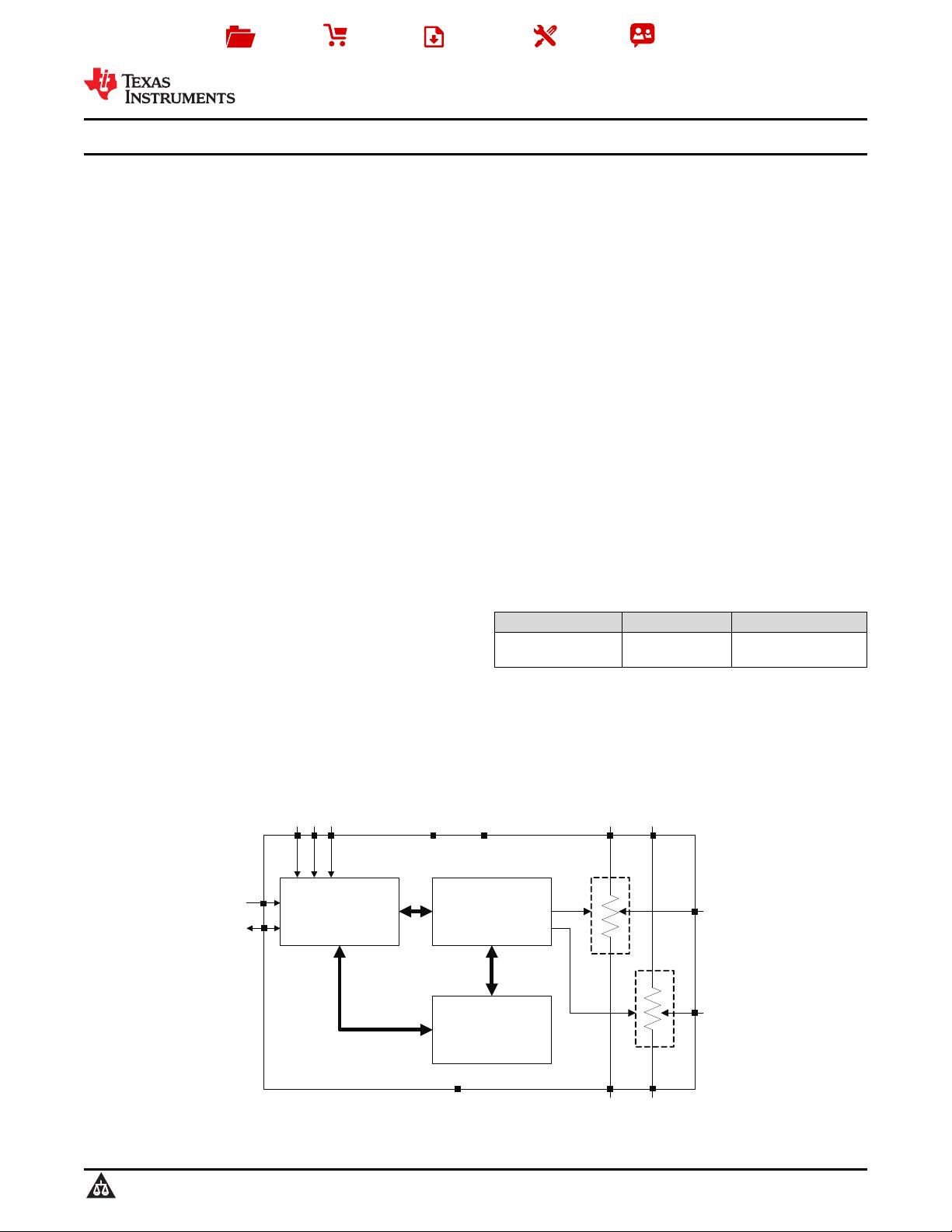

I

2

C INTERFACE

VOLATILE

REGISTERS

NON-VOLATILE

REGISTERS

A0 A1 A2 HA

LA

HB

LB

WA

WB

VDD VSS

GND

SDA

SCL

Product

Folder

Sample &

Buy

Technical

Documents

Tools &

Software

Support &

Community

TPL0102-EP

SLIS149 –JUNE 2014

TPL0102-EP 256-Taps Dual-Channel Digital Potentiometer With Non-Volatile Memory

1 Features 2 Applications

1

• Dual-Channel, 256-Position Resolution

• Adjustable Gain Amplifiers and Offset Trimming

• Non-Volatile Memory Stores Wiper Settings • Adjustable Power Supplies

• 2-mm × 2-mm, 14-Pin TSSOP Package • Precision Calibration of Set Point Thresholds

• 100-kΩ End-to-End Resistance (TPL0102-100) • Sensor Trimming and Calibration

• Fast Power-Up Response Time to Wiper Setting: • Mechanical Potentiometer Replacement

<100 µs

3 Description

• ±0.5 LSB INL, ±0.25 LSB DNL (Voltage-Divider

The TPL0102-EP is a two-channel, linear-taper digital

Mode)

potentiometer with 256 wiper positions. Each

• 4 ppm/°C Ratiometric Temperature Coefficient

potentiometer can be used as a three-terminal

• I

2

C-Compatible Serial Interface

potentiometer or as a two-terminal rheostat. The

• 2.7- to 5.5-V Single-Supply Operation

TPL0102-EP-100 has an end-to-end resistance of

100 kΩ.

• ±2.25 to ±2.75 V Dual-Supply Operation

The TPL0102-EP has non-volatile memory

• Operating Temperature Range From

(EEPROM) which can be used to store the wiper

–40°C to 125°C

position. The internal registers of the TPL0102-EP

• ESD Performance Tested Per JESD 22

can be accessed using the I

2

C interface.

– 2000-V Human Body Model

The TPL0102-EP is available in a 14-pin TSSOP

(A114-B, Class II)

package with a specified temperature range of –40°C

• Supports Defense, Aerospace, and Medical

to 125°C.

Applications

– Controlled Baseline

Device Information

(1)

ORDER NUMBER PACKAGE BODY SIZE (NOM)

– One Assembly and Test Site

TPL0102-

– One Fabrication Site

TSSOP (14) 5.00 mm × 4.40 mm

100QPWREP

– Available in Extended (Q) Temperature –40°C

(1) For all available packages, see the orderable addendum at

to 125°C

the end of the data sheet.

– Extended Product Life Cycle

– Extended Product-Change Notification

– Product Traceability

4 Functional Block Diagram

1

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications,

intellectual property matters and other important disclaimers. PRODUCTION DATA.

TPL0102-EP

SLIS149 –JUNE 2014

www.ti.com

Table of Contents

8.1 Overview ................................................................. 12

1 Features.................................................................. 1

8.2 Functional Block Diagram ....................................... 12

2 Applications ........................................................... 1

8.3 Feature Description................................................. 13

3 Description ............................................................. 1

8.4 Device Functional Modes........................................ 22

4 Functional Block Diagram .................................... 1

8.5 Register Maps......................................................... 23

5 Revision History..................................................... 2

9 Application and Implementation ........................ 26

6 Pin Configuration and Functions......................... 3

9.1 Application Information............................................ 26

7 Specifications......................................................... 4

9.2 Typical Application ................................................. 26

7.1 Absolute Maximum Ratings ...................................... 4

10 Layout................................................................... 27

7.2 Handling Ratings....................................................... 4

10.1 Layout Example .................................................... 27

7.3 Recommended Operating Conditions....................... 4

11 Device and Documentation Support ................. 29

7.4 Thermal Information.................................................. 5

11.1 Trademarks........................................................... 29

7.5 Electrical Characteristics........................................... 6

11.2 Electrostatic Discharge Caution............................ 29

7.6 Operating Characteristics.......................................... 8

11.3 Glossary................................................................ 29

7.7 Timing Requirements................................................ 9

12 Mechanical, Packaging, and Orderable

7.8 Typical Characteristics............................................ 10

Information ........................................................... 29

8 Detailed Description ............................................ 12

5 Revision History

DATE REVISION NOTES

June 2014 * Initial release.

2 Submit Documentation Feedback Copyright © 2014, Texas Instruments Incorporated

HA

LA

WA

HB

LB

WB

A2

VDD

A0

A1

GND

SCL

SDA

VSS

1

2

3

4

5

6

7

14

13

12

11

10

9

8

TPL0102-EP

www.ti.com

SLIS149 –JUNE 2014

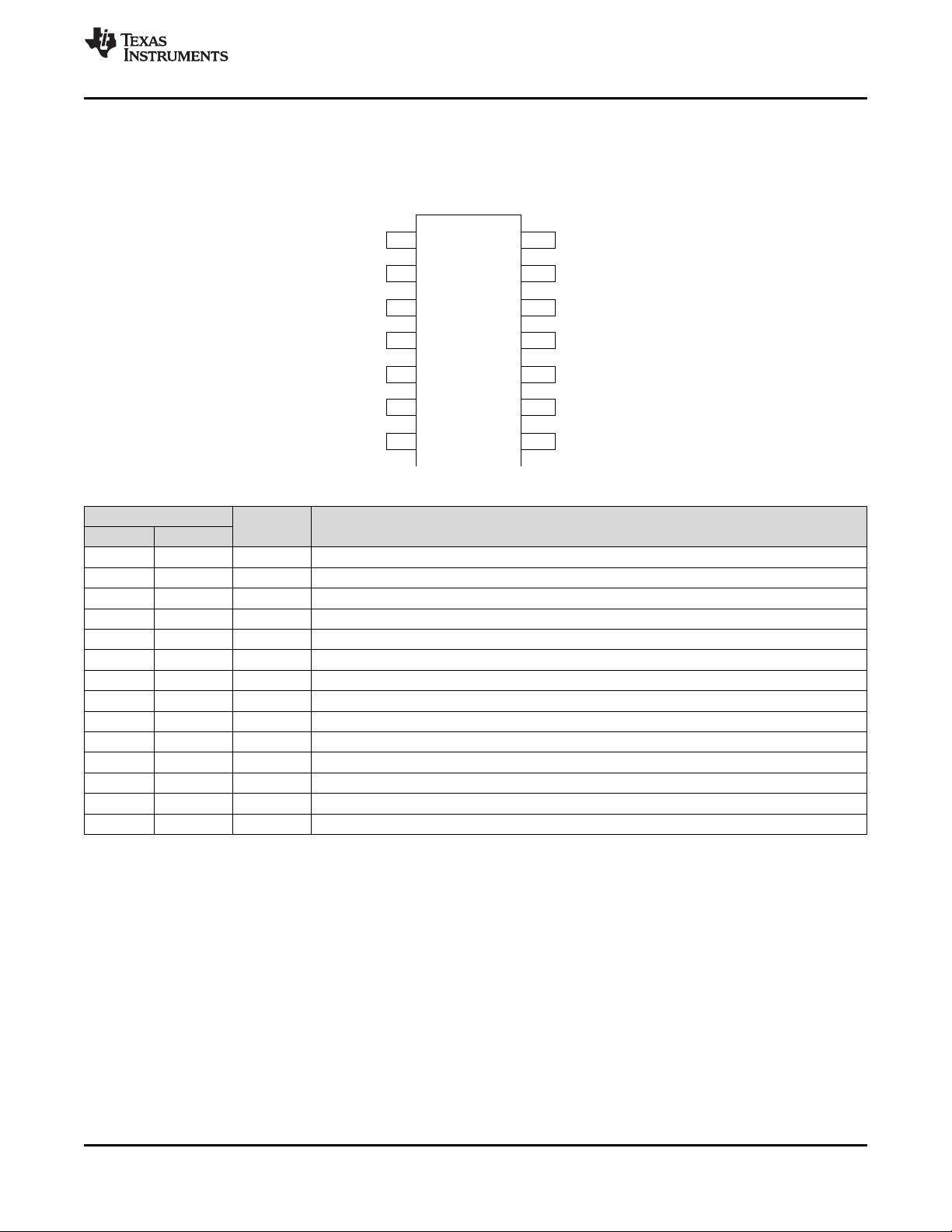

6 Pin Configuration and Functions

TSSOP – PW Package

14 Pins

(Top View)

Pin Functions

PIN

I/O DESCRIPTION

NAME NO.

HA 1 I/O High pin of potentiometer A

LA 2 I/O Low pin of potentiometer A

WA 3 I/O Wiper pin of potentiometer A

HB 4 I/O High pin of potentiometer B

LB 5 I/O Low pin of potentiometer B

WB 6 I/O Wiper pin of potentiometer B

A2 7 I Address bit 2

VSS 8 Power Negative or GND power supply pin

SDA 9 I/O I

2

C data I/O

SCL 10 I I

2

C clock input

GND 11 — Ground

A1 12 I Address bit 1

A0 13 I Address bit 0

VDD 14 Power Positive power supply pin

Copyright © 2014, Texas Instruments Incorporated Submit Documentation Feedback 3

TPL0102-EP

SLIS149 –JUNE 2014

www.ti.com

7 Specifications

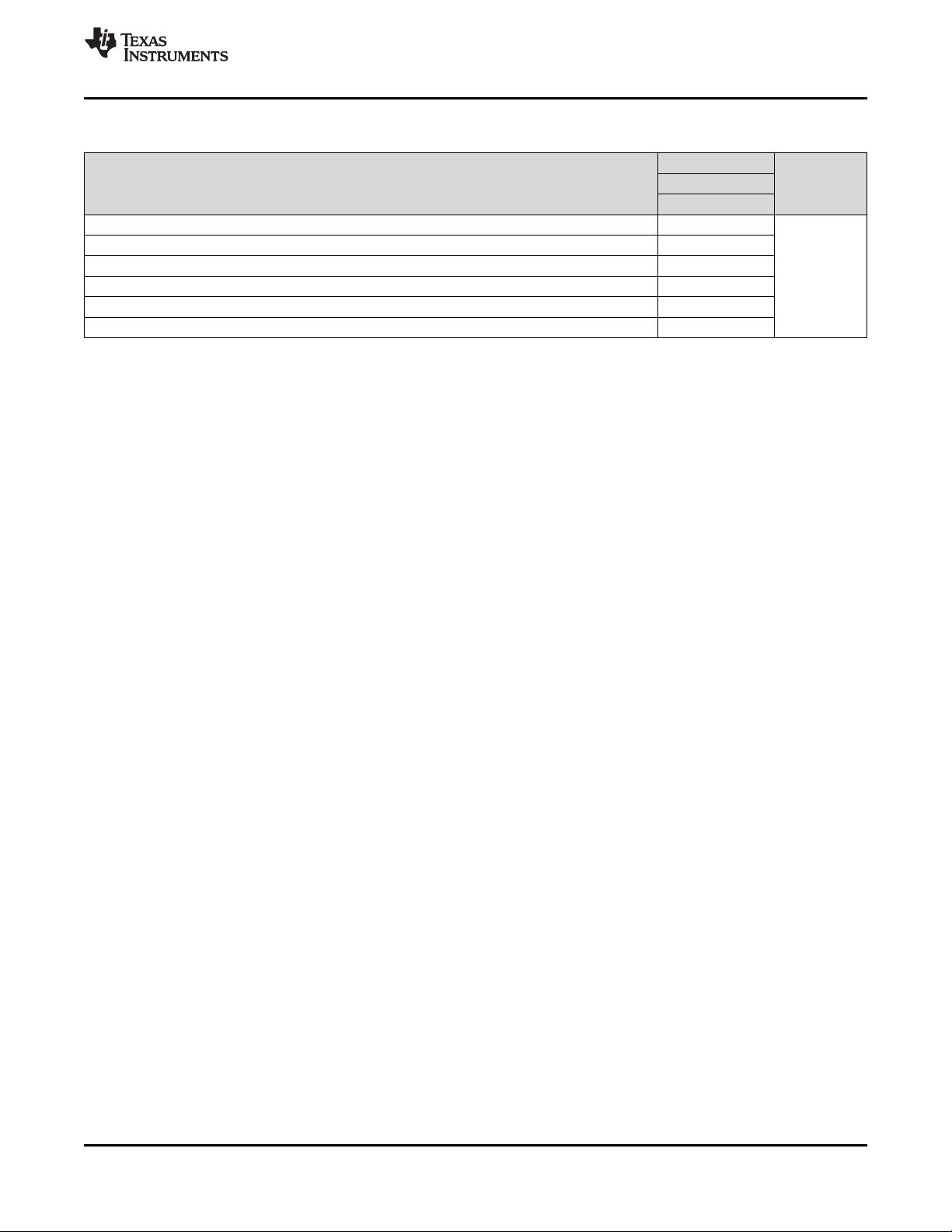

7.1 Absolute Maximum Ratings

(1)(2)(3)

MIN MAX UNIT

V

DD

to GND –0.3 7 V

V

SS

to GND Supply voltage –7 0.3 V

V

DD

to V

SS

7 V

V

H

, V

L

, V

W

Voltage at resistor pins V

SS

– 0.3 V

DD

+ 0.3 V

V

I

Digital input voltage –0.3 V

DD

+ 0.3 V

Pulse current ±20 mA

I

H

, I

L

, I

W

Continuous current ±2 mA

(1) Stresses above these ratings may cause permanent damage. Exposure to absolute maximum conditions for extended periods may

degrade device reliability. These are stress ratings only, and functional operation of the device at these or any other conditions beyond

those specified is not implied.

(2) The algebraic convention, whereby the most negative value is a minimum and the most positive value is a maximum.

(3) All voltages are with respect to ground, unless otherwise specified.

7.2 Handling Ratings

MIN MAX UNIT

T

stg

Storage temperature range –65 150 °C

7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

MIN MAX UNIT

Single supply operation (V

SS

= 0 V) 2.7 5.5

V

DD

, V

SS

V

Dual supply operation ±2.25 ±2.75

V

H

, V

L

Pin voltage V

SS

V

DD

V

V

IH

Voltage input high (SCL, SDA, A0, A1, A2) 0.7 × V

DD

5.5 V

V

IL

Voltage input low (SCL, SDA, A0, A1, A2) 0 0.3 × V

DD

V

I

W

Wiper current ±2 mA

T

J

Junction temperature –40 125 °C

4 Submit Documentation Feedback Copyright © 2014, Texas Instruments Incorporated

TPL0102-EP

www.ti.com

SLIS149 –JUNE 2014

7.4 Thermal Information

TPL0102-EP

THERMAL METRIC

(1)

PW UNIT

14 PINS

R

θJA

Junction-to-ambient thermal resistance

(2)

112.9

R

θJC(top)

Junction-to-case (top) thermal resistance

(3)

39.9

R

θJB

Junction-to-board thermal resistance

(4)

55.9

°C/W

ψ

JT

Junction-to-top characterization parameter

(5)

3.5

ψ

JB

Junction-to-board characterization parameter

(6)

55.2

R

θJC(bot)

Junction-to-case (bottom) thermal resistance

(7)

N/A

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

(2) The junction-to-ambient thermal resistance under natural convection is obtained in a simulation on a JEDEC-standard, high-K board, as

specified in JESD51-7, in an environment described in JESD51-2a.

(3) The junction-to-case (top) thermal resistance is obtained by simulating a cold plate test on the package top. No specific JEDEC-

standard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

(4) The junction-to-board thermal resistance is obtained by simulating in an environment with a ring cold plate fixture to control the PCB

temperature, as described in JESD51-8.

(5) The junction-to-top characterization parameter, ψ

JT

, estimates the junction temperature of a device in a real system and is extracted

from the simulation data for obtaining θ

JA

, using a procedure described in JESD51-2a (sections 6 and 7).

(6) The junction-to-board characterization parameter, ψ

JB

, estimates the junction temperature of a device in a real system and is extracted

from the simulation data for obtaining θ

JA

, using a procedure described in JESD51-2a (sections 6 and 7).

(7) The junction-to-case (bottom) thermal resistance is obtained by simulating a cold plate test on the exposed (power) pad. No specific

JEDEC standard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

Spacer

Copyright © 2014, Texas Instruments Incorporated Submit Documentation Feedback 5

剩余35页未读,继续阅读

资源评论

不觉明了

- 粉丝: 3164

- 资源: 5429

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 基于matlab实现本份代码能对图像进行gabor滤波处理,结合指纹方向图以及指纹沟壑频率特性,对指纹图像进行增强.rar

- 基于matlab实现RBM神经网络实现了手写数字体识别的GUI程序.rar

- 基于matlab实现蝙蝠算法优化相关向量机建模对数据进行建模和预测.rar

- 基于matlab实现编写的禁忌搜索算法,解决了TSP问题,对初学者有重要的参考价值.rar

- 基于matlab实现SOH关于IMU进行姿态求解的C代码,里面包含了两套代码,分别是重力约束法求解和梯度下降法求解.rar

- 1_简单电子邮件客户端.zip

- 基于matlab实现powell优化搜索算法,适合于多参数优化且目标函数中不包含参数的情况.rar

- 基于matlab实现PID神经网络前向和反向学习算法的matlab的原程序代码.rar

- 基于matlab实现nsga-2的多目标优化算法,有注解.rar

- AIR-AP1815-K9-ME-8-5-182-0.zipFor 1815 1830 1840 1850 2700 3700

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功