没有合适的资源?快使用搜索试试~ 我知道了~

TI-LM5050-2.pdf

需积分: 9 0 下载量 72 浏览量

2022-11-15

23:57:37

上传

评论 5

收藏 1.14MB PDF 举报

温馨提示

试读

24页

TI-LM5050-2.pdf

资源推荐

资源详情

资源评论

V

IN

V

OUT

GND

OFF

OUT

IN

GATE

LM5050-2

Shutdown

GND

GND

nFGD

Low= FET On, High= FET Off

+6V to +75V

Status

V

LOGIC

Low= OK, High= Fault

R

PULL-UP

LM5050-2

www.ti.com

SNVS679B –NOVEMBER 2010–REVISED MARCH 2013

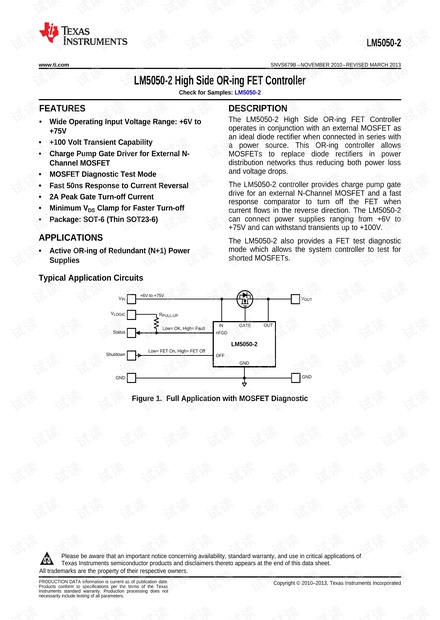

LM5050-2 High Side OR-ing FET Controller

Check for Samples: LM5050-2

1

FEATURES

DESCRIPTION

The LM5050-2 High Side OR-ing FET Controller

2

• Wide Operating Input Voltage Range: +6V to

operates in conjunction with an external MOSFET as

+75V

an ideal diode rectifier when connected in series with

• +100 Volt Transient Capability

a power source. This OR-ing controller allows

• Charge Pump Gate Driver for External N-

MOSFETs to replace diode rectifiers in power

distribution networks thus reducing both power loss

Channel MOSFET

and voltage drops.

• MOSFET Diagnostic Test Mode

The LM5050-2 controller provides charge pump gate

• Fast 50ns Response to Current Reversal

drive for an external N-Channel MOSFET and a fast

• 2A Peak Gate Turn-off Current

response comparator to turn off the FET when

• Minimum V

DS

Clamp for Faster Turn-off

current flows in the reverse direction. The LM5050-2

can connect power supplies ranging from +6V to

• Package: SOT-6 (Thin SOT23-6)

+75V and can withstand transients up to +100V.

APPLICATIONS

The LM5050-2 also provides a FET test diagnostic

mode which allows the system controller to test for

• Active OR-ing of Redundant (N+1) Power

shorted MOSFETs.

Supplies

Typical Application Circuits

Figure 1. Full Application with MOSFET Diagnostic

1

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

2All trademarks are the property of their respective owners.

PRODUCTION DATA information is current as of publication date.

Copyright © 2010–2013, Texas Instruments Incorporated

Products conform to specifications per the terms of the Texas

Instruments standard warranty. Production processing does not

necessarily include testing of all parameters.

OFF

GATE

OUT

IN

1

2

3

6

5

4

nFGD

GND

LM5050MK-2

PS1

PS2

IN

GATE

OUT

IN GATE OUT

R

LOAD

C

LOAD

LM5050-2

LM5050-2

GND

GND

LM5050-2

SNVS679B –NOVEMBER 2010–REVISED MARCH 2013

www.ti.com

Figure 2. Typical Redundant Supply Configuration

Connection Diagram

Figure 3. LM5050MK-2

SOT-6 Package (Top View)

PIN DESCRIPTIONS

Pin # Name Function

Open drain output for the FET Test circuit. Status pin used in

conjunction with the OFF test mode pin. When the OFF pin is in the

logic high state, an active low state on nFGD indicates that the forward

1 nFGD

voltage (from source to drain) of the external MOSFET is greater than

350 mV. The nFGD pin requires an external pull-up resistor to a voltage

not higher than 5.5V.

2 GND Ground return for the controller

FET Test Mode control input. Logic low or open state at the OFF pin

will deactivate the FET Test Mode. A logic high state at the OFF pin will

pull the GATE pin low and turn off the external MOSFET. If the body

3 OFF diode forward voltage of the MOSFET (from source to drain) is greater

than 350mV when the OFF pin is in the high state, the nFGD pin will

indicate that the MOSFET is not shorted by pulling to the active low

state.

Voltage sense connection to the external MOSFET Source pin and

4 IN

supply input to the internal charge pump.

5 GATE Connection to the external MOSFET Gate.

Voltage sense connection to the external MOSFET Drain pin and

6 OUT

supply pin for biasing the internal control circuitry.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam

during storage or handling to prevent electrostatic damage to the MOS gates.

2 Submit Documentation Feedback Copyright © 2010–2013, Texas Instruments Incorporated

Product Folder Links: LM5050-2

LM5050-2

www.ti.com

SNVS679B –NOVEMBER 2010–REVISED MARCH 2013

Absolute Maximum Ratings

(1)(2)

IN, OUT Pins to Ground

(3)

-0.3V to 100V

GATE Pin to Ground

(3)

-0.3V to 100V

OFF Pin to Ground -0.3V to 7V

nFGD Pin to Ground (Off) -0.3V to 7V

Storage Temperature Range −65°C to 150°C

ESD

HBM

(4)

2 kV

MM

(5)

150V

Peak Reflow Temperature

(6)

260°C, 30sec

(1) If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/ Distributors for availability and

specifications.

(2) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur, including in-operability and degradation of

device reliability and/or performance. Functional operation of the device and/or non-degradation at the Absolute Maximum Ratings or

other conditions beyond those indicated in the Recommended Operating Conditions is not implied. Operating Range conditions indicate

the conditions at which the device is functional and the device should not be operated beyond such conditions. For specifications and

conditions, see Electrical Characteristics.

(3) The GATE pin voltage is typically 12V above the IN pin voltage when the LM5050-2 is enabled (i.e. OFF Pin is Open or Low, and V

IN

>

V

OUT

). Therefore, the Absolute Maximum Rating for the IN pin voltage applies only when the LM5050-2 is disabled (i.e. OFF Pin is logic

high), or for a momentary surge to that voltage since the Absolute Maximum Rating for the GATE pin is also 100V

(4) The Human Body Model (HBM) is a 100 pF capacitor discharged through a 1.5 kΩ resistor into each pin. Applicable test standard is

JESD-22-A114-C.

(5) The Machine Model (MM) is a 200 pF capacitor discharged through a 0Ω resistor (i.e. directly) into each pin. Applicable test standard is

JESD-A115-A.

(6) For soldering specifications visit www.ti.com.

Operating Ratings

(1)

IN, OUT Pins +6.0V to +75V

OFF Pin Voltage 0.0V to 5.5V

nFGD Voltage (Off) 0.0V to 5.5V

nFGD Sink Current (On) 0 mA to 1 mA

Junction Temperature Range (T

J

) −40°C to +125°C

(1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur, including in-operability and degradation of

device reliability and/or performance. Functional operation of the device and/or non-degradation at the Absolute Maximum Ratings or

other conditions beyond those indicated in the Recommended Operating Conditions is not implied. Operating Range conditions indicate

the conditions at which the device is functional and the device should not be operated beyond such conditions. For specifications and

conditions, see Electrical Characteristics.

Copyright © 2010–2013, Texas Instruments Incorporated Submit Documentation Feedback 3

Product Folder Links: LM5050-2

LM5050-2

SNVS679B –NOVEMBER 2010–REVISED MARCH 2013

www.ti.com

Electrical Characteristics

Limits in standard type are for T

J

= 25°C only; limits in boldface type apply over the operating junction temperature (T

J

)

range of -40°C to +125°C. Minimum and Maximum limits are specified through test, design, or statistical correlation. Typical

values represent the most likely parametric norm at T

J

= 25°C, and are provided for reference purposes only. Unless

otherwise stated the following conditions apply: V

IN

= 12.0V, V

OUT

= 12.0V, V

OFF

= 0.0V, C

GATE

= 47 nF, and T

J

= 25°C.

Symbol Parameter Conditions Min Typ Max Unit

IN Pin

V

IN

Operating Supply Range 6.0 - 75.0 V

V

IN

= 6.0V

GATE = Open 180 240 300

V

OUT

= V

IN

- 100 mV

V

IN

= 12.0V

I

IN

IN Pin current GATE = Open 262 350 440 μA

V

OUT

= V

IN

- 100 mV

V

IN

= 75.0V

GATE = Open 275 355 460

V

OUT

= V

IN

- 100 mV

OUT Pin

V

IN

= 6.0V

74 95 115

V

OUT

= V

IN

- 100 mV

V

IN

= 12.0V

I

OUT

OUT Pin Current 70 110 160 uA

V

OUT

= V

IN

- 100 mV

V

IN

= 75.0V

35 125 265

V

OUT

= V

IN

- 100 mV

GATE Pin

V

IN

= 6.0V to 75V

I

GATE(ON)

GATE Pin Source Current V

GATE

= V

IN

18.0 32. 45.0 uA

V

OUT

= V

IN

- 175 mV

V

IN

= 6.0V

6.0 6.8 7.4

V

OUT

= V

IN

- 175 mV

V

IN

= 12.0V

V

GS

V

GATE

- V

IN

in Forward Operation

(1)

8.0 11.5 14.7 V

V

OUT

= V

IN

- 175 mV

V

IN

= 75.0V

8.0 11 14.5

V

OUT

= V

IN

- 175 mV

C

GATE

= 0

(2)

- 27 100

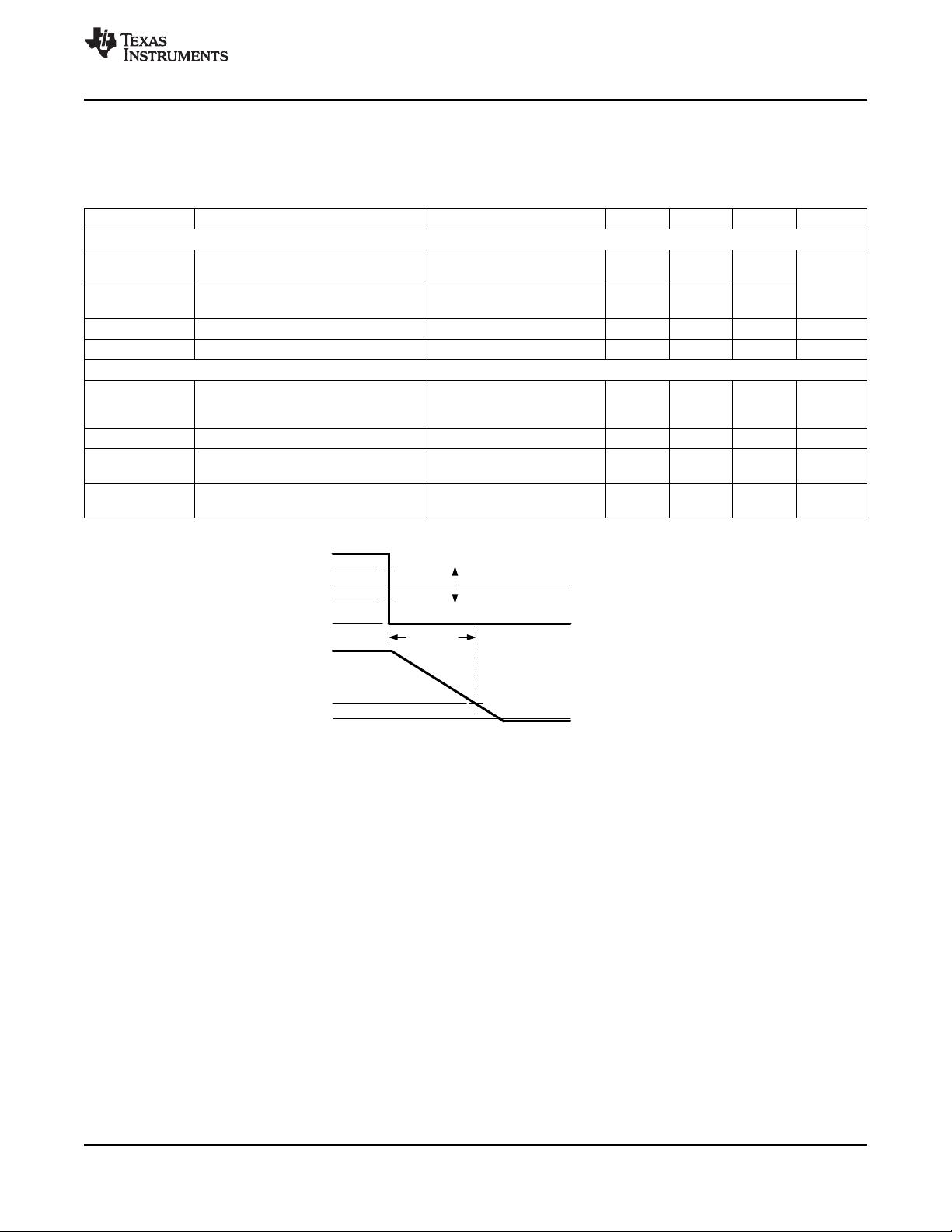

Gate Capacitance Discharge Time at

t

GATE(REV)

Forward to Reverse Transition C

GATE

= 10 nF

(2)

- 61 - ns

See Figure 4

C

GATE

= 47 nF

(2)

- 205 425

Gate Capacitance DischargeTime at

t

GATE(OFF)

OFF pin Low to High Transition C

GATE

= 47 nF

(3)

- 450 - ns

See Figure 5

V

GATE

= V

IN

+ 3V

I

GATE(OFF)

GATE Pin Sink Current V

OUT

> V

IN

+ 100 mV 1.9 2.8 - A

t ≤ 10ms

Reverse V

SD

Threshold

V

SD(REV)

V

IN

- V

OUT

-37 -27 -17 mV

V

IN

< V

OUT

ΔV

SD(REV)

Reverse V

SD

Hysteresis - 10 - mV

V

IN

= 6.0V

6 20 33

V

IN

- V

OUT

Regulated Forward V

SD

Threshold

V

SD(REG)

mV

V

IN

> V

OUT

V

IN

= 12.0V

2 16 31

V

IN

- V

OUT

(1) Measurement of V

GS

voltage (i.e. V

GATE

- V

IN

) includes 1 MΩ in parallel with C

GATE

(2) Time from V

IN

-V

OUT

voltage transition from 200mV to -500mV until GATE pin voltage falls to V

IN

+ 1V. See Figure 4

(3) Time from V

OFF

voltage transition from 0.0V to 5.0V until GATE pin voltage falls to V

IN

+ 1V. See Figure 5

4 Submit Documentation Feedback Copyright © 2010–2013, Texas Instruments Incorporated

Product Folder Links: LM5050-2

V

IN

- V

OUT

V

GATE

- V

IN

0.0V

1.0V

0 mV

V

SD(REV)

-500 mV

V

SD(REG)

200 mV

V

GATE

V

IN

> V

OUT

V

IN

< V

OUT

t

GATE(OFF)

LM5050-2

www.ti.com

SNVS679B –NOVEMBER 2010–REVISED MARCH 2013

Electrical Characteristics (continued)

Limits in standard type are for T

J

= 25°C only; limits in boldface type apply over the operating junction temperature (T

J

)

range of -40°C to +125°C. Minimum and Maximum limits are specified through test, design, or statistical correlation. Typical

values represent the most likely parametric norm at T

J

= 25°C, and are provided for reference purposes only. Unless

otherwise stated the following conditions apply: V

IN

= 12.0V, V

OUT

= 12.0V, V

OFF

= 0.0V, C

GATE

= 47 nF, and T

J

= 25°C.

Symbol Parameter Conditions Min Typ Max Unit

OFF Pin

V

OUT

= V

IN

-500 mV

V

OFF(IH)

OFF Input High Threshold Voltage - 1.55 1.73

V

OFF

Rising

V

V

OUT

= V

IN

- 500 mV

V

OFF(IL)

OFF Input Low Threshold Voltage 1.09 1.41 -

V

OFF

Falling

ΔV

OFF

OFF Threshold Voltage Hysteresis V

OFF(IH)

- V

OFF(IL)

- 160 - mV

I

OFF

OFF Pin Internal Pull-down V

OFF

= 5.0V 2.0 5 8.0 µA

nFGD Pin

V

OFF

= 5V

FET Test Threshold Voltage

V

SD(TST)

V

OUT

= 12V 250 350 450 mV

V

IN

< V

OUT

V

IN

falling from 12V

ΔV

SD(TST)

FET Test Threshold Voltage Hysteresis - 95 - mV

nFGD Output Low Voltage V

OFF

= 5V

nFGD

VOL

- 630 850 mV

nFGD Output = On I

nFGD

= 1 mA Sinking

nFGD Output Leakage Current V

OFF

= 0V

nFGD

IOL

- 0.001 0.7 µA

nFGD Output = Off V

nFGD

= 5.5V

Figure 4. Gate Off Timing for Forward to Reverse Transition

Copyright © 2010–2013, Texas Instruments Incorporated Submit Documentation Feedback 5

Product Folder Links: LM5050-2

剩余23页未读,继续阅读

资源评论

不觉明了

- 粉丝: 3203

- 资源: 5558

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功