没有合适的资源?快使用搜索试试~ 我知道了~

TI-LM98640QML-SP.pdf

需积分: 5 0 下载量 84 浏览量

2022-12-04

22:32:17

上传

评论 4

收藏 787KB PDF 举报

温馨提示

试读

54页

TI-LM98640QML-SP.pdf

资源详情

资源评论

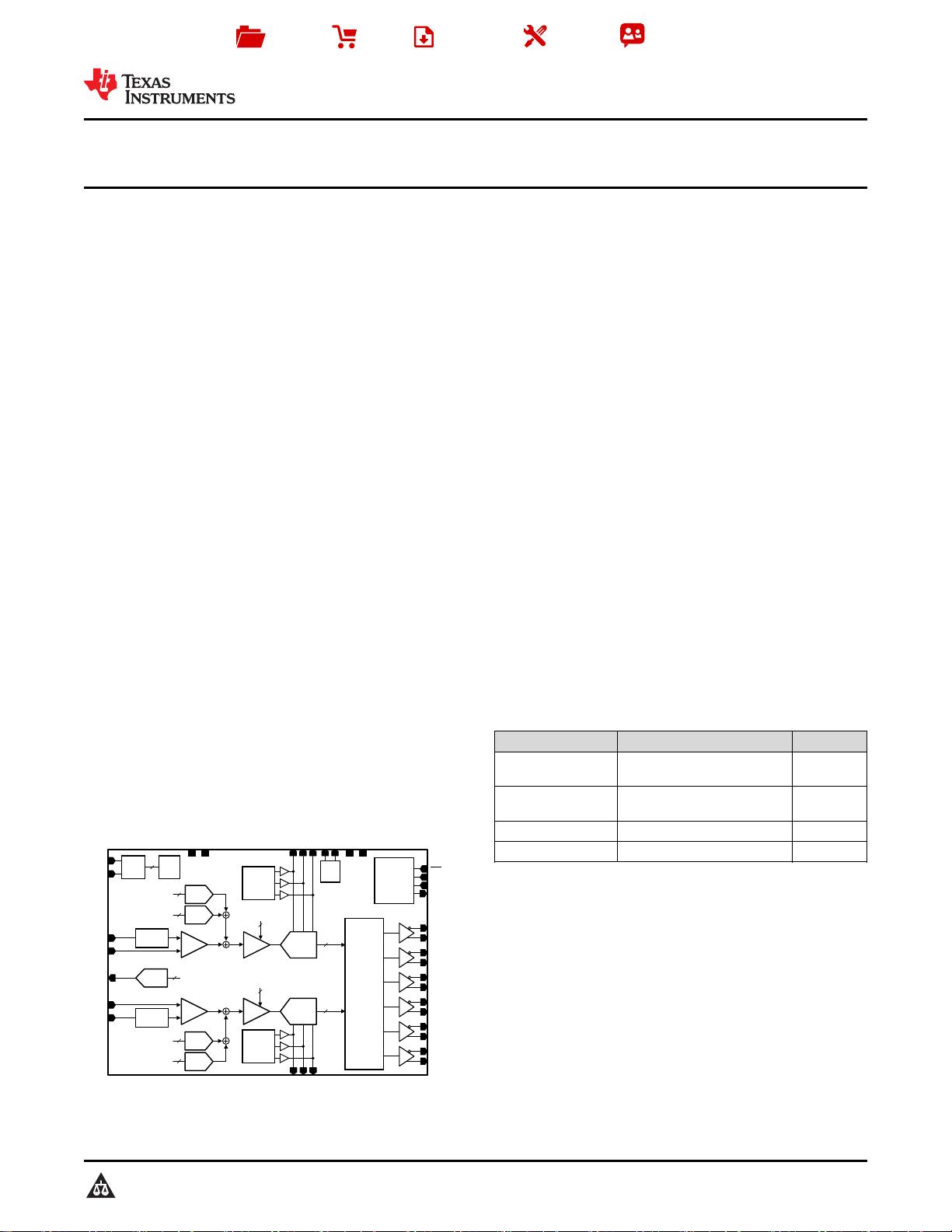

Digital

Control

and

Config

Registers

SCLK

SDI

SDO

TXFRM-

TXFRM+

TXOUT0-

TXOUT0+

TXOUT1-

TXOUT1+

TXOUT2-

TXOUT2+

TXOUT3-

TXCLK-

DLL ATG

64

PGA

SERIALIZER

TXOUT3+

TXCLK+

PGA

INTERNAL

REFERENCE

14 Bit

ADC

14

14

SEN

OS

1

+

OS

1

-

OS

2

+

OS

2

-

INCLK+

INCLK-

Input Bias/

Clamping

PGA1[7:0]

PGA2[7:0

]

INTERNAL

REFERENCE

VCOM2

VREFT2

VREFB2

VBG

VCLP

14 Bit

ADC

5

8

8

VCLP

Control[4:0]

VSS33

VDD33

VCOM1

VREFT1

VREFB1

IBIAS

VREFBG

VCLP

Reference

DAC

VDD18

VSS18

9

COARSE

DAC

FINE

DAC

CDAC1[

8:0]

FDAC1[

8:0]

9

Input Bias/

Clamping

CDS

S/H

+

-

CDS

S/H

+

-

9

COARSE

DAC

FINE

DAC

CDAC2[

8:0]

FDAC2[

8:0]

9

Product

Folder

Order

Now

Technical

Documents

Tools &

Software

Support &

Community

本文档旨在为方便起见,提供有关 TI 产品中文版本的信息,以确认产品的概要。 有关适用的官方英文版本的最新信息,请访问 www.ti.com,其内容始终优先。 TI 不保证翻译的准确

性和有效性。 在实际设计之前,请务必参考最新版本的英文版本。

English Data Sheet: SNAS461

LM98640QML-SP

ZHCSIZ1G –MAY 2010–REVISED NOVEMBER 2018

具具有有 LVDS 输输出出的的 LM98640QML-SP 抗抗辐辐射射加加固固 (RHA) 型型、、双双通通道道、、14

位位、、40MSPS 模模拟拟前前端端

1

1 特特性性

1

• 耐辐射

– TID 100krad(Si)

– 单粒子锁定 (SEL) 对于 LET 的抗扰度 =

120MeV-cm

2

/mg

– 在高达 120MeV-cm

2

/mg 的条件下无单粒子功

能中断 (SEFI)

– SMD 5962R1820301VXC

• ADC 分辨率:14 位

• ADC 采样速率:5MSPS 至 40MSPS

• 输入电平:2.85V

• 电源电压 3.3V 和 1.8V(标称值)

– 15MSPS 时的每通道功耗为 125mW

– 40MSPS 时的每通道功耗为 178mW

• 针对 CCD 或 CIS 传感器的 CDS 或 S/H 处理

– CDS 或 S/H 增益为 0dB 或 6dB

• 每个通道具有可编程模拟增益

– 256 步;范围 –3dB 至 18dB

• 可编程模拟失调电压校正

– 精细和粗略 DAC 分辨率 ±8 位

– 精细 DAC 范围 ±5mV

– 粗略 DAC 范围 ±250mV

• 可编程输入钳位电压

• 可编程采样边沿:1/64 像素周期

• 15MHz 时的 INL:±3.5LSB

• 本底噪声:–79dB

• 串扰:–80dB

• 工作温度:–55°C 至 125°C

2 应应用用

• 太空卫星科学 应用

– 焦平面电子学

– 成像姿态控制系统

– 地球成像

3 说说明明

LM98640QML-SP 是一种完全集成的高性能 14 位

5MSPS 至 40MSPS 信号处理解决方案。串行 LVDS

输出格式在单粒子曝光期间表现良好,可防止数据丢

失。LM98640QML-SP 具有自适应功率调节功能,可

根据工作频率和所需增益量优化功耗。借助创新型架

构,并利用相关双采样 (CDS) 技术 - 通常用于 CCD

阵列或采样保持 (S/H) 输入(用于 CIS 和 CMOS 图像

传感器),可实现高速信号吞吐量。采样边沿可编程为

1/64 像素周期的分辨率。CDS 和 S/H 都具有 0dB 或

6dB 的可编程增益。信号路径使用两个 ±8 位失调电压

校正 DAC 进行粗略和精细的失调电压校正,并使用可

为每个输入独立编程的 8 位可编程增益放大器

(PGA)。然后,信号将传送至两个片上 14 位 40MHz

高性能模数转换器 (ADC)。全差分处理通道提供卓越

的抗噪能力,在 1 倍增益下具有 –79dB 的极低本底噪

声。

器器件件信信息息

(1)

器器件件型型号号 等等级级 封封装装

5962R1820301VXC

QMLV RHA(SMD 器件)

[100krad(Si)]

CQFP (68)

LM98640W-MLS

飞行 RHA(非 SMD 器件)

[100krad(Si)]

CQFP (68)

LM96840W-MPR 工程样片

(2)

CQFP (68)

LM98640CVAL 陶瓷评估板 EVM

(1) 如需了解所有可用封装,请参阅数据表末尾的可订购产品附

录。

(2) 这些部件仅适用于工程评估。部件按照不合规的流程进行加工

处理。这些部件不适用于质检、生产、辐射测试或飞行。无法

在 –55°C 至 125°C 的完整 MIL 额定温度范围内或运行寿命中

保证这些器件的性能。

2

LM98640QML-SP

ZHCSIZ1G –MAY 2010–REVISED NOVEMBER 2018

www.ti.com.cn

版权 © 2010–2018, Texas Instruments Incorporated

目目录录

1 特特性性.......................................................................... 1

2 应应用用.......................................................................... 1

3 说说明明.......................................................................... 1

4 修修订订历历史史记记录录 ........................................................... 2

5 Pin Configuration and Functions......................... 4

6 Specifications......................................................... 7

6.1 Absolute Maximum Ratings ...................................... 7

6.2 ESD Ratings .................................................... 7

6.3 Recommended Operating Conditions....................... 7

6.4 Thermal Information ......................... 8

6.5 Quality Conformance Inspection............................... 8

6.6 LM98640QML-SP Electrical Characteristics............. 9

6.7 AC Timing Specifications....................................... 17

6.8 Typical Performance Characteristics ...................... 18

7 Detailed Description............................................ 20

7.1 Overview ................................................................. 20

7.2 Functional Block Diagram ....................................... 20

7.3 Feature Description................................................. 21

7.4 Device Functional Mode ......................................... 32

7.5 Programming........................................................... 34

7.6 Register Maps......................................................... 36

8 Application and Implementation ........................ 46

8.1 Application Information............................................ 46

8.2 Typical Application ................................................. 47

8.3 Initialization Set Up ................................................ 47

9 Layout ................................................................... 48

9.1 Layout Guidelines ................................................... 48

10 器器件件和和文文档档支支持持 ..................................................... 49

10.1 器件支持 ............................................................... 49

10.2 接收文档更新通知 ................................................. 49

10.3 社区资源................................................................ 49

10.4 出口管制提示......................................................... 49

10.5 商标 ....................................................................... 49

10.6 静电放电警告......................................................... 49

10.7 术语表 ................................................................... 49

11 机机械械、、封封装装和和可可订订购购信信息息....................................... 50

11.1 工程样片................................................................ 50

4 修修订订历历史史记记录录

Changes from Revision F (October 2018) to Revision G Page

• Changed pin diagram in Pin Configuration and Functions section to correct typographical error ......................................... 4

Changes from Revision E (December 2017) to Revision F Page

• 已删除 运行寿命测试 Delta 参数表 ......................................................................................................................................... 1

• 更新

特性

部分的列表项以包含 SMD 信息............................................................................................................................... 1

• 更新

应用

部分 ......................................................................................................................................................................... 1

• 已添加 向“器件信息”表中添加新的可订购器件 ........................................................................................................................ 1

• 已添加 工程样片脚注 .............................................................................................................................................................. 1

• 已删除 “器件信息”表中的 LM98640-MDR 和 LM9864-MDP................................................................................................... 1

• Updated thermal metrics ....................................................................................................................................................... 8

• Deleted 15 MHz and 25 MHz min/max spec........................................................................................................................ 11

• Changed ENOB typical for subgroup 6 at 25 MHz .............................................................................................................. 16

• Added minimum spec value for ENOB subgroups 4,5 at 40 MHz ...................................................................................... 16

• Changed pulses to windows................................................................................................................................................. 23

• Updated wording in CDS Mode CLAMP/SAMPLE Adjust section ...................................................................................... 23

• Updated wording in Input Bias and Clamping section ......................................................................................................... 24

Changes from Revision D (September 2015) to Revision E Page

• 已更改 在“器件信息”表中将 64 引线更改为 68 引线 ............................................................................................................... 1

3

LM98640QML-SP

www.ti.com.cn

ZHCSIZ1G –MAY 2010–REVISED NOVEMBER 2018

Copyright © 2010–2018, Texas Instruments Incorporated

Changes from Revision C (April 2013) to Revision D Page

• 根据新的数据表标准添加、更新或修订以下部分:

说明

、

引脚配置和功能

、

规格

、

详细 说明

、

应用和实施

、

电源建

议

、

布局

、

器件和文档支持

、

机械、封装和订购信息

............................................................................................................. 1

• Changed CLPIN I

IH

from 44 to 100 μA ................................................................................................................................... 9

• Changed SEN I

IH

from 28 to 100 μA ..................................................................................................................................... 9

• Changed SEN I

IL

from –70 to –100 μA................................................................................................................................... 9

• Changed INCLK I

IHL

from 36 to 100 μA ................................................................................................................................. 9

• Added mininum limits for t

DSO

, t

DSE

, t

QSR

and t

QHF

and deleted maximum limits................................................................... 17

• Added details on register write. ........................................................................................................................................... 34

• Changed Device Revision ID from x01 to x48 .................................................................................................................... 37

• Changed Device Revision ID from x01 to x48 .................................................................................................................... 45

• Added TID test and ELDRS-free information ...................................................................................................................... 46

Changes from Revision B (January 2011) to Revision C Page

• 将美国国家半导体数据表的布局更改为 TI 格式 ...................................................................................................................... 1

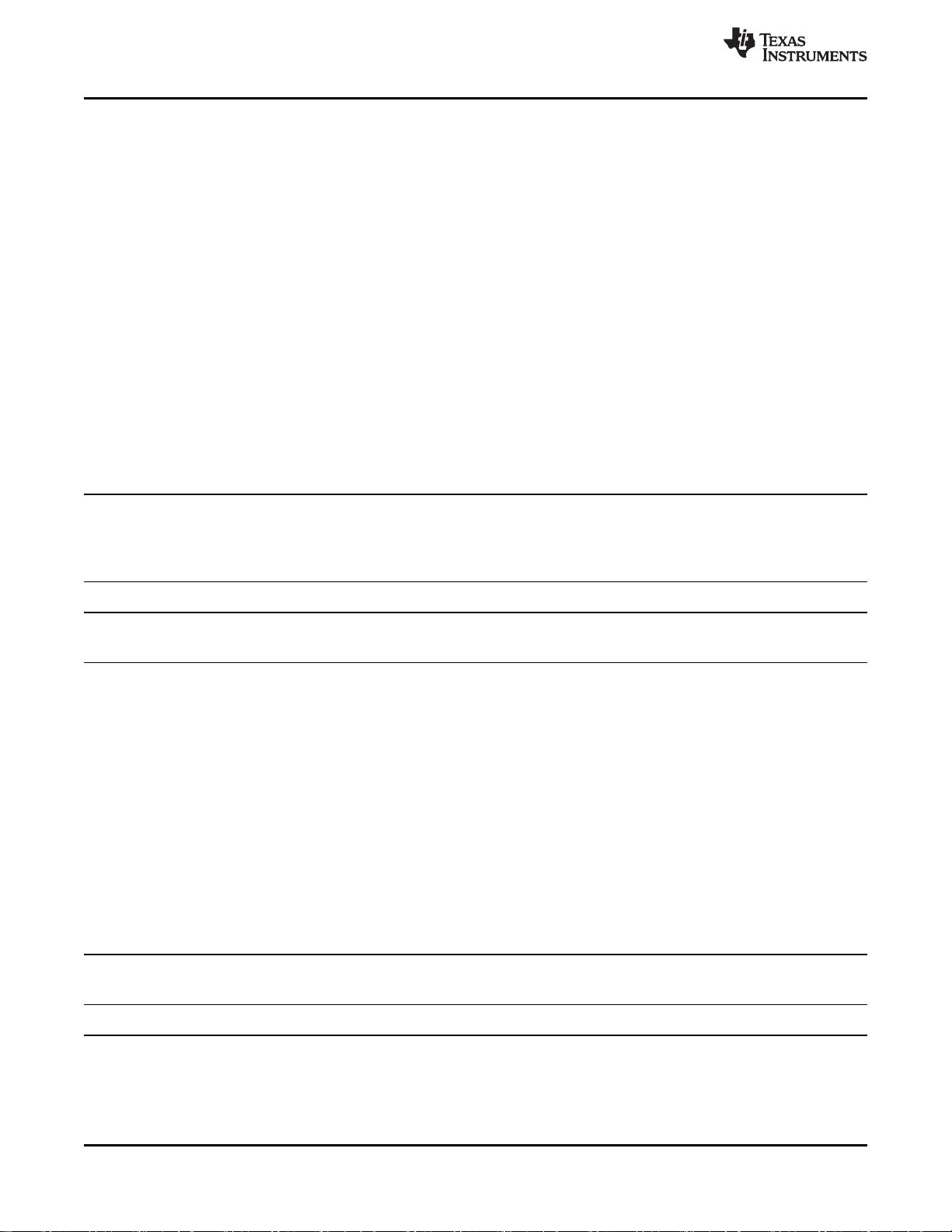

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1VCOM1

VDD33

VDD33

VSS33

VSS33

OS

1

-

OS

1

+

VSS33

VCLP

VSS33

OS

2

+

OS

2

-

VSS33

VSS33

VDD33

VDD33

VCOM2

VREFB2

VREFT2

VSS33

VSS33

VDD33

VDD33

VSS33

SDO

SDI

SCLK

CLPIN

VSS18

VDD18

DTM1

DTM0

ATB0

VDD18

VSS18

TXCLK-

TXCLK+

TXOUT0-

TXOUT0+

TXOUT1-

TXOUT1+

TXOUT2-

TXOUT2+

TXOUT3-

TXOUT3+

TXFRM-

TXFRM+

VSS18

VDD18

VREFB1

VREFT1

VSS33

VREFBG

IBIAS1

IBIAS0

VSS33

VDD33

VDD33

VSS33

VSS18

VSS18

VDD18

VDD18

ATB1

INCLK-

INCLK+

18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

68 67 66 65 64 63 62 61 60 59 58 57 56 55 54 53 52

NC

* Exposed pad is for thermal dissipation and must be soldered to

ground plane to ensure rated performance.

VSS33

LM98640QML-SP

68 Pin Ceramic QFP with Exposed Pad

(top view, exposed pad on bottom of package, not to scale)

SEN

4

LM98640QML-SP

ZHCSIZ1G –MAY 2010–REVISED NOVEMBER 2018

www.ti.com.cn

Copyright © 2010–2018, Texas Instruments Incorporated

5 Pin Configuration and Functions

68-Pin QFP

Package NBB0068D

Top View

5

LM98640QML-SP

www.ti.com.cn

ZHCSIZ1G –MAY 2010–REVISED NOVEMBER 2018

Copyright © 2010–2018, Texas Instruments Incorporated

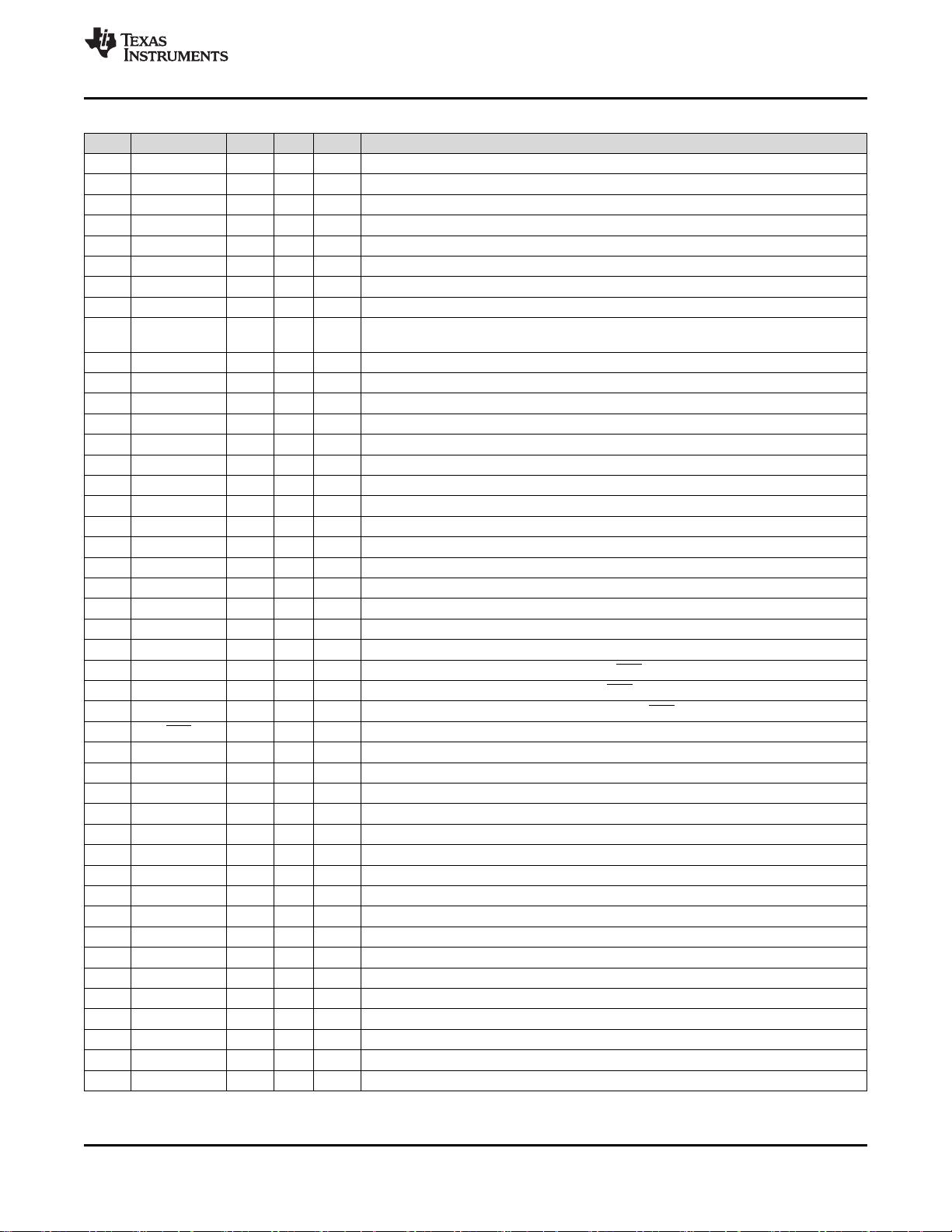

(1) (I = Input), (O = Output), (IO = Bi-directional), (P = Power), (D = Digital), (A = Analog), (PU = Pull Up with an internal resistor), (PD = Pull

Down with an internal resistor.).

Pin Functions

PIN NAME I/O

(1)

TYP RES DESCRIPTION

1 VCOM1 O A Common mode of ADC reference. Bypass with 0.1-µF capacitor to VSS33.

2 VDD33 P Analog power supply. Decouple with minimum 0.1-µF capacitor to VSS33 plane.

3 VDD33 P Analog power supply. Decouple with minimum 0.1-µF capacitor to VSS33 plane.

4 VSS33 P Analog supply return.

5 VSS33 P Analog supply return.

6 OS1- I A Analog input signal.

7 OS1+ I A Sample/Hold Mode Reference Level. Bypassed with a 0.1-µF to ground in CDS mode.

8 VSS33 P Analog supply return.

9 VCLP O A

Programmable Clamp Voltage output. Normally bypassed with a 0.1-µF capacitor to

VSS33.

10 VSS33 P Analog supply return.

11 OS2+ I A Sample/Hold Mode Reference Level. Bypassed with a 0.1-µF to ground in CDS mode.

12 OS2- I A Analog input signal.

13 VSS33 P Analog supply return.

14 VSS33 P Analog supply return.

15 VDD33 P Analog power supply. Decouple with minimum 0.1-µF capacitor to VSS33 plane.

16 VDD33 P Analog power supply. Decouple with minimum 0.1-µF capacitor to VSS33 plane.

17 VCOM2 O A Common mode of ADC reference. Bypass with 0.1-µF capacitor to ground.

18 VREFB2 O A Bottom of ADC reference. Bypass with a 0.1-µF capacitor to ground.

19 VREFT2 O A Top of ADC reference. Bypass with a 0.1-µF capacitor to ground.

20 VSS33 P Analog supply return.

21 VSS33 P Analog supply return.

22 VDD33 P Analog power supply. Decouple with minimum 0.1-µF capacitor to VSS33 plane.

23 VDD33 P Analog power supply. Decouple with minimum 0.1-µF capacitor to VSS33 plane.

24 VSS33 P Analog supply return.

25 SDO O D Serial Interface Data Output. (Tri-State when SEN is high)

26 SDI I D Serial Interface Data Input. (Tri-State when SEN is high)

27 SCLK I D PD Serial Interface shift register clock. (Tri-State when SEN is high)

28 SEN I D PU Active-low chip enable for the Serial Interface.

29 NC No Connection. Can be connected to VSS18.

30 CLPIN I D Input clamp signal.

31 VSS18 P Digital supply return.

32 VDD18 P Digital power supply. Decouple with minimum 0.1-µF capacitor to VSS18 plane.

33 DTM1 O D Digital Timing Monitor. If not used, can be connected to VDD18 through a 10-kΩ resistor.

34 DTM0 O D Digital Timing Monitor. If not used, can be connected to VDD18 through a 10-kΩ resistor.

35 VDD18 P Digital power supply. Decouple with minimum 0.1-µF capacitor to VSS18 plane.

36 VSS18 P Digital supply return.

37 TXFRM+ O D LVDS Frame+

38 TXFRM- O D LVDS Frame-

39 TXOUT3+ O D LVDS Data Out3+

40 TXOUT3- O D LVDS Data Out3-

41 TXOUT2+ O D LVDS Data Out2+

42 TXOUT2- O D LVDS Data Out2-

43 TXOUT1+ O D LVDS Data Out1+

44 TXOUT1- O D LVDS Data Out1-

45 TXOUT0+ O D LVDS Data Out0+

剩余53页未读,继续阅读

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论0

最新资源