实验7_同步时序电路典型设计1

需积分: 0 91 浏览量

更新于2022-08-03

收藏 3.66MB PDF 举报

实验7_同步时序电路典型设计1主要关注的是在计算机软硬件课程中,如何通过硬件描述语言(HDL)设计并实现同步时序电路,特别是32位同步二进制双向计数器。同步时序电路是数字逻辑设计的基础,它们在计算机系统和其他电子设备中扮演着关键角色,如计数、定时和数据处理。

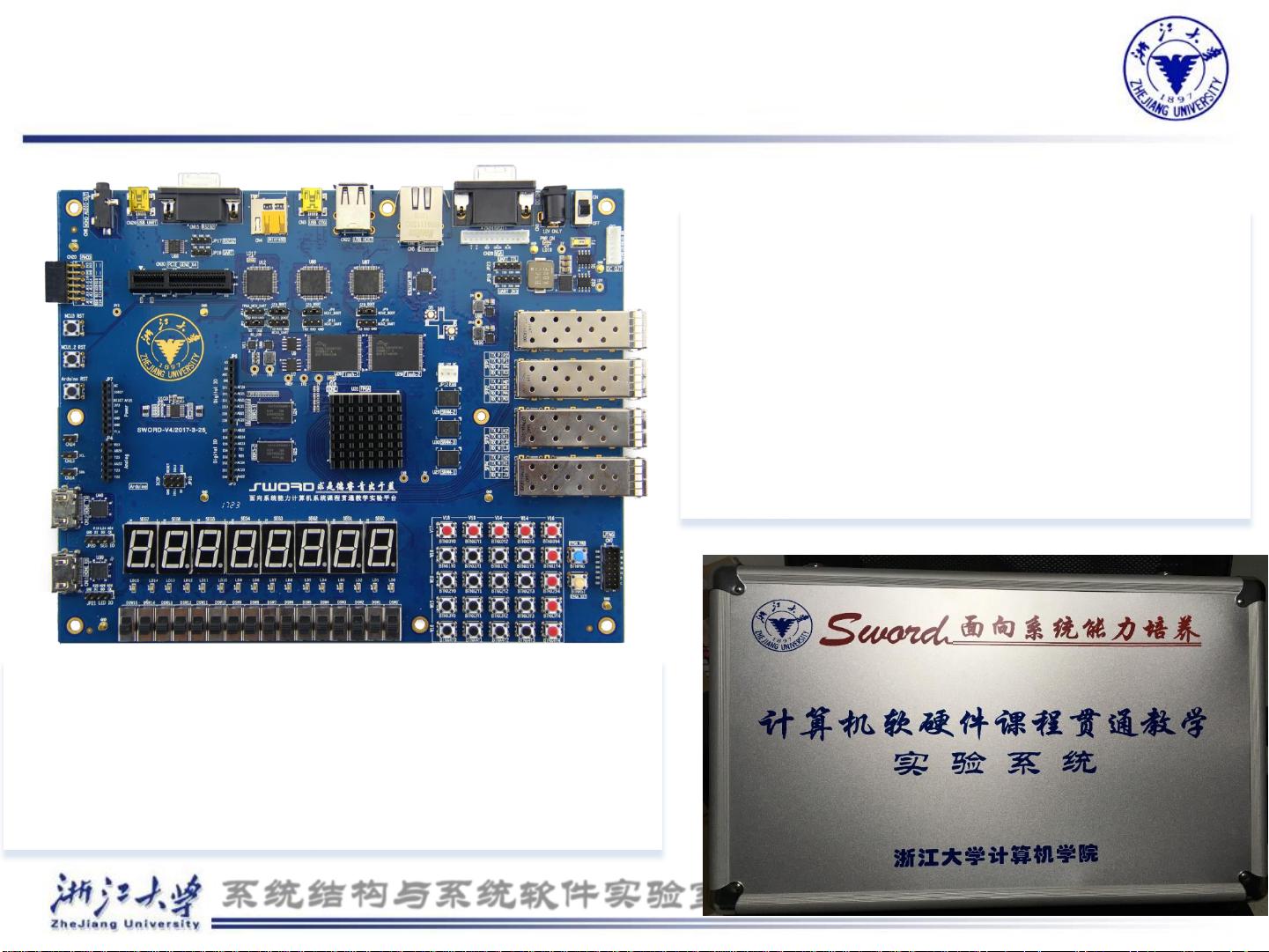

实验环境包括配备Intel Core i5以上处理器和4GB以上内存的计算机,以及计算机软硬件课程贯通教学实验系统SWORD4.0,该系统基于Xilinx ISE14.7及以上版本的开发工具。实验平台的核心是Xilinx Kintex™-7系列的XC7K325 FPGA,它提供了丰富的硬件资源,如 Slice、片内存储和各种接口,支持复杂的数字逻辑设计。

实验目的是让学生掌握同步时序电路的工作原理和设计方法,理解有限状态机的描述和电路实现,学习如何用状态图、状态方程和触发器激励函数来描述时序电路,并通过FPGA实现有限状态机的设计、仿真和调试。实验设备还包括用于输入输出的硬件接口,如矩阵按键、滑动开关、LED和七段数码管等,便于学生进行实际操作。

实验任务分为三个部分:

1. 基于状态方程,设计一个4位二进制同步计数器,使用原理图进行实现。

2. 使用HDL行为描述设计一个32位同步二进制双向计数器,这要求学生熟悉高级抽象的硬件描述语言,如Verilog或VHDL。

3. 将设计的计数器集成到实验环境中,如混合计算器(Calculation)。

对于4位同步二进制计数器,其状态表描述了当前状态(现态)和下一个状态(次态),以及触发器的输入激励(Qn+1A, Qn+1B, Qn+1C, Qn+1D)。状态变化由计数触发,无外部输入,输入方程需满足次态的输入要求。状态分配和触发器选择直接影响计数器的功能。例如,这里选择了D触发器,因为它们在同步时序电路中广泛使用,能确保在时钟边沿稳定地转移状态。

在状态方程中,可以计算每个触发器的输出,例如Qn+1A的输出函数可以通过状态真值表构建卡诺图并简化,得到触发器的激励函数。同样,其他触发器的输出也可以通过类似方法得出,从而完成整个计数器的设计。

这个实验通过理论与实践相结合的方式,让学生深入理解同步时序电路的工作原理和设计流程,提高他们的硬件设计和实现能力。同时,使用FPGA进行实时验证和调试,有助于增强学生的工程实践能力。

马克love

- 粉丝: 40

- 资源: 319

最新资源

- 课堂考勤微信小程序ssm-微信小程序毕业项目,适合计算机毕-设、实训项目、大作业学习.rar

- 考研论坛设计+ssm-微信小程序毕业项目,适合计算机毕-设、实训项目、大作业学习.rar

- 基于微信小程序的医院体检管理系统+ssm-微信小程序毕业项目,适合计算机毕-设、实训项目、大作业学习.rar

- 民大食堂用餐综合服务平台+ssm-微信小程序毕业项目,适合计算机毕-设、实训项目、大作业学习.rar

- 基于微信小程序的医院综合服务平台的设计与实现ssm-微信小程序毕业项目,适合计算机毕-设、实训项目、大作业学习.rar

- 旅游社交小程序+ssm-微信小程序毕业项目,适合计算机毕-设、实训项目、大作业学习.rar

- 马拉松报名系统微信小程序+ssm-微信小程序毕业项目,适合计算机毕-设、实训项目、大作业学习.rar

- 基于微信小程序的医院挂号预约系统ssm-微信小程序毕业项目,适合计算机毕-设、实训项目、大作业学习.rar

- 明星应援系统设计与实现+ssm-微信小程序毕业项目,适合计算机毕-设、实训项目、大作业学习.rar

- 基于深度学习的图像识别系统的研究与实现-构建高效CNN模型及其应用

- 基于微信小程序的在线学习系统springboot-微信小程序毕业项目,适合计算机毕-设、实训项目、大作业学习.rar

- 南宁周边乡村游微信小程序+ssm-微信小程序毕业项目,适合计算机毕-设、实训项目、大作业学习.rar

- 基于微信小程序的游泳馆管理系统--论文-微信小程序毕业项目,适合计算机毕-设、实训项目、大作业学习.zip

- 基于微信小程序的在线点餐(堂食)平台的设计与实现ssm-微信小程序毕业项目,适合计算机毕-设、实训项目、大作业学习.rar

- 模拟考试+ssm-微信小程序毕业项目,适合计算机毕-设、实训项目、大作业学习.rar

- 汽车预约维修系统+ssm-微信小程序毕业项目,适合计算机毕-设、实训项目、大作业学习.rar