没有合适的资源?快使用搜索试试~ 我知道了~

电子线路基础数字电路实验7 时序逻辑电路设计.docx

1.该资源内容由用户上传,如若侵权请联系客服进行举报

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

版权申诉

0 下载量 108 浏览量

2022-06-16

08:59:45

上传

评论

收藏 443KB DOCX 举报

温馨提示

试读

8页

电子线路基础数字电路实验7 时序逻辑电路设计.docx电子线路基础数字电路实验7 时序逻辑电路设计.docx电子线路基础数字电路实验7 时序逻辑电路设计.docx电子线路基础数字电路实验7 时序逻辑电路设计.docx电子线路基础数字电路实验7 时序逻辑电路设计.docx电子线路基础数字电路实验7 时序逻辑电路设计.docx电子线路基础数字电路实验7 时序逻辑电路设计.docx电子线路基础数字电路实验7 时序逻辑电路设计.docx电子线路基础数字电路实验7 时序逻辑电路设计.docx

资源推荐

资源详情

资源评论

实验七 时序逻辑电路设计

一、实验目的

1. 学习用集成触发器构成计数器的方法。

2. 熟悉中规模集成十进制计数器的逻辑功能及使用方法。

3. 学习计数器的功能扩展。

4. 了解集成译码器及显示器的应用。

二、实验原理

计数器是一种重要的时序逻辑电路,它不仅可以计数,而且用作定时控制

及进行数字运算等。按计数功能计数器可分加法、减法和可逆计数器,根据计数

体制可分为二进制和任意进制计数器,而任意进制计数器中常用的是十进制计数

器。根据计数脉冲引入的方式又有同步和异步计数器之分。

1. 用 D 触发器构成异步二进制加法计数器和减法计数器:

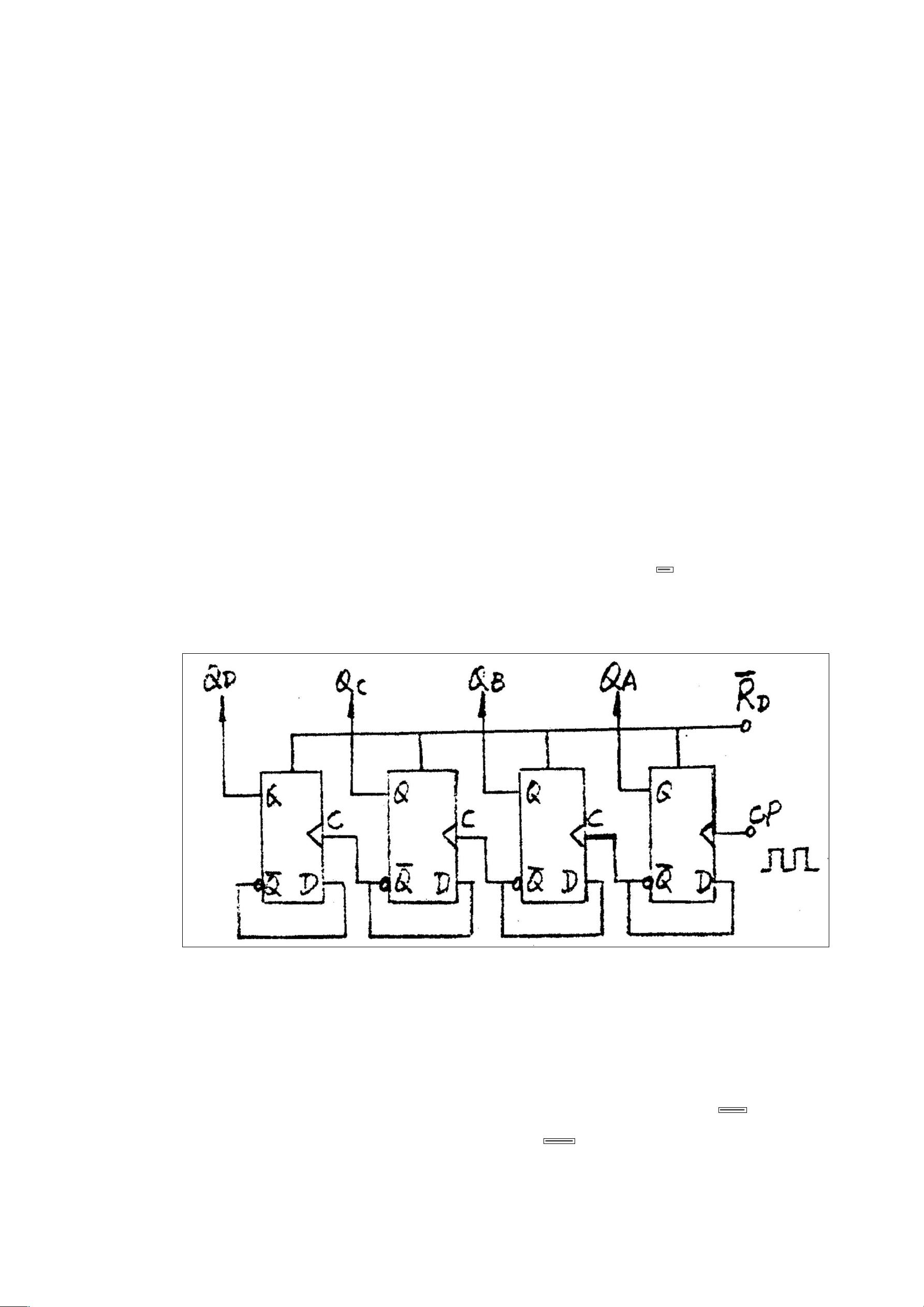

图 10—1 是用四只 D 触发器构成的四位二进制异步加法计数器,它的连接

特点是将每只 D 触发器接成 T触发器形式,再由低位触发器的

Q

端和高一位的

CP 端相连接,即构成异步计数方式。若把图 10—1 稍加改动,即将低位触发器

的 Q 端和高一位的 CP 端相连接,即构成了减法计数器。

图 10—1

本实验采用的 D 触发器型号为 74LS74A,引脚排列见前述实验。

2. 中规模十进制计数器

中规模集成计数器品种多,功能完善,通常具有予置、保持、计数等多种

功能。74LS182 同步十进制可逆计数器具有双时钟输入,可以执行十进制加法和

减法计数,并具有清除、置数等功能。引脚排列如图 10—2 所示。其中

LD

置数端;CP 加计数端;CP 减计数端;

非同步进位输出端;

DO

u D

资源评论

不吃鸳鸯锅

- 粉丝: 8225

- 资源: 2万+

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功