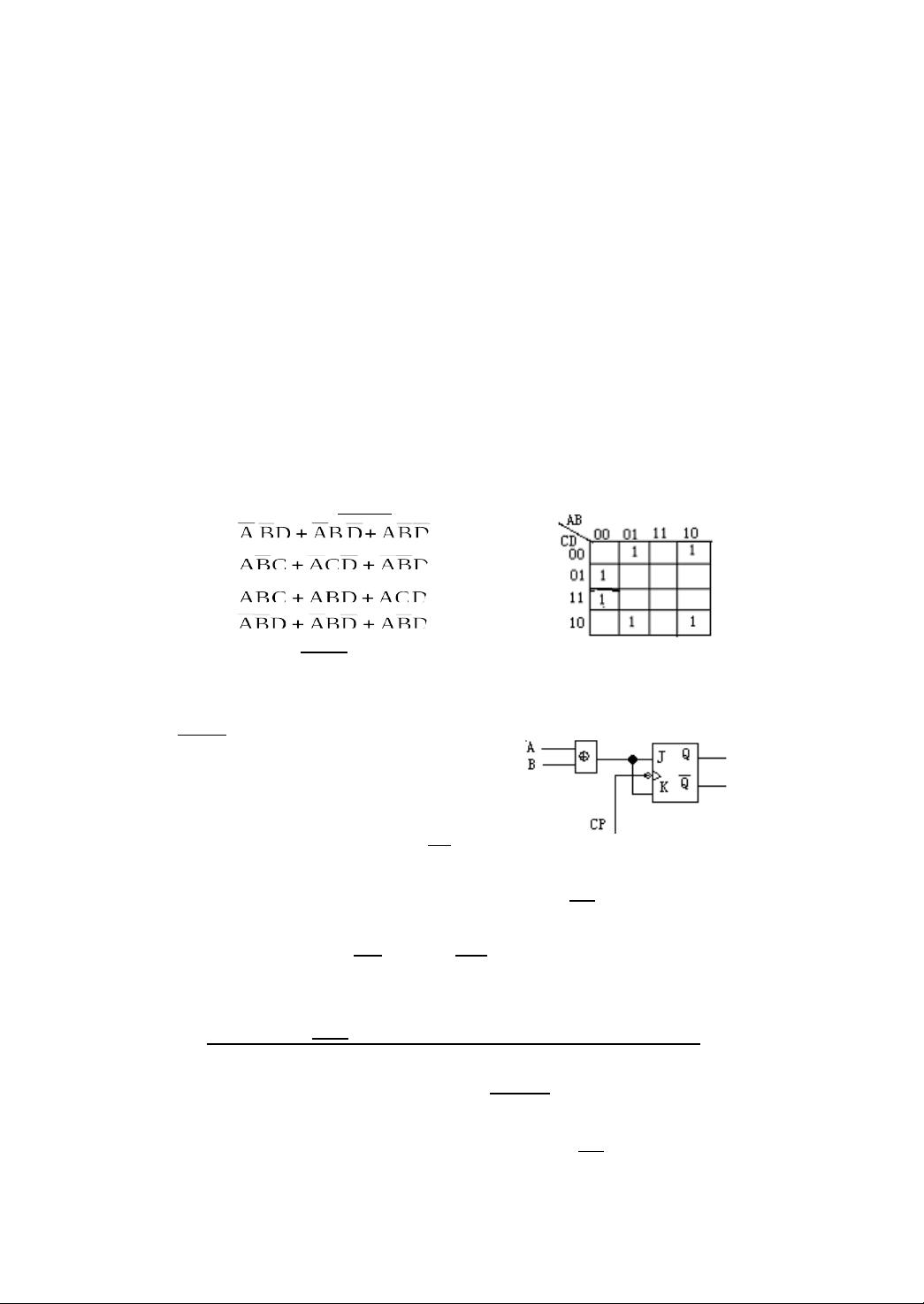

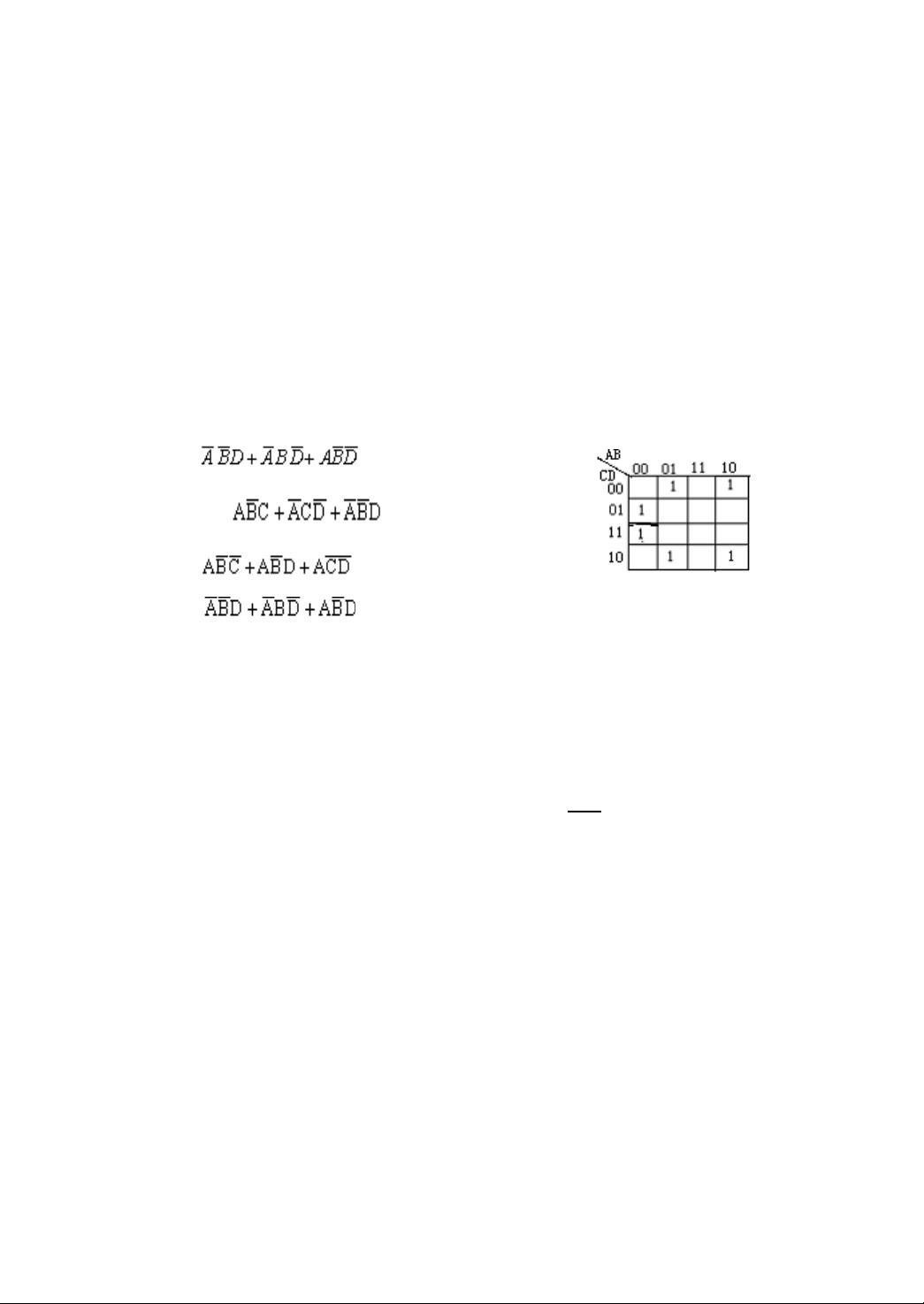

### 数字电路综合实验知识点解析 #### 一、选择题解析 **1. 若ABCDEFGH为最小项,则它有逻辑相邻项个数为(A)** **解析:** 最小项通常指的是在一个布尔函数中,由所有变量以某种形式(原变量或反变量)组成的与项。对于一个具有n个变量的最小项,它将有n个逻辑相邻项。这是因为每个变量都有两种状态(0或1),改变其中任何一个变量的状态都会导致一个新的相邻最小项。因此,对于ABCDEFGH这样一个包含8个变量的最小项来说,它会有8个逻辑相邻项。 **2. 如果编码0100表示十进制数4,则此码不可能是(B)** **解析:** BCD(Binary-Coded Decimal)码是一种用来表示十进制数的二进制编码方式。选项中提到的几种BCD码都是常见的BCD编码方法。8421BCD码是最常用的BCD码之一,它可以直接通过二进制位来表示十进制数,比如0100代表的就是4。而5211BCD码是一种不常用的BCD编码方式,它的每一位分别代表5、2、1、1这四个权重值,所以0100无法表示4,因为这四个权重值的组合无法表示出4这个十进制数。其他选项中,2421BCD码和余3循环码都可以表示4。 **3. 构成移位寄存器不能采用的触发器为(D)** **解析:** 移位寄存器是一种特殊的存储电路,能够将数据逐位地从一个触发器转移到另一个触发器。它可以采用R-S型、J-K型或主从型触发器来构建,但同步型触发器并不适用于直接构建移位寄存器,因为它没有明确的时钟控制信号来控制数据的移动。 **5. 以下PLD中,与、或阵列均可编程的是(C)器件。** **解析:** PLD(Programmable Logic Device)是可编程逻辑器件的总称,包括PROM(Programmable Read-Only Memory)、PAL(Programmable Array Logic)、PLA(Programmable Logic Array)和GAL(Generic Array Logic)等。在这几种PLD中,只有PLA的与阵列和或阵列都是可编程的,而其他类型的PLD要么只允许编程与阵列(PROM),要么只允许编程或阵列(PAL)。 **6. 函数F(A,B,C,D)=∑m(1,3,4,6,8,10),它的卡诺图如右图所示。函数的最简与或表达式F=A。** **解析:** 卡诺图是用来简化布尔函数的一种图形化工具。题目中给出了函数F的minterms(最小项)为1,3,4,6,8,10,根据这些信息绘制卡诺图,并简化得到最简与或表达式。这里提供的信息不足以确定具体的卡诺图和最简表达式,但一般来说,这样的过程会涉及到对卡诺图的分组,以找出最简表达式。 **7. 组合电路是指B组合而成的电路。** **解析:** 组合电路是由门电路(例如与门、或门、非门等)组合而成的电路,它没有记忆功能,输出完全取决于当前的输入状态。因此,正确答案是门电路。 **8. 电路如右图所示,经CP脉冲作用后,欲使Qn+1=Q,则A,B输入应为AB。** **解析:** 这类题目主要考察的是基本触发器的工作原理。为了使得Qn+1等于Q,即保持当前状态不变,通常需要特定的输入组合。根据题目描述,无法直接给出具体的输入组合,但一般情况下,这可能涉及到特定类型的触发器及其工作模式。 **9. 一位十进制计数器至少需要4个触发器。** **解析:** 一个十进制计数器需要能够表示从0到9共10个状态。使用二进制编码表示这10个状态,至少需要4个触发器(因为2^3=8小于10,而2^4=16大于10)。 **10. n个触发器构成的扭环计数器中,无效状态有D个。** **解析:** 扭环计数器是一种特殊的计数器,它可以使用较少的触发器实现较大的计数范围。对于n个触发器构成的扭环计数器,有效状态数为2^n - n,因为有n个状态是冗余的(即无效状态)。因此,无效状态的数量为2^n - (2^n - n) = n个。 **11. GAL器件的与阵列,或阵列D。** **解析:** GAL是一种可编程逻辑器件,它允许用户编程与阵列和或阵列中的某些部分。对于GAL而言,与阵列和或阵列都是可编程的,因此正确答案是“可编程,可编程”。 **12. 下列器件中是C现场片。** **解析:** EPROM(Erasable Programmable Read-Only Memory)是一种可以被多次擦写的只读存储器,属于现场可编程器件之一。触发器、计数器和加法器不是现场可编程器件。 **13. IspLSI器件中,缩写字母GLB是指B。** **解析:** 在IspLSI(isolated programming LSI)器件中,GLB(General Logic Block)是指通用逻辑块,它是IspLSI器件中的一个重要组成部分,用于实现复杂的逻辑功能。 **14. 在下列逻辑部件中,不属于组合逻辑部件的是D。** **解析:** 寄存器通常用于存储数据,具有记忆功能,因此不属于组合逻辑部件。译码器、编码器和全加器都是典型的组合逻辑部件。 **15. 八路数据选择器,其地址输入端(选择控制端)有C个。** **解析:** 一个八路数据选择器通常有3个地址输入端,因为2^3=8,可以控制8种不同的输入路径。 **17. 用n个触发器构成计数器,可得到最大计数模是C。** **解析:** 使用n个触发器构成的计数器的最大计数模为2^n。这是因为n个触发器可以表示2^n个不同的状态。 **18. [pic]C** **解析:** 图像题目无法直接解析,但是这类题目通常涉及到布尔代数的计算或者逻辑表达式的化简。 **19. 或非门构成的基本RS触发器,输入端SR的约束条件是(AC)。** **解析:** 对于由或非门构成的基本RS触发器,输入端S和R之间存在约束条件,即不允许同时输入高电平(1),即SR不能同时为1,因此约束条件为SR=0。 **21. 在CP作用下,欲使D触发器具有Qn+1=[pic]的功能,其D端应接(D)。** **解析:** D触发器的功能是在时钟脉冲的作用下,输出Qn+1等于输入D。为了满足题目中所描述的功能,D端应该连接到适当的逻辑表达式。 **22. 比较两个两位二进制数A=A1A0和B=B1B0,当A>B时输出F=1,则F的表达式是(C)。** **解析:** 比较两个二进制数的大小可以通过比较最高位开始,然后依次向下比较。如果最高位不同,则最高位大的那个数较大;如果最高位相同,则比较次高位。具体到这个题目中,A1和B1分别是A和B的最高位,因此F的表达式应考虑A1和B1之间的关系以及它们是否相等。 **23. 下列电路中属于数字电路的是(D)。** **解析:** 数字电路是指那些处理离散信号(通常是二进制信号)的电路。差动放大电路、集成运放电路和RC振荡电路都属于模拟电路,而逻辑运算电路则是数字电路的一部分。 **24. 表示任意两位十进制数,需要(B)位二进制数。** **解析:** 两位十进制数的最大值为99,使用二进制表示时,需要7位二进制数(2^7=128大于99)。 **25. n个变量可以构成(C)个最大项或最小项。** **解析:** 对于n个变量,可以构成2^n个最大项或最小项,因为每个变量都有两种状态(0或1),所有可能的组合共有2^n种。 **26. 组合逻辑电路中的险象是由于(C)引起的。** **解析:** 组合逻辑电路中的险象通常是由于信号传输路径中的时延差异造成的。当两个输入信号在时间上非常接近时,可能会导致输出信号出现瞬时的错误状态。 **27. 实现同一功能的Mealy型同步时序电路比Moore型同步时序电路所需要的(D)。** **解析:** Mealy型同步时序电路的输出不仅取决于当前状态,还取决于输入信号。因此,相比于仅依赖当前状态输出的Moore型电路,Mealy型电路通常需要更少的状态数和触发器数量来实现相同的逻辑功能。 **28. 用0011表示十进制数2,则此码为(D)。** **解析:** 根据题目描述,0011表示十进制数2。这个编码方式不是常用的BCD码或者其他编码方式,而是格雷码(Gray Code)的一种特殊情况,因为在格雷码中,连续数值之间的二进制表示只有一位发生变化。 **31. 函数F(A,B,C,D)=∑m(1,3,4,6,8,10),它的卡诺图如右图所示。函数的最简与或表达式F=(A)。** **解析:** 这个题目要求求出给定函数的最简与或表达式。根据给出的minterms列表,绘制卡诺图并进行简化。由于题目中没有提供具体的卡诺图,因此无法给出具体的解析过程。 **32. 组合电路是指(B)组合而成的电路。** **解析:** 同解析7。 **33. 八路数据分配器,其地址输入(选择控制)端有(C)个。** **解析:** 同解析15。 **34. 555定时器构成的单稳态触发器输出脉宽tw为。** **解析:** 555定时器构成的单稳态触发器的输出脉宽tw通常由外部电阻R和电容C决定,具体的公式为tw ≈ 1.1RC。 **35. 下列触发器中,有约束条件的是(C)。** **解析:** R-S触发器和JK触发器通常没有特定的约束条件。D触发器有一个约束条件,即在时钟边沿到来之前,输入D必须稳定。因此,正确答案是D触发器。 **36. 实现两个四位二进制数相乘的组合电路,应有(B)个输出函数。** **解析:** 两个四位二进制数相乘的结果是一个8位的二进制数。因此,需要8个输出函数来表示乘积的每一位。 **37. 组合逻辑电路中的险象是由于(C)引起的。** **解析:** 同解析26。 **38. 实现同一功能的Mealy型同步时序电路比Moore型同步时序电路所需要的(D)。** **解析:** 同解析27。 **39. 用0011表示十进制数2,则此码为(D)。** **解析:** 同解析28。 **40. 标准与或式是由(B)构成的逻辑表达式。** **解析:** 标准与或式是由最小项相或构成的逻辑表达式。 **41. J-K触发器在CP时钟脉冲作用下,要使得Q(n+1)=Qn,则输入信号必定不会** **解析:** J-K触发器在时钟脉冲CP的作用下,若要使得输出Q(n+1)等于当前状态Qn,则输入J和K应当为0,这样无论CP脉冲上升沿还是下降沿到来时,触发器的状态都不会改变。因此,输入信号J和K必定不会同时为1。

剩余21页未读,继续阅读

- 粉丝: 0

- 资源: 1

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 自动送餐设备sw16可编辑全套技术资料100%好用.zip

- 自动丝印链板线(sw19可编辑+工程图)全套技术资料100%好用.zip

- Meterpreter框架下常见命令及其应用详解

- 自行车立体车库 sw16全套技术资料100%好用.zip

- 自动贴胶带贴膜产线sw17可编辑全套技术资料100%好用.zip

- 多功能集成工具 SpiritTools 2.0.1 版本功能更新与优化

- 自动纸板捆扎机1.5米sw16可编辑全套技术资料100%好用.zip

- python脚本-生成MySQL数据字典

- enhanced chop melons and vegetables-啊哦111

- 字符串-圣诞树c++语言编程代码

- christmasTree-圣诞树html网页代码

- 数据结构与算法 -二叉树的深度

- shell-scripts-python圣诞树

- chdthesis-学术规范与论文写作

- Java-Interview-Advanced-啊哦111

- iot-iita-http

信息提交成功

信息提交成功