如果你是肥大学子,在做verilog课程设计,不用再看了,这就是你需要的!

此版本word内部为程序的截屏,程序需要自己敲进电脑。若不想自己敲代码,清下载我上传的另一版本。

功能描述:此数字跑表由三个按键控制,按键功能如下:

SW1:实现暂停、开始以及数据的保存

SW2:实现清零

SW3:实现已保存数据的显示

在电子设计自动化(EDA)领域,Verilog 是一种广泛应用的硬件描述语言,用于设计和验证数字系统的逻辑。本文将深入探讨如何使用Verilog实现一个数字跑表,这通常是一个常见的课程设计项目,对于学习者来说,它能很好地展示Verilog的基础知识和实际应用。

我们来理解数字跑表的基本功能。根据描述,这个数字跑表由三个按键(SW1, SW2, SW3)控制,每个按键都有特定的功能:

- SW1:暂停/开始计时并保存数据。这需要实现一个状态机来控制跑表的运行状态,例如,当按下SW1时,状态机可以从运行状态切换到暂停状态,再次按下则恢复计时。同时,为了保存数据,可能需要一个存储单元来保存当前的时间值。

- SW2:清零功能。按下SW2时,跑表计数值应重置为零,这可以通过对计数器清零实现。

- SW3:显示已保存数据。当按下SW3时,跑表应显示之前保存的时间,而不是当前的实时时间,这可能需要额外的逻辑来控制LED显示。

在Verilog中,跑表的设计通常包括以下几个部分:

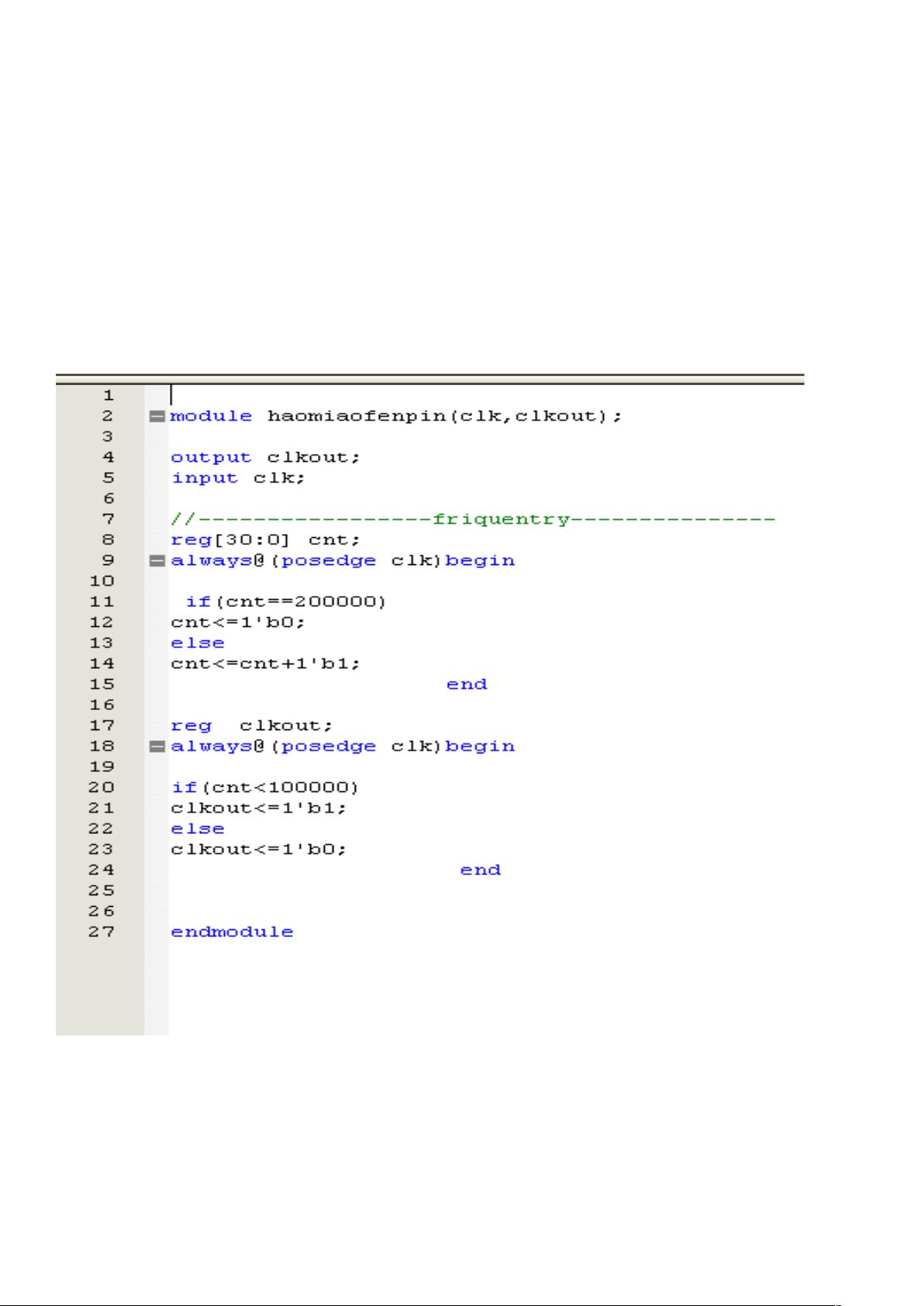

1. **毫秒分频器**:这是跑表的心脏,用于生成精确的时间单位。通常,一个分频器会将系统时钟(如50MHz)分频得到毫秒级别的时钟。这可以通过一个计数器和比较器实现,当达到预设值时产生一个新的毫秒信号。

2. **消抖程序**:由于机械按键会有抖动,为了确保稳定的操作,需要加入消抖电路。这通常是一个简单的延时电路,通过在一段时间内检测按键是否持续被按下来避免误触发。

3. **状态机**:实现SW1的功能,需要一个状态机来管理跑表的运行、暂停和数据保存。状态机的状态可以包括`IDLE`(等待开始),`RUNNING`(计时中),`PAUSED`(暂停),和`SAVE`(保存数据)等。

4. **计数器**:计数器负责记录时间,每次收到毫秒级时钟脉冲时加一。在暂停状态下,计数器不再增加。

5. **LED控制**:这部分逻辑决定哪些LED应该亮起以显示时间。可以使用位移寄存器和选择器来实现,或者更高级的方法如查表法(ROM)。

6. **存储器**:为了保存数据,可以使用一个寄存器或RAM单元来存储暂停时的时间值。当SW1被按下的特定条件下,数据会被写入存储器。

7. **显示控制**:这部分逻辑响应SW3的输入,选择显示实时计时还是已保存的计时数据。

实现这些功能需要理解Verilog的基本语法,如模块定义、输入/输出端口、赋值操作符(如`<=`)、条件语句(如`if-else`)、循环结构(如`always`块)、组合逻辑和时序逻辑等。在实际编码过程中,还需要考虑仿真测试,以确保跑表在各种输入条件下的正确行为。

设计一个Verilog数字跑表是一项涵盖状态机设计、计数器、存储器操作、信号处理等多个核心概念的实践任务,对于理解和掌握Verilog编程技巧具有很大的帮助。通过这样的项目,学生不仅能学习到硬件描述语言的基本用法,还能了解数字系统的实际工作原理。