基于FPGA的数字钟设计报告

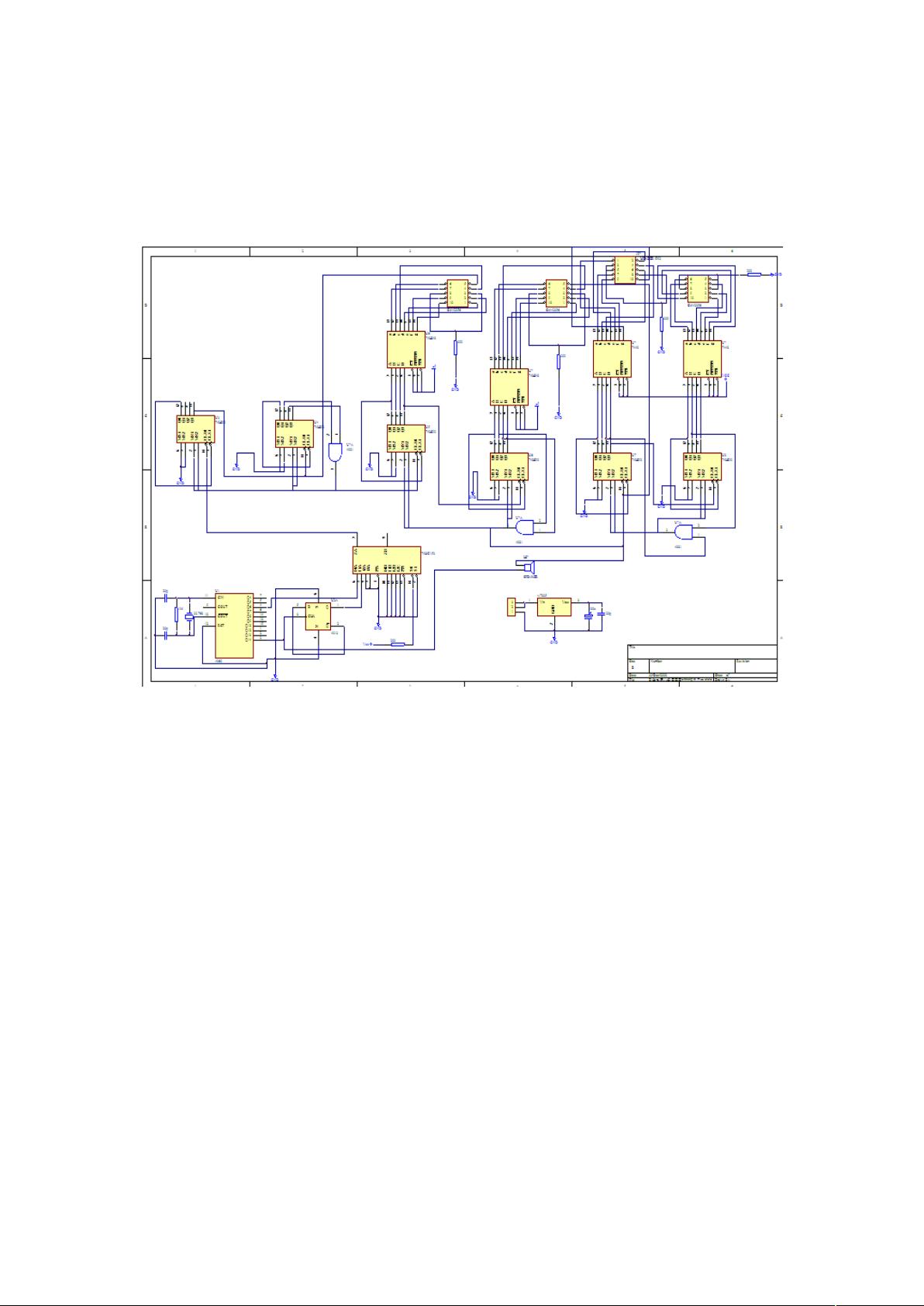

EDA技术在电子系统设计领域越来越普及,本设计主要利用VHDL语言在EDA平台上设计一个电子数字钟,它的计时周期为24小时,显示满刻度为23时59分59秒,另外还具有校时功能和闹钟功能。总的程序由几个各具不同功能的单元模块程序拼接而成,其中包括分频程序模块、时分秒计数和设置程序模块、比较器程序模块、三输入数据选择器程序模块、译码显示程序模块和拼接程序模块。并且使用QuartusII软件进行电路波形仿真,下载到EDA实验箱进行验证。该设计采用自顶向下、混合输入方式(原理图输入—顶层文件连接和VHDL语言输入—各模块程序设计)实现数字钟的设计、下载和调试。 《基于FPGA的数字钟设计报告》是一篇关于利用EDA技术设计数字钟的详细报告,主要涉及FPGA芯片和VHDL语言的应用。设计的目标是一个24小时计时周期的电子数字钟,具备完整的计时、校时以及闹钟功能。报告详细阐述了设计过程中的各个步骤和技术要点。 设计要求明确,包括基本功能和发挥部分。基本功能要求数字钟能够每秒计时,并在显示屏上实时显示时间,同时具备手动校准小时和分钟的时间设置功能。发挥部分则增加了计时进制的选择(12小时或24小时制)、整点报警以及可能的其他创新功能。 在总体设计方案中,报告提到了几种不同的方案。方案一利用74LS90数码管译码电路,以32768Hz的晶体振荡器为核心,通过分频器(如CD4060)将高频信号转换为1Hz的秒信号。这种方案通常采用多级二进制计数器来实现所需的分频倍数,以满足设计需求。 在设计思路上,报告采用了自顶向下的设计方法,结合原理图输入和VHDL语言编程。VHDL语言被用来编写各个功能模块的程序,如分频程序模块、时分秒计数和设置程序模块、比较器程序模块、三输入数据选择器程序模块、译码显示程序模块以及拼接程序模块。这些模块共同构建了整个数字钟系统。 在硬件电路部分,报告虽然没有详述,但可以理解,数字钟通常包括时钟信号源(如晶体振荡器)、分频器、计数器、比较器(用于校时和闹钟触发)、数据选择器(用于处理不同信号)以及译码器(用于驱动显示器)。所有这些组件通过VHDL代码实现逻辑功能,并在EDA平台上进行仿真验证。 在软件模块部分,QuartusII软件被用来进行电路波形仿真,这是Altera公司的FPGA开发工具,它支持VHDL语言,可以对设计进行逻辑综合、时序分析和功能仿真,最终将设计下载到FPGA实验板上进行实际操作和测试。 报告最后总结了设计过程中的心得体会,强调了EDA技术的重要性以及在实际项目中的应用。同时,参考文献提供了进一步学习的资源。 基于FPGA的数字钟设计融合了硬件描述语言VHDL、分频技术、计数器逻辑、时序控制以及EDA工具的使用,充分展示了现代电子设计的流程和技术。通过这样的设计实践,学生不仅可以掌握电子设计的基本思路和方法,还能提升在FPGA领域的专业知识和动手能力。

剩余22页未读,继续阅读

溪流扬2013-06-04很多图整死我想要的,非常好

溪流扬2013-06-04很多图整死我想要的,非常好 linjm212013-03-19毕业设计值得借鉴。内容齐全,图表清晰

linjm212013-03-19毕业设计值得借鉴。内容齐全,图表清晰 laviequev2013-06-17还可以,文字略少

laviequev2013-06-17还可以,文字略少

- 粉丝: 5

- 资源: 19

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功