没有合适的资源?快使用搜索试试~ 我知道了~

资源推荐

资源详情

资源评论

JESD204 v6.0

LogiCORE IP Product Guide

Vivado Design Suite

PG066 October 1, 2014

JESD204 v6.0 www.xilinx.com 2

PG066 October 1, 2014

Table of Contents

IP Facts

Chapter 1: Overview

Transmitter. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

Receiver . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Core Level Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Unsupported Features. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Licensing and Ordering Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Chapter 2: Product Specification

Standards . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Resource Utilization. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Port Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Register Space . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Chapter 3: Designing with the Core

General Design Guidelines . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Core Overview and Getting Started . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Clocking. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

Resets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

Interfacing to the AXI4-Stream Data Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

AXI4-Lite Management Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

Subclass 1 Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

Subclass 2 Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

JESD204B Receiver . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

JESD204B Transmitter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

Link Test Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

Sharing Transceivers between Transmit and Receive . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

Chapter 4: Design Flow Steps

Customizing and Generating the Core . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

Constraining the Core . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

Send Feedback

JESD204 v6.0 www.xilinx.com 3

PG066 October 1, 2014

Simulation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

Synthesis and Implementation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

Chapter 5: Detailed Example Design

Common Design Elements. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

Chapter 6: Test Bench

Appendix A: Verification, Compliance, and Interoperability

Simulation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

Hardware Testing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

Appendix B: Hardware Demonstration Design

Appendix C: Migrating and Upgrading

Migrating to the Vivado Design Suite. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

Upgrading in the Vivado Design Suite . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

Appendix D: Debugging

Finding Help on Xilinx.com . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110

Debug Tools . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 112

Simulation Debug. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

Hardware Debug . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 114

Interface Debug . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 115

Appendix E: Additional Resources and Legal Notices

Xilinx Resources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 116

References . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 116

Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 117

Please Read: Important Legal Notices . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 118

Send Feedback

JESD204 v6.0 www.xilinx.com 4

PG066 October 1, 2014 Product Specification

Introduction

The Xilinx® LogiCORE™ IP JESD204 core

implements a JESD204B interface supporting

line rates from 1 Gb/s to 12.5 Gb/s. The

JESD204 core can be configured as a

transmitter or receiver.

Features

• Designed to JEDEC® JESD204B [Ref 1]

• Supports 1 to 12 lane configurations

• Supports Initial Lane Alignment

• Supports scrambling

• Supports 1–256 octets per frame

(1)

• Supports 1–32 frames per multi frame

(1)

• Supports Subclass 0, 1 and 2

• Physical and Data Link Layer functions

provided

• AXI4-Lite configuration interface [Ref 2]

• AXI4-Stream data interface [Ref 3]

• Supports transceiver sharing between TX

and RX cores

1. The maximum supported multi frame size is 1000 octets

and the minimum is 20 octets.

IP Facts

LogiCORE IP Facts Table

Core Specifics

Supported

Device Family

(1)

UltraScale™ Architecture, Zynq®-7000 All

Programmable SoC, 7 Series

Supported User

Interfaces

AXI4-Stream, AXI4-Lite Control/Status

Resources See Ta ble 2-2.

Provided with Core

Design Files Encrypted RTL

Example Design Verilog

Test Bench Verilog

Constraints File XDC

Simulation

Model

Verilog

Supported

S/W Driver

N/A

Tested Design Flows

(2)

Design Entry

Vivado

® Design Suite

IP Integrator

Simulation

For supported simulators, see

the

Xilinx Design Tools: Release Notes Guide.

Synthesis Vivado Synthesis

Support

Provided by Xilinx @ www.xilinx.com/support

Notes:

1. For a complete listing of supported devices, see the Vivado IP

catalog.

2. For the supported versions of the tools, see the

X

ilinx Design Tools: Release Notes Guide.

Send Feedback

JESD204 v6.0 www.xilinx.com 5

PG066 October 1, 2014

Chapter 1

Overview

The LogiCORE™ IP JESD204 core implements a JESD204B interface supporting line rates of

between 1 and 12.5 Gb/s on 1 to 12 lanes using GTX, GTH or GTP transceivers. (See the

device data sheets for maximum line rates supported by each device and family.) The

JESD204 core can be configured as transmit or receive.

The JESD204 core is a fully-verified solution design delivered by using the Xilinx® Vivado®

Design Suite. In addition, an example design is provided in Verilog.

Transmitter

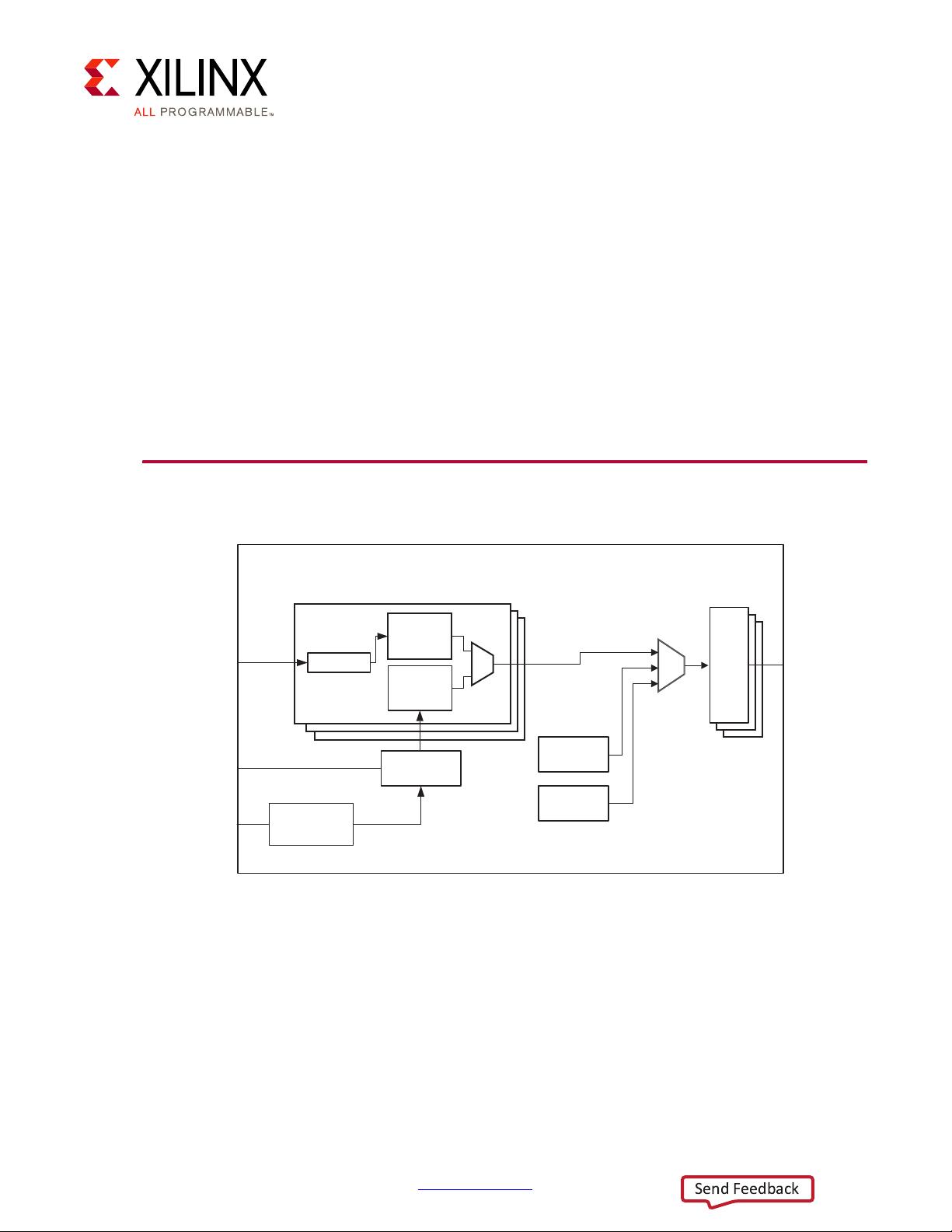

Figure 1-1 shows an overview block diagram for the transmitter of the JESD204 core. The

main blocks are:

• Single AXI4-Stream interface for all lanes

• TX lane logic, per lane, contains:

°

Scrambling

°

Alignment character insertion logic

°

Initial Lane Alignment (ILA) sequence generation

X-Ref Target - Figure 1-1

Figure 1-1: Transmitter Core Overview

7H[W

7H[W

6FUDPEOHU

$OLJQPHQW

&KDUDFWHU

*HQHUDWRU

/DQH

$OLJQPHQW

6HTXHQFH

7;&RXQWHUV

$;,/LWH,3,)

5HJLVWHUV

6\QF6<65()

$;,/LWH

&RQWURO

$;,6WUHDP

7[/DQHV

53$7

*HQHUDWRU

-63$7

*HQHUDWRU

*7;

*7+

*73

-(6'7UDQVPLWWHU&RUH

-(6'

6HULDO'DWD

Send Feedback

剩余117页未读,继续阅读

资源评论

遥远的停止线前

- 粉丝: 19

- 资源: 9

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 大学生智能消费记账系统的设计与实现-springboot毕业项目,适合计算机毕-设、实训项目、大作业学习.rar

- 个人博客系统的设计与实现-springboot毕业项目,适合计算机毕-设、实训项目、大作业学习.rar

- 洞见研报ZDEER左点(全场景科技医疗及健康生活解决方案服务商,左点健康产业(深圳)有限公司)创投信息

- javaweb的新能源充电系统pf-springboot毕业项目,适合计算机毕-设、实训项目、大作业学习.zip

- 基于Java的大学生考勤系统的设计与实现--论文pf-springboot毕业项目,适合计算机毕-设、实训项目、大作业学习.zip

- 基于Java Web的考编论坛网站的设计与实现pf-springboot毕业项目,适合计算机毕-设、实训项目、大作业学习.zip

- +vue校园求职招聘系统设计和实现pf-springboot毕业项目,适合计算机毕-设、实训项目、大作业学习.zip

- 地理信息系统考研复习笔记,助力上岸

- 洞见研报和府捞面(面食餐饮品牌,江苏和府餐饮管理有限公司)创投信息

- 基于html5+css3的在线英语阅读分级平台--论文pf-springboot毕业项目,适合计算机毕-设、实训项目、大作业学习.zip

- 交流互动系统(1)-springboot毕业项目,适合计算机毕-设、实训项目、大作业学习.zip

- 教师人事档案管理系统-springboot毕业项目,适合计算机毕-设、实训项目、大作业学习.zip

- 基于javaweb的宠物猫认养系统pf-springboot毕业项目,适合计算机毕-设、实训项目、大作业学习.zip

- 酒店管理系统-springboot毕业项目,适合计算机毕-设、实训项目、大作业学习.zip

- 基于javaweb的城乡居民基本医疗信息管理系统pf-springboot毕业项目,适合计算机毕-设、实训项目、大作业学习.zip

- arm64架构下gmssl工具

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功