VLSI可测性设计-冯建华课程 08-1

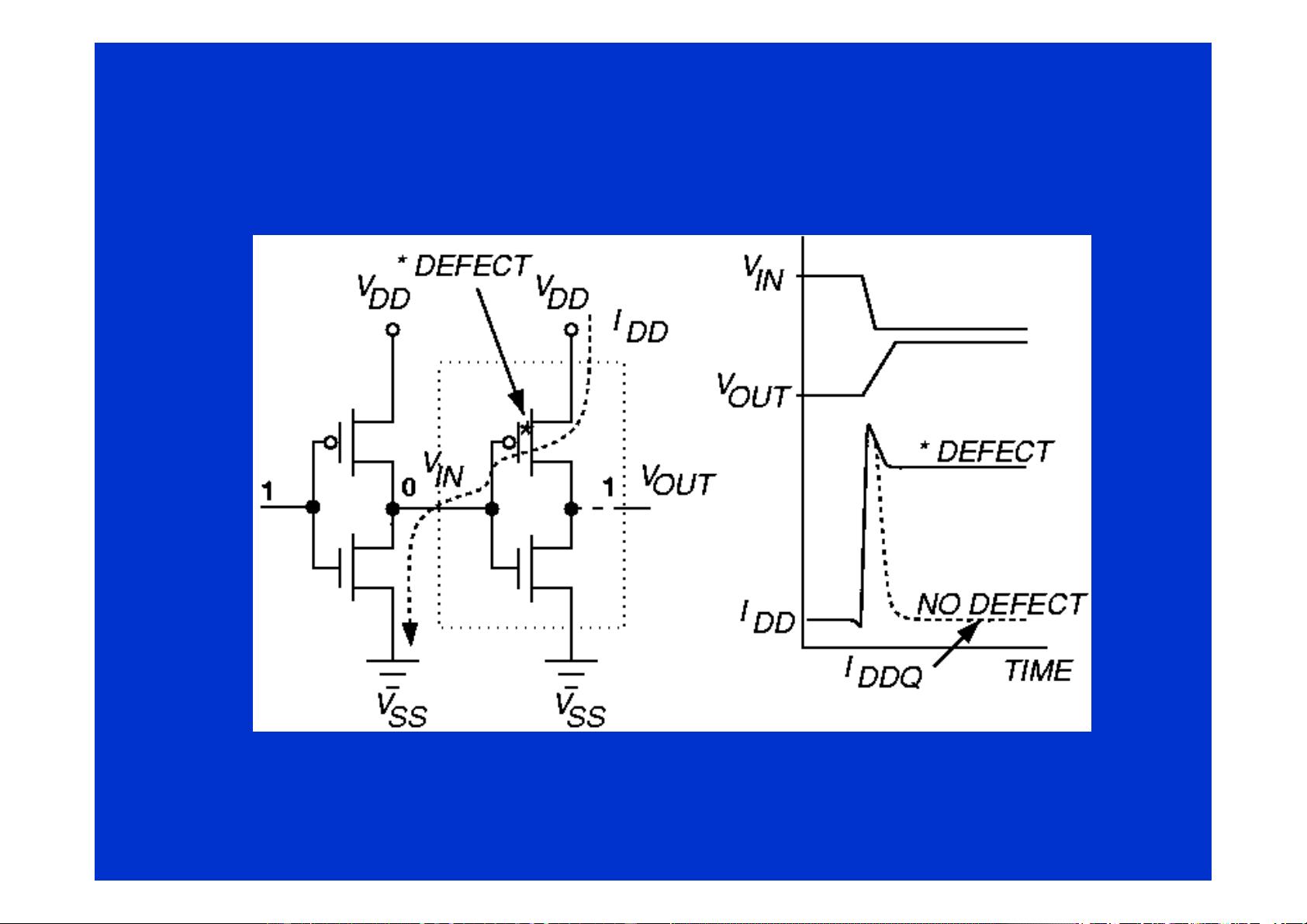

### VLSI可测性设计——IDDQ电流测试详解 #### 一、IDDQ电流测试概述 IDDQ电流测试是一种重要的集成电路(IC)测试技术,主要用于检测IC在静态(即不进行任何操作的情况下)时的电源电流是否异常。正常情况下,CMOS电路在静态条件下的电源电流应该非常低,几乎可以忽略不计。然而,一旦电路出现某些类型的故障,静态电流就会显著增加。因此,通过测量IDDQ电流的变化情况,可以有效检测出电路中存在的故障。 #### 二、IDDQ电流测试基本原理 IDDQ测试的基本原理在于利用Vss总线测量IDDQ电流。具体而言,在静态条件下,若电路内部存在故障,如桥接、短路或开路等,这些故障会导致电流泄露或者额外的电流路径形成,从而使得IDDQ电流增大。通过比较实际测量得到的IDDQ值与预期的理想值之间的差异,可以判断电路是否存在故障。 #### 三、IDDQ测试可检测的故障类型 IDDQ测试能够有效地检测多种类型的故障,包括但不限于以下几种: 1. **桥接故障**:当逻辑节点与VDD或VSS桥接时,可能会导致IDDQ电流异常升高。此外,晶体管栅氧化层短路也会引起类似问题。 2. **悬浮MOSFET栅缺陷**:这类故障使得晶体管无法完全截止,导致IDDQ电流增加。 3. **浮栅缺陷**: - 小开路(100-200Ω)会通过电子隧道效应耦合到其他线路,可能导致延迟故障和IDDQ故障。 - 大开路则可能形成固定故障,但若满足一定条件(如Vtn < Vfn < VDD - |Vtp|),仍可通过IDDQ测试检测。 4. **桥接故障**:完全短路(<50Ω)或较大的电阻(R > 50KΩ)引起的桥接故障均可通过IDDQ测试发现。 5. **CMOS晶体管常开故障(Stuck-Open)**:这类故障虽然较难检测,但在某些情况下IDDQ测试依然有效。 6. **延迟故障**:大多数随机CMOS缺陷都会导致时序延迟故障,IDDQ测试能够检测到其中的一部分。 7. **漏电故障**:栅氧化层短路引起的栅-源或栅-漏之间的漏电也可以通过IDDQ测试检测出来。 8. **弱故障**:当一个晶体管不能完全导通时,可能导致逻辑值衰减,这类故障也可以通过IDDQ测试识别。 #### 四、IDDQ测试的局限性 尽管IDDQ测试能够检测多种故障,但它也有一定的局限性。例如,对于某些类型的互连通孔电阻故障以及提高晶体管阈值电压的故障,IDDQ测试可能无法准确地检测出来。 #### 五、总结 IDDQ电流测试作为一种有效的集成电路测试手段,在检测静态条件下的各种故障方面发挥着重要作用。通过对IDDQ电流的精确测量和分析,可以及时发现并定位电路中的潜在问题,从而确保集成电路的可靠性和性能。随着集成电路设计的复杂度不断增加,IDDQ测试的重要性也在不断提升,成为了现代集成电路制造过程中不可或缺的一部分。

剩余31页未读,继续阅读

- 粉丝: 0

- 资源: 22

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功

评论0