PCI Bus Power Management

Interface Specification

Revision 1.2

March 3, 2004

PCI BUS POWER MANAGEMENT INTERFACE SPECIFICATION, REV. 1.2

2

Revision History

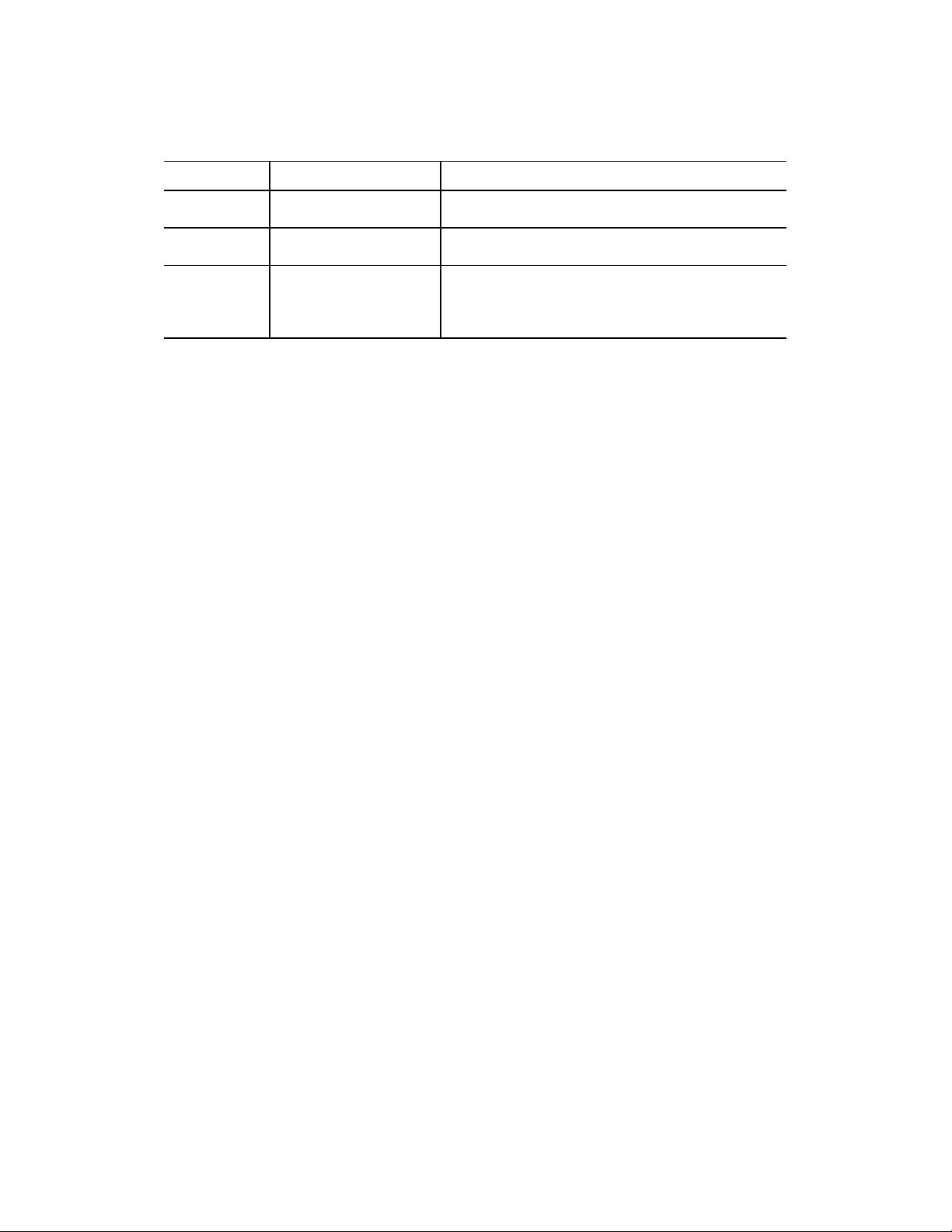

Revision Issue Date Comments

1.0 June 30, 1997 Original Issue.

1.1 December 18, 1998 Integrated the 3.3Vaux ECR.

1.2 March 3, 2004 Changed defined action for D3

hot

and clarified

bridge behavior when not in D0. Common

document template update.

PCI-SIG disclaims all warranties and liability for the use of this document and the information

contained herein and assumes no responsibility for any errors that may appear in this document, nor

does the PCI-SIG make a commitment to update the information contained herein.

Contact the PCI-SIG office to obtain the latest revision of the specification.

Questions regarding this specification or membership in PCI-SIG may be forwarded to:

Membership Services

www.pcisig.com

E-mail: administration@pcisig.com

Phone: 503-291-2569

Fax: 503-297-1090

Technical Support

techsupp@pcisig.com

DISCLAIMER

This PCI Bus Power Management Interface Specification is provided "as is" with no

warranties whatsoever, including any warranty of merchantability, noninfringement,

fitness for any particular purpose, or any warranty otherwise arising out of any proposal,

specification, or sample. PCI-SIG disclaims all liability for infringement of proprietary

rights, relating to use of information in this specification. No license, express or implied,

by estoppel or otherwise, to any intellectual property rights is granted herein.

PCI Express is a trademark of PCI-SIG.

All other product names are trademarks, registered trademarks, or service marks of their

respective owners.

Copyright © 1997, 1998, 2004 PCI-SIG

PCI BUS POWER MANAGEMENT INTERFACE SPECIFICATION, REV. 1.2

3

Contents

1. INTRODUCTION............................................................................................................... 7

1.1. G

OALS OF

T

HIS

S

PECIFICATION

...................................................................................... 7

1.2. T

ARGET

A

UDIENCE

........................................................................................................ 8

1.3. O

VERVIEW

/S

COPE

.......................................................................................................... 9

1.4. C

ONVENTIONS

U

SED IN

T

HIS

D

OCUMENT

..................................................................... 10

1.5. G

LOSSARY OF

T

ERMS

................................................................................................... 10

1.6. R

ELATED

D

OCUMENTS

................................................................................................. 15

2. PCI POWER MANAGEMENT OVERVIEW ............................................................... 17

2.1. PCI P

OWER

M

ANAGEMENT

S

TATES

............................................................................. 17

2.1.1. PCI Function Power States ................................................................................. 17

2.1.2. Bus Power States................................................................................................. 17

2.1.3. PCI Express Link Power States........................................................................... 17

2.1.4. Device-Class Specifications ................................................................................ 18

2.1.5. Bus Support for PCI Function Power Management ........................................... 19

3. PCI POWER MANAGEMENT INTERFACE .............................................................. 21

3.1. C

APABILITIES

L

IST

D

ATA

S

TRUCTURE

.......................................................................... 22

3.1.1. Capabilities List Cap_Ptr Location .................................................................... 23

3.2. P

OWER

M

ANAGEMENT

R

EGISTER

B

LOCK

D

EFINITION

.................................................. 24

3.2.1. Capability Identifier - Cap_ID (Offset = 0) ........................................................ 24

3.2.2. Next Item Pointer - Next_Item_Ptr (Offset = 1).................................................. 25

3.2.3. PMC - Power Management Capabilities (Offset = 2) ........................................ 25

3.2.4. PMCSR - Power Management Control/Status (Offset = 4) ................................ 27

3.2.5. PMCSR_BSE - PMCSR PCI-to-PCI Bridge Support Extensions (Offset = 6).... 30

3.2.6. Data (Offset = 7)................................................................................................. 31

4. PCI BUS POWER STATES............................................................................................. 35

4.1. PCI B0 S

TATE

- F

ULLY

O

N

.......................................................................................... 36

4.2. PCI B1 S

TATE

.............................................................................................................. 36

4.3. PCI B2 S

TATE

.............................................................................................................. 36

4.4. PCI B3 S

TATE

- O

FF

.................................................................................................... 37

4.5. PCI B

US

P

OWER

S

TATE

T

RANSITIONS

.......................................................................... 37

4.6. PCI C

LOCKING

C

ONSIDERATIONS

................................................................................ 38

4.6.1. Special Considerations for 66-MHz PCI Designs............................................... 38

4.7. C

ONTROL

/S

TATUS OF

PCI B

US

P

OWER

M

ANAGEMENT

S

TATES

................................... 39

4.7.1. Control of Secondary Bus Power Source and Clock........................................... 39

PCI BUS POWER MANAGEMENT INTERFACE SPECIFICATION, REV. 1.2

4

5. PCI FUNCTION POWER MANAGEMENT STATES ................................................ 41

5.1. PCI F

UNCTION

D0

S

TATE

............................................................................................. 41

5.2. PCI F

UNCTION

D1 S

TATE

............................................................................................ 41

5.3. PCI F

UNCTION

D2 S

TATE

............................................................................................ 42

5.4. PCI F

UNCTION

D3 S

TATE

............................................................................................ 42

5.4.1. Software Accessible D3 (D3

hot

)........................................................................... 43

5.4.2. Power Off (D3

cold

) ............................................................................................... 43

5.4.3. 3.3Vaux/D3

cold

Add-in Card Power Consumption Requirements ....................... 44

5.5. PCI F

UNCTION

P

OWER

S

TATE

T

RANSITIONS

................................................................ 45

5.6. PCI F

UNCTION

P

OWER

M

ANAGEMENT

P

OLICIES

.......................................................... 45

5.6.1. State Transition Recovery Time Requirements ................................................... 50

6. PCI BRIDGES AND POWER MANAGEMENT .......................................................... 53

6.1. H

OST

B

RIDGE OR

O

THER

S

YSTEM

B

OARD

E

NUMERATED

B

RIDGE

................................ 55

6.2. PCI-

TO

-PCI B

RIDGES

................................................................................................... 56

6.3. PCI-

TO

-C

ARD

B

US

B

RIDGE

........................................................................................... 56

7. POWER MANAGEMENT EVENTS.............................................................................. 57

7.1. P

OWER

M

ANAGEMENT

E

VENT

(PME#) S

IGNAL

R

OUTING

........................................... 60

7.2. A

UXILIARY

P

OWER

....................................................................................................... 61

7.2.1. 3.3Vaux DC Characteristics ............................................................................... 61

7.2.2. 3.3Vaux Minimum Required Current Capacity................................................... 62

7.3. 3.3V

AUX

S

YSTEM

D

ESIGN

R

EQUIREMENTS

.................................................................. 62

7.3.1. Power Delivery Requirements............................................................................. 62

7.3.2. PCI Bus RST# Signaling Requirements .............................................................. 63

7.3.3. Voltage Sequencing ............................................................................................. 64

7.4. 3.3V

AUX

A

DD

-

IN

C

ARD

D

ESIGN

R

EQUIREMENTS

......................................................... 65

7.4.1. 3.3Vaux Power Consumption Requirements....................................................... 65

7.4.2. Physical Connection to the 3.3Vaux Pin............................................................. 65

7.4.3. Isolation of 3.3Vaux from Main 3.3V.................................................................. 65

7.4.4. 3.3Vaux Presence Detection................................................................................ 66

8. SOFTWARE SUPPORT FOR PCI POWER MANAGEMENT .................................. 67

8.1. I

DENTIFYING

PCI F

UNCTION

C

APABILITIES

.................................................................. 67

8.2. P

LACING

PCI F

UNCTIONS IN A

L

OW

P

OWER

S

TATE

...................................................... 67

8.2.1. Buses.................................................................................................................... 68

8.2.2. D3 State............................................................................................................... 68

8.3. R

ESTORING

PCI F

UNCTIONS

F

ROM A

L

OW

P

OWER

S

TATE

............................................ 69

8.3.1. D0 “Uninitialized” and the DSI Bit.................................................................... 69

8.3.2. D1 and D2 States................................................................................................. 70

8.3.3. D3 State............................................................................................................... 70

8.4. W

AKE

E

VENTS

............................................................................................................. 70

8.4.1. Wake Event Support ............................................................................................ 70

8.4.2. The D0 “Initialized” State From a Wake Event.................................................. 71

8.5. G

ET

C

APABILITIES

........................................................................................................ 71

PCI BUS POWER MANAGEMENT INTERFACE SPECIFICATION, REV. 1.2

5

8.6. S

ET

P

OWER

S

TATE

....................................................................................................... 71

8.7. G

ET

P

OWER

S

TATUS

..................................................................................................... 72

8.8. S

YSTEM

F

IRMWARE

I

NITIALIZATION

............................................................................. 72

9. OTHER CONSIDERATIONS......................................................................................... 73

- 1

- 2

前往页