verilog testbench

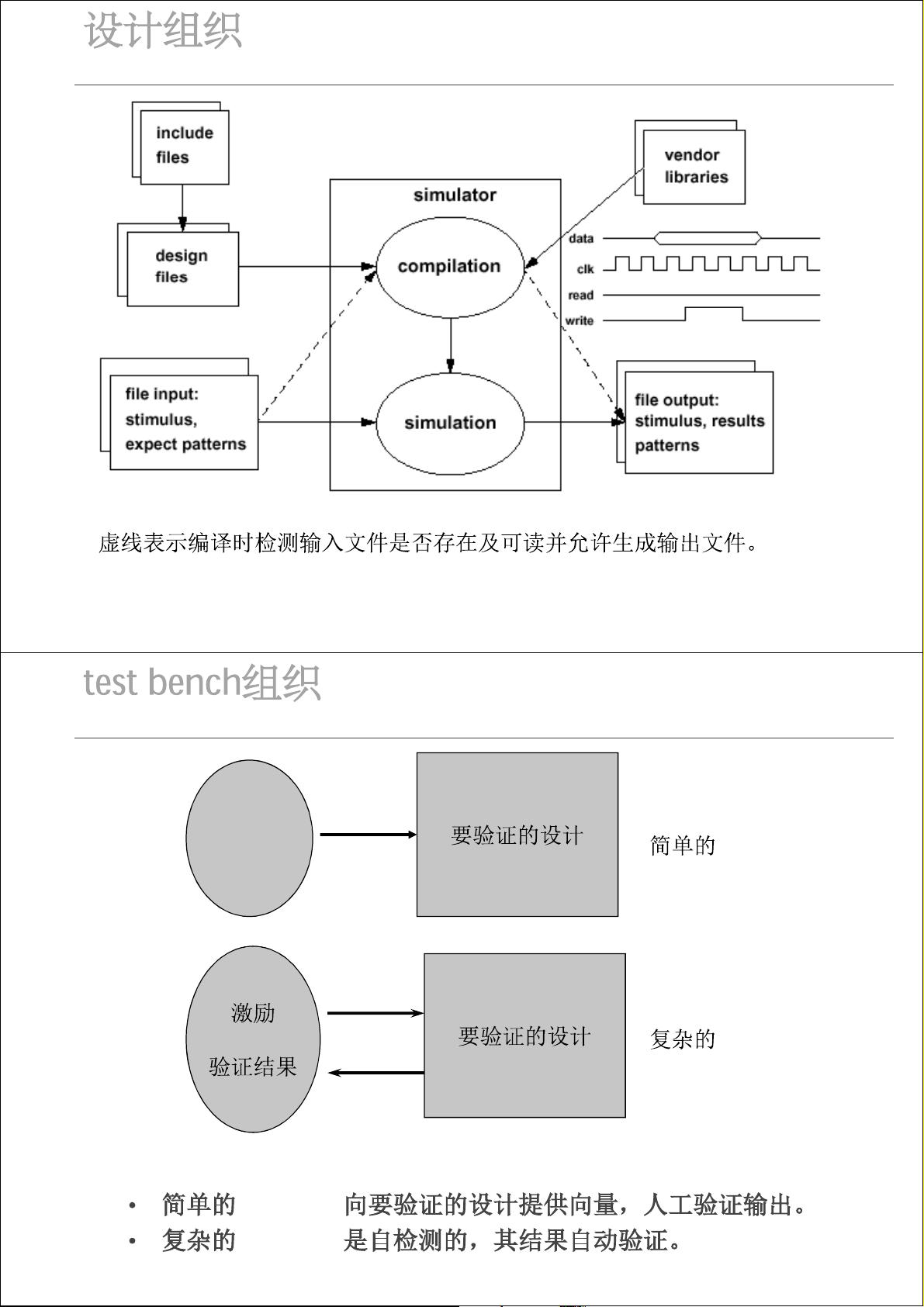

### Verilog Testbench 写法入门 在数字电路设计领域,Verilog 是一种非常重要的硬件描述语言(HDL),广泛用于集成电路的设计与验证。而测试平台(Testbench)则是用来验证设计模块(Design Under Test, DUT)是否按预期工作的重要组成部分。本文将详细介绍 Verilog Testbench 的基本写法,并通过示例来展示如何编写有效的测试平台。 #### 一、Verilog Testbench 基础概念 **1.1 Testbench 定义** Testbench 是一种特殊的 Verilog 模块,它不参与最终的硬件合成,而是作为仿真工具的一部分,用于驱动设计模块并观察其行为是否符合预期。Testbench 主要包括以下几个部分: - **激励信号(Stimulus)**:用来模拟输入到设计模块中的信号。 - **时钟信号(Clock Signal)**:大多数数字系统都需要时钟信号来进行同步控制。 - **结果验证(Verification)**:比较设计模块的实际输出与预期输出,判断是否一致。 - **数据采集(Data Collection)**:记录设计模块的输出数据,便于后续分析。 **1.2 Verilog Testbench 结构** 一个典型的 Verilog Testbench 包括以下结构: ```verilog module tb_name; // 声明信号 reg clk; wire rst; // 创建设计模块实例 dut_instance dut_name (rst, clk); // 测试逻辑 initial begin // 初始化信号 clk = 0; // 测试流程 while (true) begin // 产生时钟信号 #5 clk = !clk; // 激励信号设置 if (clk == 1) begin // 设置输入信号 // 观察输出信号 end end end endmodule ``` #### 二、Verilog Testbench 实战示例 **2.1 基本测试平台** 下面通过几个具体的例子来介绍 Verilog Testbench 的编写方法。 **2.1.1 简单测试平台** 这是一个简单的测试平台示例,展示了如何创建一个时钟信号以及如何在不同的时间点设置激励信号。 ```verilog module simple_tb; reg clk; reg [7:0] data_bus; // 时钟生成 always #5 clk = !clk; initial begin // 初始化信号 data_bus = 8'h00; #10 data_bus = 8'h45; #20 repeat(10) #10 data_bus = data_bus + 1; #25 repeat(5) #20 data_bus = data_bus << 1; #140 data_bus = 8'h0f; end endmodule ``` **2.1.2 使用 fork-join 结构** 这个例子演示了如何使用 `fork` 和 `join` 控制多个并行任务。 ```verilog module fork_join_tb; reg clk; reg [7:0] data_bus; always #5 clk = !clk; initial begin fork #10 data_bus = 8'h45; #20 repeat(10) #10 data_bus = data_bus + 1; #25 repeat(5) #20 data_bus = data_bus << 1; #140 data_bus = 8'h0f; join end endmodule ``` **2.1.3 读取外部文件进行测试** 此示例演示了如何从外部文件读取数据,并将其用作测试激励。 ```verilog module file_read_tb; reg [7:0] in_vec, out_vec; integer RESULTS, STIMULUS; initial begin STIMULUS = $fopen("stimulus.txt"); RESULTS = $fopen("results.txt"); fork if (STIMULUS != 0) forever #(period/2) $fstrobeb(STIMULUS, "%b", in_vec); if (...) end endmodule ``` #### 三、总结 以上介绍了 Verilog Testbench 的基本概念及其实现方式。通过这些示例,我们可以看到 Verilog Testbench 在数字电路设计验证中的重要性。为了更好地验证设计的正确性,测试平台需要精心设计,确保能够覆盖各种可能的情况,从而帮助工程师发现潜在的问题并进行优化。此外,利用并行处理、循环结构以及外部文件读取等高级特性可以进一步提高测试效率和质量。

- 粉丝: 1

- 资源: 4

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功