编写verilog测试验证程序 如何编写测试验证程序(test bench)

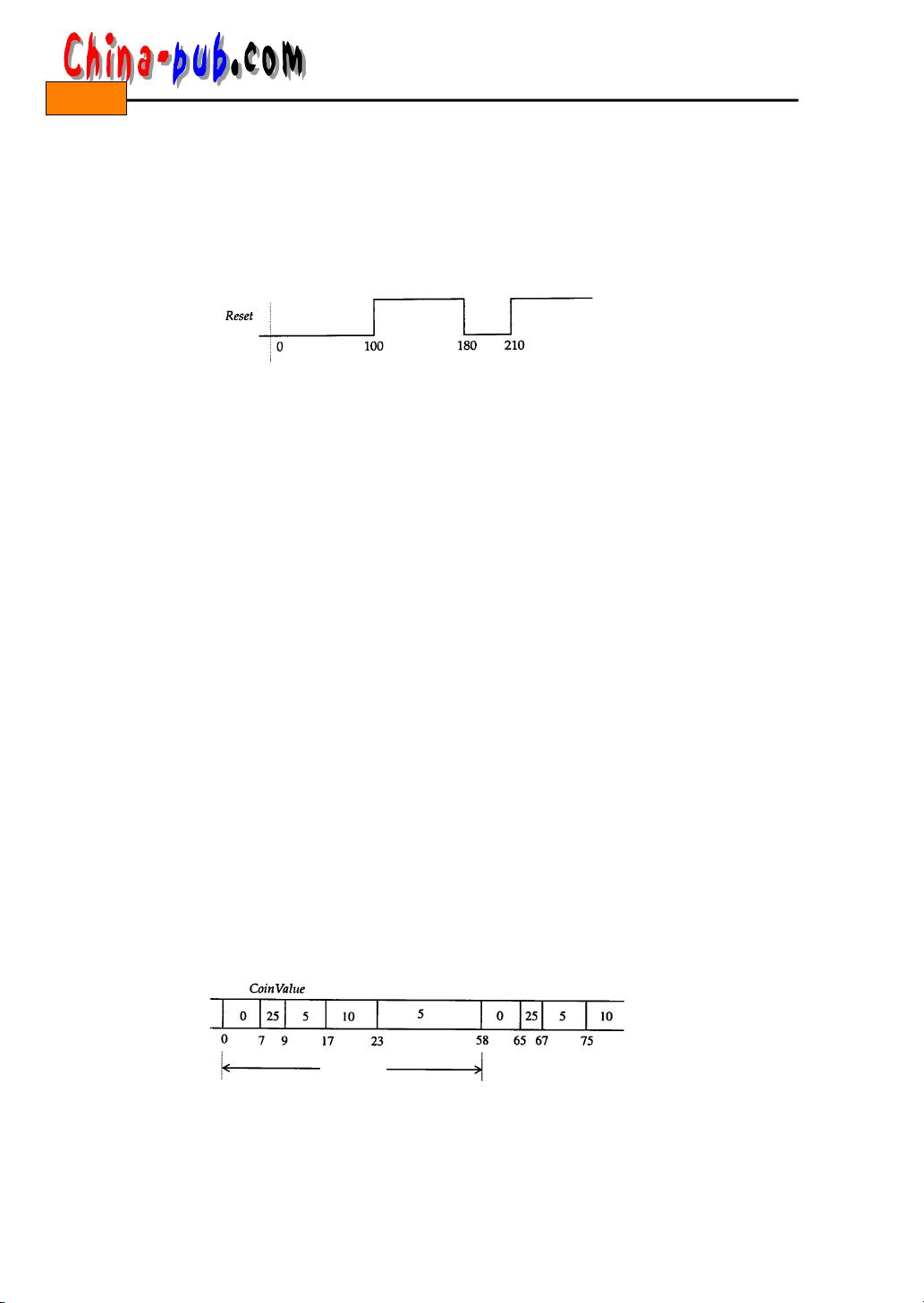

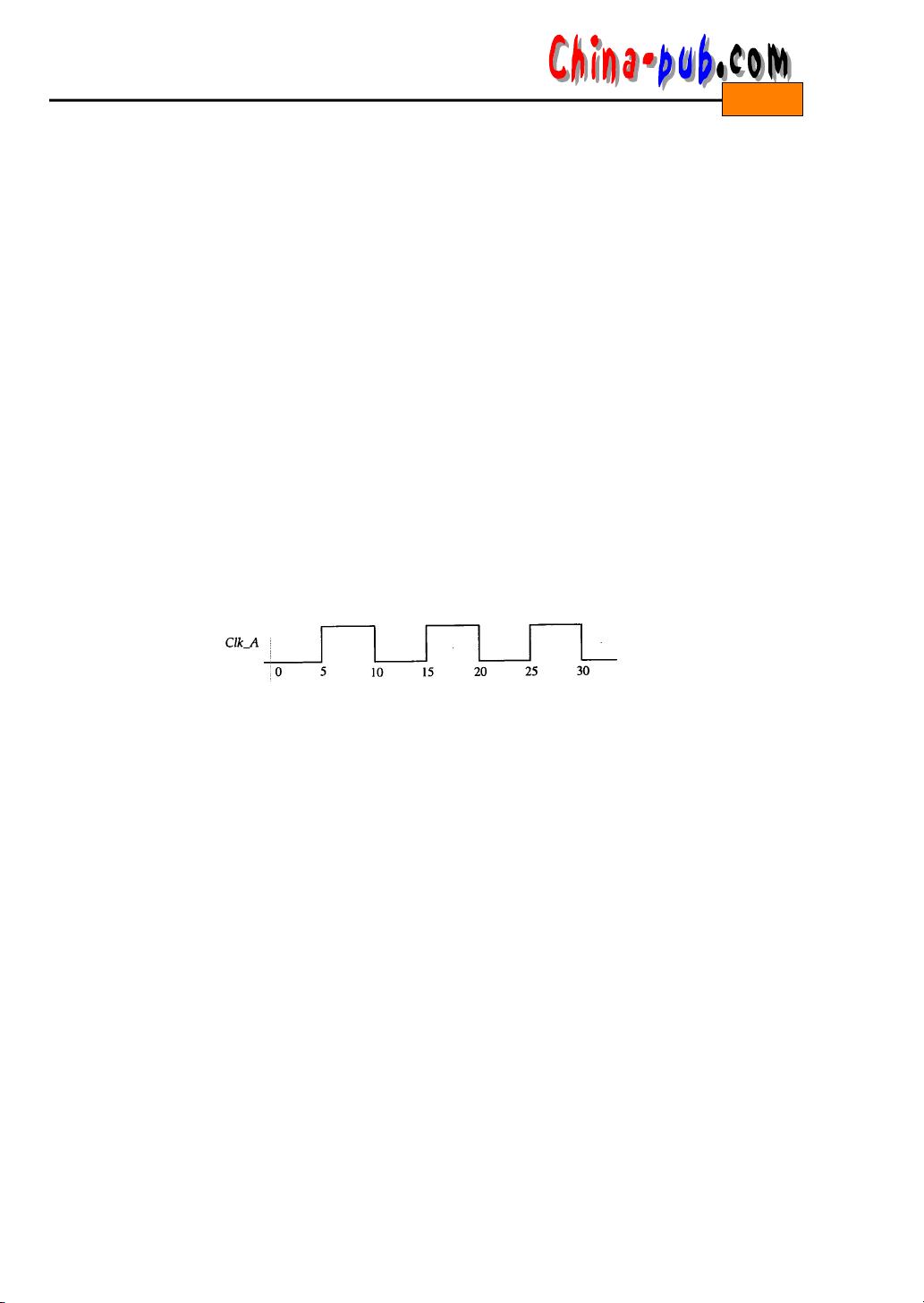

Verilog测试验证程序(Test Bench)编写指南 在 Verilog HDL 中,测试验证程序(Test Bench)是一种特殊的模块,旨在测试和验证设计的正确性。测试验证程序有三个主要目的:产生模拟激励(波形),将输入激励加入到测试模块并收集其输出响应,将响应输出与期望值进行比较。 典型的测试验证程序形式如下: ```verilog module Test_Bench; // 局部寄存器和网线声明 // 生成波形 // 实例化模块 // 监控输出并与期望值比较 endmodule ``` 测试验证程序中,通过实例化,激励自动加载于测试模块。 波形产生有两种主要方法:1)产生波形,并在确定的离散时间间隔加载激励;2)根据模块状态产生激励,即根据模块的输出响应产生激励。通常需要两类波形。一类是具有重复模式的波形,例如时钟波形,另一类是一组指定的值确定的波形。 使用 Initial 语句可以产生波形。例如: ```verilog initial begin Reset = 0; #100 Reset = 1; #80 Reset = 0; #30 Reset = 1; end ``` 这将产生如图 11-1 所示的波形。 使用 Always 语句可以重复产生一个值序列。例如: ```verilog parameter REPEAT_DELAY = 35; integer CoinValue; always begin CoinValue = 0; #7 CoinValue = 25; #2 CoinValue = 5; #8 CoinValue = 10; #6 CoinValue = 5; #REPEAT_DELAY; end ``` 这将产生如图 11-2 所示的重复序列。 在生成重复模式时,可以使用连续赋值形式加以简化。但是,这种做法并不完全正确。问题在于 Clock 是一个线网(只有线网能够在连续赋值中被赋值),它的初始值是 z,并且,z 等于 x,~x 等于 x。因此 Clock 的值永远固定为值 x。现在需要一种初始化 Clock 的方法。可以用 Initial 语句实现。 ```verilog initial Clock = 0; ``` 然而,现在 Clock 必须是寄存器数据类型(因为只有寄存器数据类型能够在 Initial 语句中被赋值)。

剩余17页未读,继续阅读

- 粉丝: 40

- 资源: 11

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功

- 1

- 2

前往页