Verilog-2001新增特性[参照].pdf

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

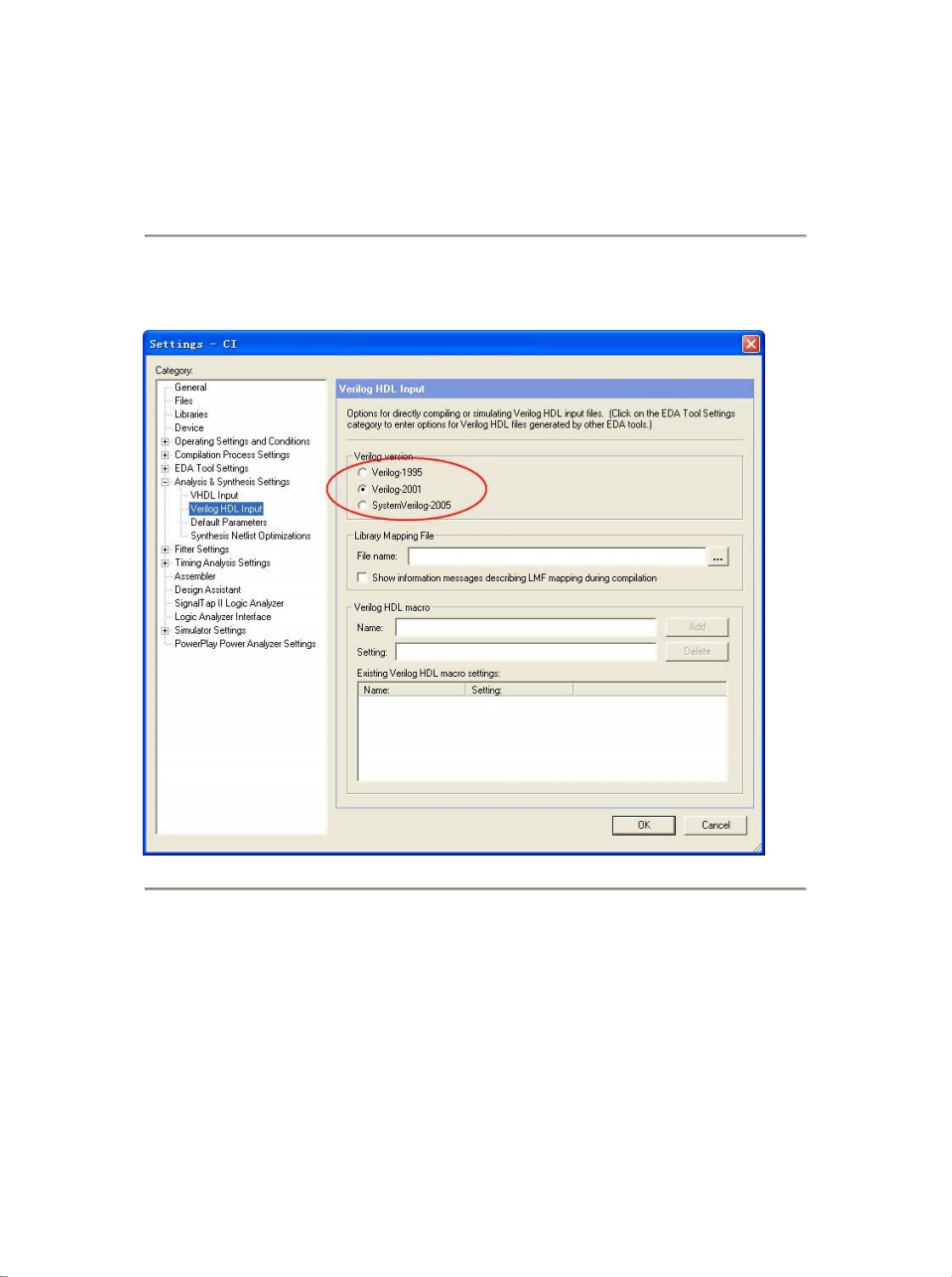

Verilog-2001是Verilog语言的一个重要版本更新,它在原有的Verilog-1995基础上引入了一系列新特性,旨在增强语言的表达能力和灵活性,尤其在硬件描述和设计自动化方面。以下是对Verilog-2001新增特性的详细说明: 1. **Generate语句**:这是Verilog-2001最重要的特性之一,它允许根据条件生成模块或原语的多个实例。`generate`语句使得设计者能够更加灵活地创建并行结构,如阵列和条件分支。例如,`generate`可以结合`if-else`、`case`和`for`语句,根据参数或变量的不同值实例化不同类型的模块。在给定的例子中,如果输入宽度小于8,则实例化CLA_multiplier,否则实例化WALLACE_multiplier。 2. **Genvar类型**:`genvar`是一种新的数据类型,用于在`generate`循环中作为索引变量,它只能存储非负整数。在循环中,genvar变量必须被声明,并且它的值在每次迭代中自动递增。 3. **Localparam**:类似于`parameter`,但`localparam`的值在声明后不可更改。这使得局部参数可以在模块内部定义,而不会影响其他模块中的相同参数值。在上述代码中,`product_width`是基于`a_width`和`b_width`计算的,然后作为输出宽度的本地参数。 4. **Constant Functions**:Verilog-2001引入了常量函数,允许在定义参数或常量时使用更复杂的表达式。这些表达式必须在编译时就能计算得出。例如,可以定义一个参数`WIDTH`,使其等于两个其他参数的乘积,这样在设计时就可以动态调整`WIDTH`的值。 5. **Improved System Tasks and Functions**:Verilog-2001增加了更多系统任务和函数,以增强设计者在文本处理、调试和仿真中的能力。 6. **Non-blocking Assignments in Always Blocks**:在Verilog-2001中,非阻塞赋值`<=`可用于所有的`always`块,而不仅仅是组合逻辑块。这简化了代码的编写和理解,因为所有`always`块都可以统一使用一种赋值方式。 7. **New Net Types**:新增了`tri1`和`tri0`网类型,分别表示高阻态和低阻态,用于更精确地描述接口和总线特性。 8. **Strongly-typed Ports**:允许在端口声明中指定数据类型,增强了模块间接口的清晰度和可读性。 9. **Array Concatenation**:Verilog-2001允许数组的串联操作,使得处理多维数组变得更加简单。 10. **SystemVerilog Compatibility**:虽然不是Verilog-2001的直接特性,但这个版本为后续的SystemVerilog-2005打下了基础,使得部分SystemVerilog的功能可以在Verilog-2001中使用。 以上特性极大地扩展了Verilog的表达力,使得硬件设计者能够更有效地描述复杂的数字系统,特别是在FPGA和ASIC设计中。在实际应用中,如Quartus II这样的软件开发环境中,可以通过设置对话框选择使用Verilog的不同版本,以充分利用每个版本提供的功能。

- 粉丝: 2

- 资源: 12万+

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜 信息提交成功

信息提交成功