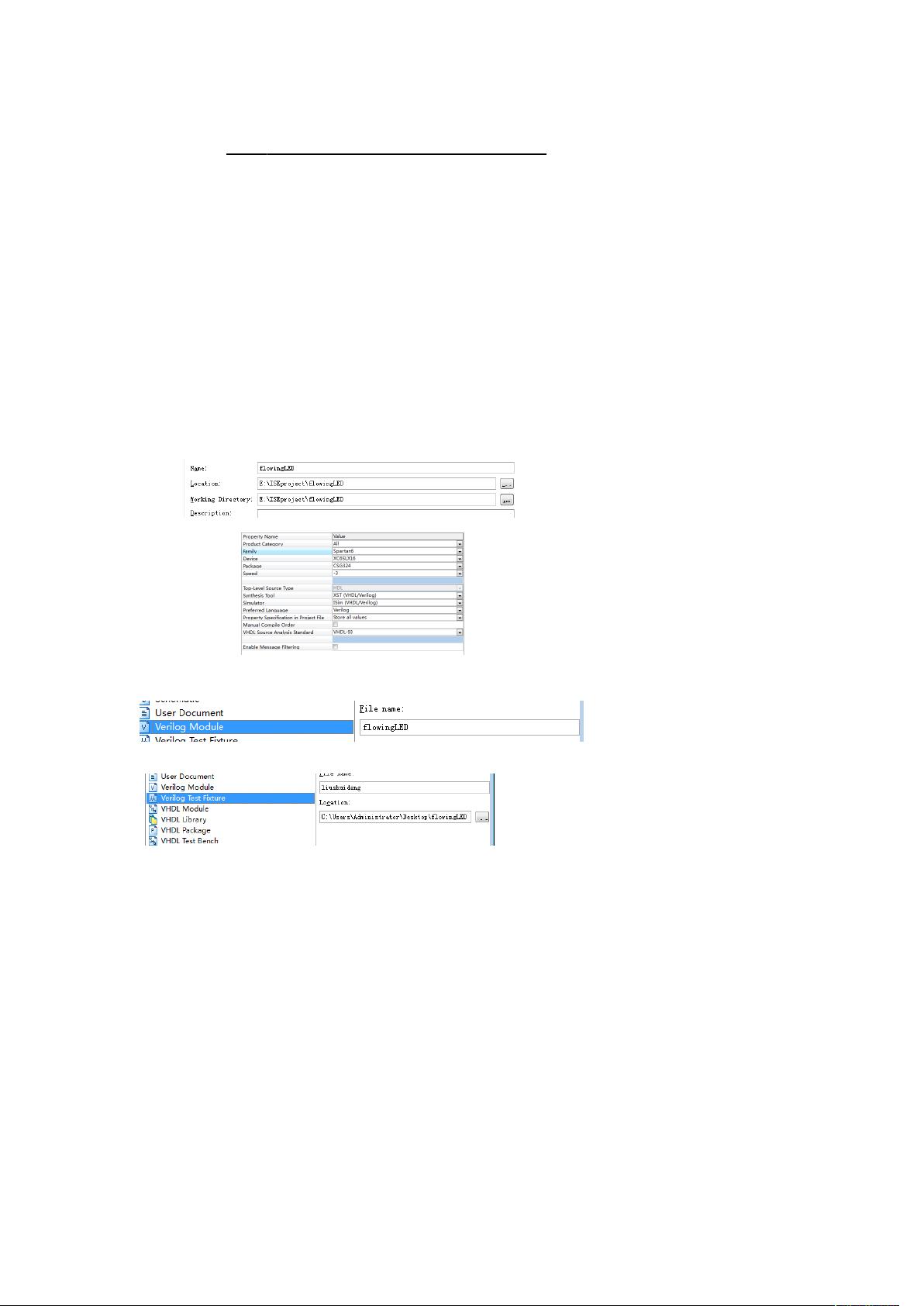

数字跑表设计 数字跑表设计是使用 Verilog HDL 语言编写的数字逻辑设计,旨在熟悉 Xilinx ISE Design Suite 12.3 软件的使用和 Verilog 语言的编程。该设计的主要功能是每过一秒,LED 灯循环移位,实现八位循环移位。 在设计过程中,首先需要新建一个工程,配置工程的基本信息,然后添加 Verilog 模块,编写设计文件。设计文件主要包括两个部分:模块划分和仿真模块。在模块划分中,使用 Verilog 语言编写了流程控制语句,实现了时钟分频和 LED 灯的循环移位。在仿真模块中,使用 Isim 或者 Modelsim 进行功能仿真和时序仿真,并检验正确性。 通过仿真结果分析,可以看出在放大倍数比较小时,得到的波形几乎是一样的,而在放大倍数比较大时,时序仿真输出的边沿会与时钟有一定的偏离,而功能仿真无论放大多少始终与时钟的边沿保持一致。 在下载目标板后,实现的功能分析显示,复位键按下时,开始计数,并且此时 LED1 亮,当时间为 1 秒,LED2 开始亮,LED1 熄灭,如此,实现八位循坏移位。 然而,在设计过程中,也存在一些问题和改进的方向,例如,可以增加一些按键操作,例如,按下某个按键让 LED 灯不再继续亮,而是从头开始循环,或者按下该键停止循环,再次按下键继续循环。 通过这个设计,熟悉了 Verilog 语言的使用和 ISE 软件的操作,提高了编程的水平和速度,并且学会了自己找错误并不断纠正,最终使得程序能正确地工作。 数字跑表设计是使用 Verilog HDL 语言编写的数字逻辑设计,旨在熟悉 Xilinx ISE Design Suite 12.3 软件的使用和 Verilog 语言的编程,实现八位循环移位的功能,并且存在一些问题和改进的方向。

剩余10页未读,继续阅读

昭晖君2021-06-04打不开这个

昭晖君2021-06-04打不开这个

- 粉丝: 0

- 资源: 1

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功