PCI规范 specification

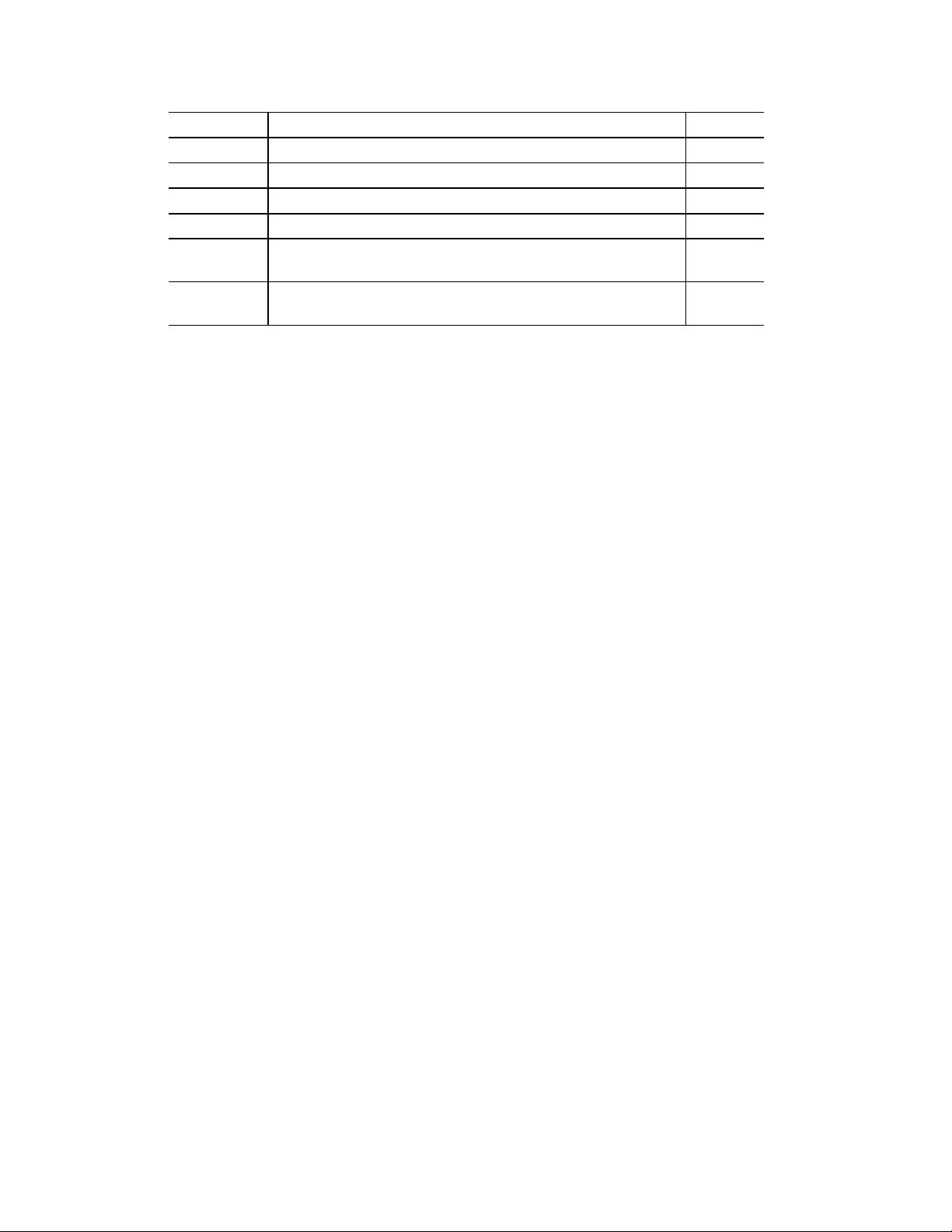

### PCI规范 specification #### PCI局部总线手册概述 PCI(Peripheral Component Interconnect)局部总线规范3.0版,发布于2002年8月12日,是PCI-SIG(PCI Special Interest Group)组织制定的一项标准。该文档详细介绍了PCI局部总线的设计原理、功能特性以及使用规范等内容,旨在为硬件制造商提供一个统一的标准接口,以便在不同类型的计算机系统中实现高效的数据传输。 #### 版本历史与修订记录 自1992年首次发布以来,PCI规范经历了多次修订和完善: - **1.0版**:1992年6月22日发布,为最初的版本。 - **2.0版**:1993年4月30日发布,新增了连接器和扩展卡规范。 - **2.1版**:1995年6月1日发布,对原有规范进行了澄清,并添加了支持66MHz的工作模式。 - **2.2版**:1998年12月18日发布,整合了工程更改通知(ECN),提高了文档的可读性。 - **2.3版**:2002年3月29日发布,进一步完善了ECN和错误修正,并删除了仅支持5V电压的扩展卡。 - **3.0版**:2002年8月12日发布,移除了对5V电压键控系统板连接器的支持。 #### PCI局部总线规格介绍 ##### 特点与优势 - **高速数据传输**:PCI局部总线提供了比传统ISA总线更高的数据传输速率。 - **热插拔支持**:部分版本的PCI规范支持热插拔功能,即设备可以在不关闭主机电源的情况下进行安装或卸载。 - **多设备支持**:能够同时支持多个设备在同一总线上工作,提高了系统的灵活性。 - **低延迟通信**:相比其他总线技术,PCI局部总线提供了更低的通信延迟,从而提高了整体性能。 - **广泛兼容性**:由于PCI规范被广泛采用,因此几乎所有主流操作系统都支持PCI设备。 ##### 应用场景 PCI局部总线主要应用于以下领域: - **服务器**:服务器通常需要大量的I/O接口,PCI局部总线能够满足这些需求。 - **工作站**:对于需要高性能图形处理的工作站而言,PCI局部总线提供了必要的带宽支持。 - **台式机**:大多数现代台式计算机都配备了基于PCI的扩展槽,用于安装显卡、声卡等外设。 - **嵌入式系统**:许多嵌入式应用也利用了PCI局部总线来扩展其功能。 #### 技术细节 - **电气特性**:包括信号电平、阻抗匹配等方面的要求。 - **机械特性**:规定了连接器和插槽的物理尺寸、形状等。 - **时序特性**:描述了数据传输过程中的时序要求,如设置时间、保持时间等。 - **配置管理**:包括PCI设备的初始化、配置空间访问机制等。 - **中断管理**:规定了如何处理PCI设备产生的中断信号。 - **DMA操作**:定义了直接内存访问的操作流程。 #### 结论 PCI局部总线规范3.0版不仅提供了详细的硬件设计指导,还涵盖了软件开发所需的各项技术细节。通过遵循这些规范,硬件制造商可以确保产品具有良好的兼容性和稳定性。此外,PCI-SIG组织还提供了联系方式,以便用户获取最新的规范版本或其他技术支持。随着技术的发展,虽然PCI已被更新的技术所取代,但其在计算机体系结构中的地位依然不可忽视。

剩余343页未读,继续阅读

shangyl002012-12-24PCI Local Bus Specification Revision 3.0 主要看下第6章,還不錯!

shangyl002012-12-24PCI Local Bus Specification Revision 3.0 主要看下第6章,還不錯! limingjiang1012018-01-15内容非常清晰,相当不错,谢谢分享。

limingjiang1012018-01-15内容非常清晰,相当不错,谢谢分享。 _Wayne_2020-11-05不错啊,就是有点贵哟!

_Wayne_2020-11-05不错啊,就是有点贵哟! download_lt2019-04-05算是学习PCI必不可少的资料吧,积分还算比较值

download_lt2019-04-05算是学习PCI必不可少的资料吧,积分还算比较值 chouxier2012-09-07相对简洁些。

chouxier2012-09-07相对简洁些。

- 粉丝: 12

- 资源: 4

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- TMS320F28069控制500-1000Vdc 0-60A 30KW 三相PFC充电桩程序

- 双馈风机 DFIG 低电压穿越 MATLAB仿真模型 LVRT 双馈异步风力 Crowbar电路 (1)转子侧变器采用基于定子电压定向的矢量控制策略,有功无功解耦,具备MPPT能力,采用功率外环电

- 电机控制器,FPGA 硬件电流环 基于FPGA的永磁同步伺服控制系统的设计,在FPGA实现了伺服电机的矢量控制 有坐标变,电流环,速度环,位置环,电机反馈接口,SVPWM Verilog

- 鲁棒优化多阶段规划 利用列和约束生成(C&CG)算法进行求解 提升了配电网对可再生能源的消纳能力且改善了配电网的运行指标,同时又保证了微电网投资商的经济利益,有效实现了配电网与微电网的协调发展

- 脉振方波HFI HFI脉振方波高频注入模型代码和matlab仿真 码基于TI283x,:::仿真和相关文档齐全,有仿真的代码,仿真也可以生成代码

- 主机欧姆龙CP1H,主机带四轴,从机CP1H带数轴进行运动控制 全自动CE锂电极片多极耳连续冲切机 欧姆龙CP1H+MCGS昆仑通态触摸屏 伺服电机控制,电阻尺应用控制,电芯极耳间距定长冲切控制,涵盖

- 物流中心选址规划 帝企鹅优化调度算法 基于帝企鹅优化算法的全国物流中心选址规划算法MATLAB程序源代码及完整数据表格(Excel文件,详见附图) 程序到手可运行 关联词:备选点选址规划,调度

- 风机变桨控制FAST与MATLAB SIMULINK联合仿真模型非线性风力发电机的 PID独立变桨和统一变桨控制下仿真模型,对于5WM非线性风机风机进行控制 链接simulink的scope出转速对比

- 逆变器光伏并网逆变器资料,包含原理图,pcb,源码以及元器件明细表 如下: 1) 功率接口板原理图和pcb,元器件明细表 2) 主控DSP板原理图(pdf);如果有需要,可发mentor版

- PSASP环境下基于PMU同步测量的分区惯量估计方法,附资料 对应主要模式下的频率、分区联络线功率测量,做为PMU计算的依据: 1、恒功率负荷模式; 2、感应电动机负荷模式; 3、1模式基础上叠加2

- TMS320F28069控制500-1000Vdc 0-60A 30KW 三相PFC充电桩硬件设计

- 基于simulink的FCV燃料电池电动汽车模型 包含3个汽车模型,双输入DCDC模型,电池管理系统模型 模型建模清晰,运行良好,部分内容如截图所示 需要matlab2015b

- 基于Html与C#、CSS、JavaScript的Blazor入门课程设计源码

- 西门子1500PLC大型立体仓库堆垛机输送机程序项目,具体为智能物流实际项目案例,成熟并且稳定的运行现场,有一万多个库位,输送机一百多个,堆垛机八个,仓库分楼下和楼上两层,以西门子1500plc为控制

- 24V 65W 120W 350W反激电源 全套资料(原理图+PCB+变压器规格+测试报告)

- PMSM模型预测电流控制集(MPCC):单矢量,双矢量,三矢量;单步预测,两步预测,三步预测;两点平,三电平;无差拿预测...... 仿真模型和文档包括且不限于:见图

信息提交成功

信息提交成功