基于FPGA的任意四位除法器代码说明与仿真文档.docx

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

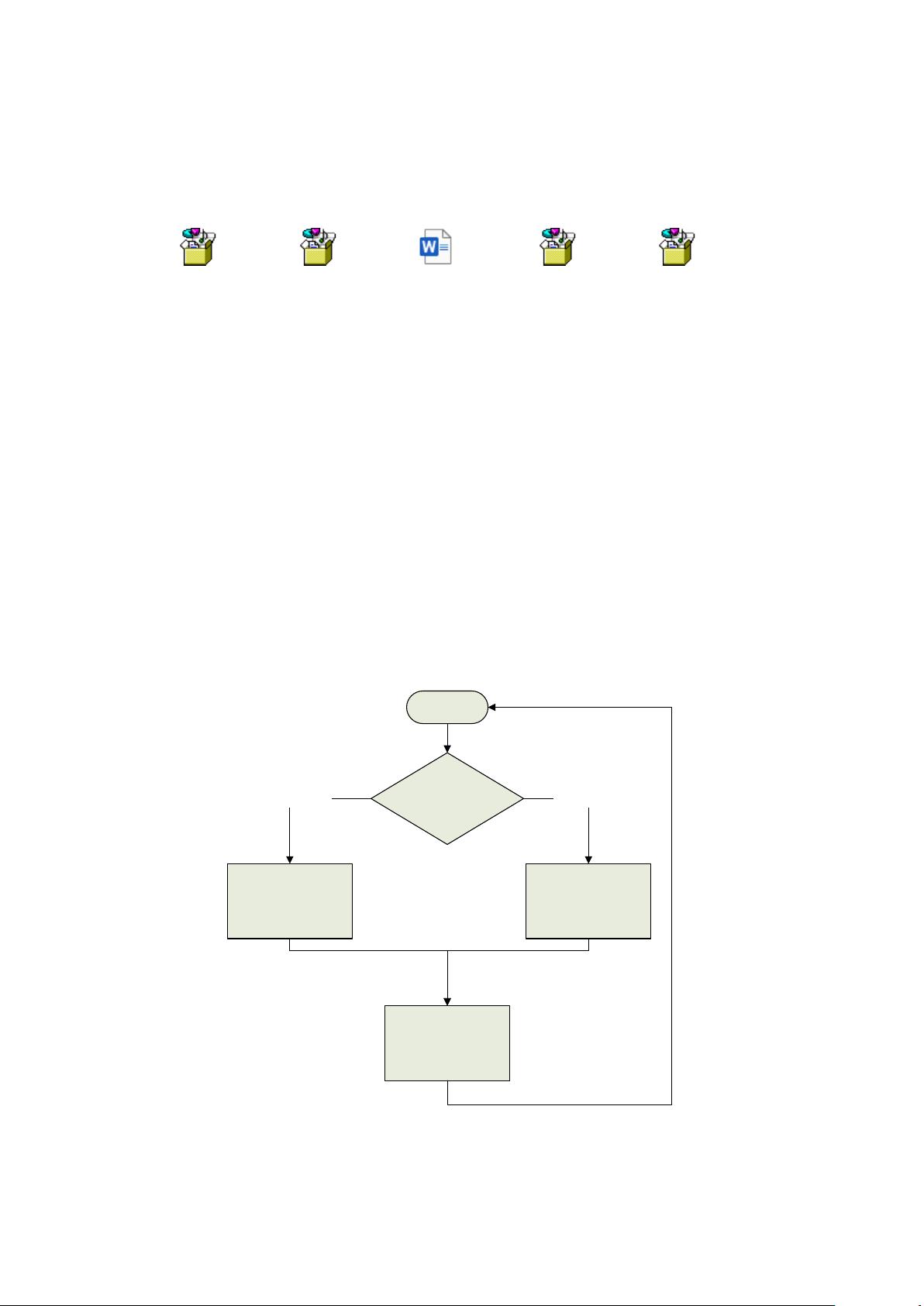

**基于FPGA的任意四位除法器设计** 在数字电路设计中,FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,允许开发者根据需求定制硬件逻辑。本设计中,我们创建了一个基于FPGA的任意四位除法器,能够处理有符号和无符号的四位数除法运算。下面我们将详细解释设计原理、流程和仿真结果。 **设计原理** 除法器的核心思想是基于除法的基本公式:被除数 = 商数 × 除数 + 余数。设计中,我们使用加法器和减法器作为基本单元来实现这一过程。当进行除法运算时,系统首先检查输入的被除数和除数,然后通过一系列减法操作来求得商和余数。为了处理有符号和无符号的运算,我们引入一个名为`sign`的控制信号。如果`sign`为1,则执行有符号运算;如果`sign`为0,则执行无符号运算。 **有符号运算** 在有符号运算模式下,当`sign`为1时,除法器会考虑数值的正负。例如,当除数为0时,按照数学规则,除法是未定义的,因此输出为高阻态'Z',表示无效运算。当被除数为0,除数为-1时,商和余数均为0,这是正确的结果。对于其他各种组合,例如被除数为-2,除数为-6或被除数为5,除数为-6,除法器都能正确计算出商和余数。 **无符号运算** 在无符号运算模式下,`sign`为0,除法器忽略数值的正负,仅处理数值大小。同样,当除数为0时,输出也为'Z'。例如,当被除数为0,除数为15时,商和余数均为0,符合预期。其他情况下,如被除数为14,除数为10,或者被除数为11,除数为11,除法器也能准确地计算出商和余数。 **设计流程** 设计流程包括以下几个步骤: 1. 接收输入的被除数和除数,以及`sign`信号。 2. 判断运算类型(有符号或无符号)。 3. 如果是无符号运算,直接进行减法和加法运算。 4. 如果是有符号运算,需考虑正负,然后进行运算。 5. 检查除数是否为0,如果是,则输出高阻态'Z'。 6. 通过连续的减法操作更新商,并计算余数。 7. 输出最终的商和余数。 **仿真验证** 为了验证设计的正确性,我们进行了详尽的仿真测试,覆盖了多种可能的输入组合,包括正数、负数和0。通过观察仿真结果,我们可以确认除法器在各种情况下均能正确计算出商和余数。 **总结** 这个基于FPGA的任意四位除法器设计提供了一种灵活且高效的解决方案,可以处理有符号和无符号的四位数除法运算。设计中利用了FPGA的可编程性,通过控制信号实现不同类型的运算,同时通过仿真验证了其正确性和鲁棒性。这样的设计对数字系统中的计算和数据处理具有重要意义,特别是在需要快速、高效除法运算的应用场景中。

- 粉丝: 367

- 资源: 6419

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 基于CSS与JavaScript的积分系统设计源码

- 生物化学作业_1_生物化学作业资料.pdf

- 基于libgdx引擎的Java开发连连看游戏设计源码

- 基于MobileNetV3的SSD目标检测算法PyTorch实现设计源码

- 基于Java JDK的全面框架设计源码学习项目

- 基于Python黑魔法原理的Python编程技巧设计源码

- 基于Python的EducationCRM管理系统前端设计源码

- 基于Django4.0+Python3.10的在线学习系统Scss设计源码

- 基于activiti6和jeesite4的dreamFlow工作流管理设计源码

- 基于Python实现的简单植物大战僵尸脚本设计源码

信息提交成功

信息提交成功