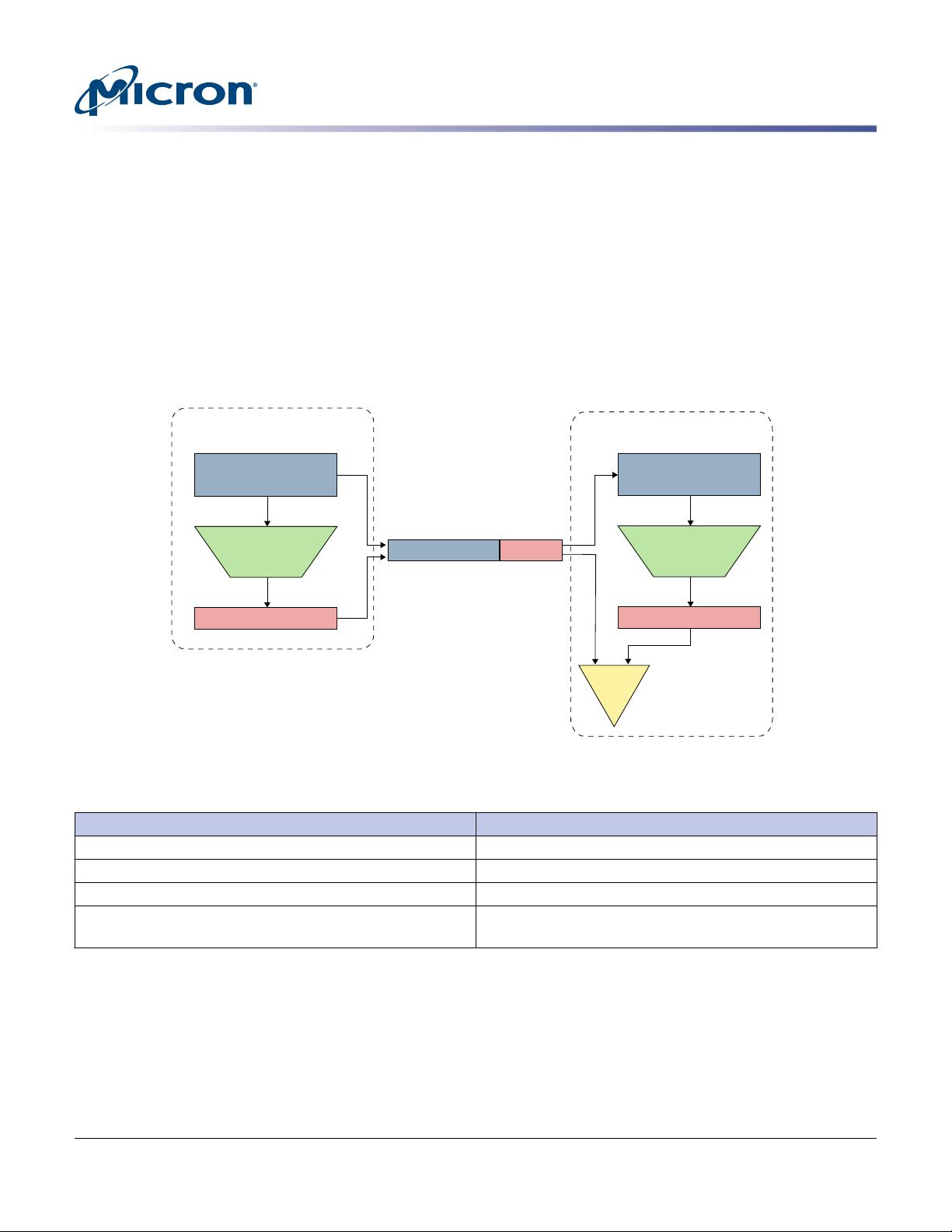

DDR4增加了超过30个新特性,其中大量提供了改进的信令或调试功能: CA奇偶校验、多用途寄存器、可编程写前导、可编程读前导、读序言训练、写CRC、读DBI、写DBI、VREFDQ校准和每个DRAM寻址性。提供对这些特性的深入解释超出了本文档的范围;然而,一个成功的DDR4高速设计将需要使用这些新特性,它们不应被忽视。美光DDR4数据表提供了对这些特性的深入解释。 DDR4内存系统与DDR3系统在许多方面相当相似,但有几项显著且重要的变化直接影响了DDR4设计,包括以下几个关键点: 1. **新VPP电源**:DDR4引入了一个新的电源电压VPP,用于为DDR4内存的辅助功能(如ECC)供电。与DDR3相比,这需要额外的电源管理电路。 2. **移除VREFDQ参考输入**:DDR3中的VREFDQ是一个外部参考电压,而在DDR4中,VREFDQ参考输入被移除,取而代之的是内部校准机制,这要求更精确的内部电压控制。 3. **接口变化**:DDR4的I/O缓冲器接口从中间点终止的SSTL(System Serial Transceiver Logic)转变为VDD终止的伪开漏(POD)。这种变化旨在减少信号反射,提高信号完整性。 4. **ACT_n控制**:ACT_n是DDR4新增的激活引脚,用于控制DRAM的行选通操作,提高了内存访问的效率和灵活性。 DDR4引入了超过30个新特性,其中一些关键的信号和调试功能包括: - **CA奇偶校验**:CA(Command Address)奇偶校验增强了数据传输的错误检测能力。 - **多用途寄存器**:允许更灵活的命令和地址配置,以适应不同的系统需求。 - **可编程写前导**和**可编程读前导**:使得系统可以调整预加重和均衡,优化信号质量。 - **读序言训练**:确保在高速运行时的数据接收准确无误。 - **写CRC(Cyclic Redundancy Check)**:通过校验码验证写入数据的完整性和准确性。 - **读DBI(Data Bus Inversion)**和**写DBI**:自动修正数据总线上的错误,提高数据传输的可靠性。 - **VREFDQ校准**:对数据线的参考电压进行校准,确保信号在传输过程中的稳定性。 - **每个DRAM寻址性**:允许对每个DRAM颗粒单独进行配置和校准,以适应不同的制造差异。 这些特性在DDR4数据表中有详细的解释,对于实现高效能和高带宽的系统设计至关重要。正确地设计和利用这些特性,能够克服由技术进步带来的时序约束,从而提升系统性能。 在设计DDR4板卡时,应遵循一系列的设计规则,例如确保足够的信号裕量,考虑PCB布线的影响,以及进行充分的信号完整性分析。计算过程,如VREFDQ的校准和数据总线写训练,需要严格按照规格书中的步骤进行,以满足严格的DDR4定时规范。未正确执行这些校准和训练可能导致性能严重下降。 DDR4内存系统的设计需要充分利用其新特性,并且需要深入理解每个特性的工作原理和应用方法。只有这样,才能确保设计出的系统能够充分发挥DDR4的优势,实现更高的数据传输速率和系统性能。

剩余33页未读,继续阅读

- 粉丝: 0

- 资源: 7

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 俄罗斯方块作为消遣小游戏,以此目的来锻炼小白

- AZ-900 -186q-.pdf

- html+css+js网页设计 美食 美食模版1个页面带js

- 高精度12bit逐次逼近型SAR ADC电路设计成品 一款包含了第四个月学习的全部经验的高精度sarADC,有效位数高达11.85bit,用来参加某比赛的 smic0.18工艺,全差分结构,3.3V

- 机械设计螺杆供料装置sw22全套技术资料100%好用.zip

- 上市公司-劳务外包数据(2012-2023年).xlsx

- 软件开发界面使用的图标

- 元胞自动机模拟纯金属 合金凝固matlab程序,程序自己编的,还可以结合fluent算出的温度场进行组织模拟 纯金属的380,包括形核和长大以及捕捉模块,适合新手用来了解元胞自动机模拟凝

- 半桥LLC谐振变器 PSIM仿真 电力电子变器 纯模拟电路实现功能 输入:380~400VDC 输出:19VDC,90W

- 广州大学编译原理题库,抄吧抄吧

- 基于optisystem的光通信系统仿真

- 引力场方程耦合常数的修改及宇宙学新视角

- 机械设计锂电池叠片机sw18可编辑全套技术资料100%好用.zip

- 磁流变阻尼器磁场仿真,2D,3D ansys maxwell 阻尼器各类磁场仿真,磁流变液BH曲线添加,磁场分析,磁力线分析,阻尼间隙分析,缸体材料分析,曲线对比

- 机械设计木材削木机sw17全套技术资料100%好用.zip

- labview视觉检测+引导定位螺丝枪,三个相机,一个相机做检测,两个相机做引导定位螺丝枪 同时采用模板匹配、抓边、找圆,内置模块封装好,内含封装好的九点标定和旋转中心

信息提交成功

信息提交成功