没有合适的资源?快使用搜索试试~ 我知道了~

数字集成电路设计课后习题chapter11_ex.pdf

需积分: 20 4 下载量 152 浏览量

2021-05-18

15:25:49

上传

评论 1

收藏 72KB PDF 举报

温馨提示

试读

6页

数字集成电路设计课后习题chapter11_ex.pdf

资源详情

资源评论

资源推荐

1 Chapter 11 Problem Set

Chapter 11

PROBLEMS

1. [E, None, 11.6] For this problem you are given a cell library consisting of full adders and two-

input Boolean logic gates (i.e. AND, OR, INVERT, etc.).

a. Design an N-bit two's complement subtracter using a minimal number of Boolean logic

gates. The result of this process should be a diagram in the spirit of Figure 11.5 . Specify

the value of any required additional signals (e.g., C

in

).

b. Express the delay of your design as a function of N, t

carry

, t

sum

, and the Boolean gate delays

(t

and

, t

or

, t

inv

, etc.).

2. [M, None, 11.6] A magnitude comparator for unsigned numbers can be constructed using full

adders and Boolean logic gates as building blocks. For this problem you are given a cell

library consisting of full adders and arbitrary fan-in logic gates (i.e., AND, OR, INVERTER,

etc.).

a. Design an N-bit magnitude comparator with outputs and A = B using a minimal

number of Boolean logic gates. The result of this process should be a diagram in the spirit

of Figure 11.5. Specify the value of any required control signals (e.g., C

in

).

b. Express the delay of your design in computing the two outputs as a function of N, t

carry

,

t

sum

, and the Boolean gate delays (t

and

, t

or

, t

inv

, etc.).3.

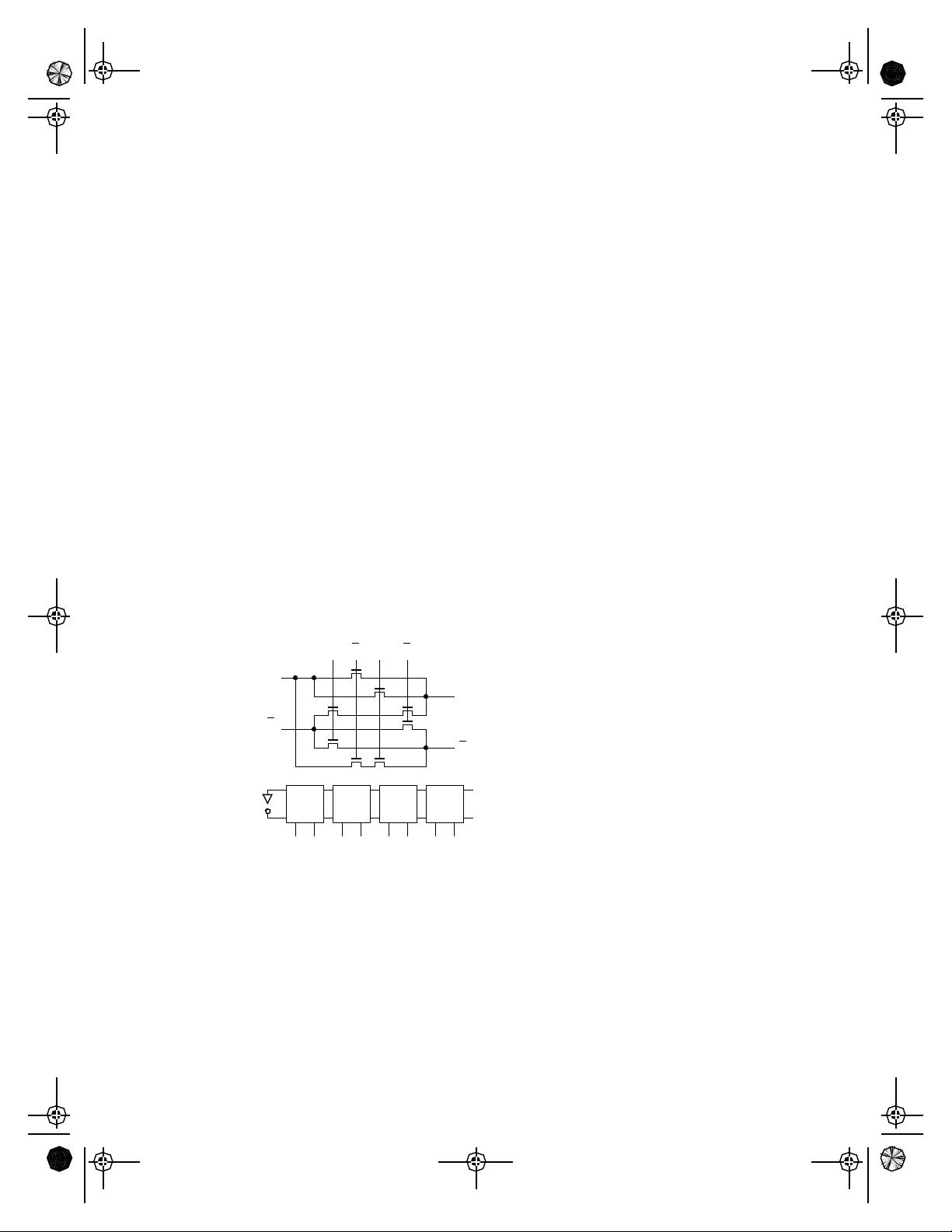

3. [E, None, 11.6] Show how the arithmetic module in Figure 0.1 can be used as a comparator.

Derive an expression for its propagation delay as a function of the number of bits.

4. [E, None, 11.6] The circuit of Figure 11.2 implements a 1-bit datapath function in dynamic

(precharge/evaluate) logic.

a. Write down the Boolean expressions for outputs F and G. On which clock phases are out-

puts F and G valid?

b. To what datapath function could this unit be most directly applied (e.g., addition, subtrac-

tion, comparison, shifting)?

5. [M, None, 11.3] Consider the dynamic logic circuit of Figure 0.2 .

a. What is the purpose of transistor M

1

? Is there another way to achieve the same effect, but

with reducing capacitive loading on the clock Φ?

AB

≥

Figure 0.1 Arithmetic module.

a

i

a

i

b

j

b

j

c

j

d

j

c

j+1

d

j+1

c

0

c

1

d

0

d

1

c

1

c

2

d

1

d

2

c

2

c

3

d

2

d

3

c

3

c

4

d

3

d

4

a

0

b

0

a

1

b

1

a

2

b

2

a

3

b

3

second-chapter11-ex.fm Page 1 Friday, October 3, 2003 9:48 PM

Lambertttt

- 粉丝: 0

- 资源: 10

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论0