没有合适的资源?快使用搜索试试~ 我知道了~

ASIC TOP-DOWN设计教程

需积分: 9 7 下载量 88 浏览量

2009-06-24

14:00:32

上传

评论

收藏 1.1MB PDF 举报

温馨提示

试读

58页

以实例的方式讲述了ASIC设计的基本流程,前端的RTL设计与仿真、逻辑综合、以及后端基于标准单元库的版图设计技术

资源推荐

资源详情

资源评论

6 Dec 2005

Top-down digital design flow

EDA tools:

Modelsim, Synopsys Design Compiler, Cadence Encounter

Alain Vachoux

Microelectronic Systems Lab

STI-IMM-LSM

alain.vachoux@epfl.ch

version 3.0.2 / 6 Dec 2005

Top-down digital design flow ii

AVx / version 3.0.2 / 6 Dec 2005

Document history

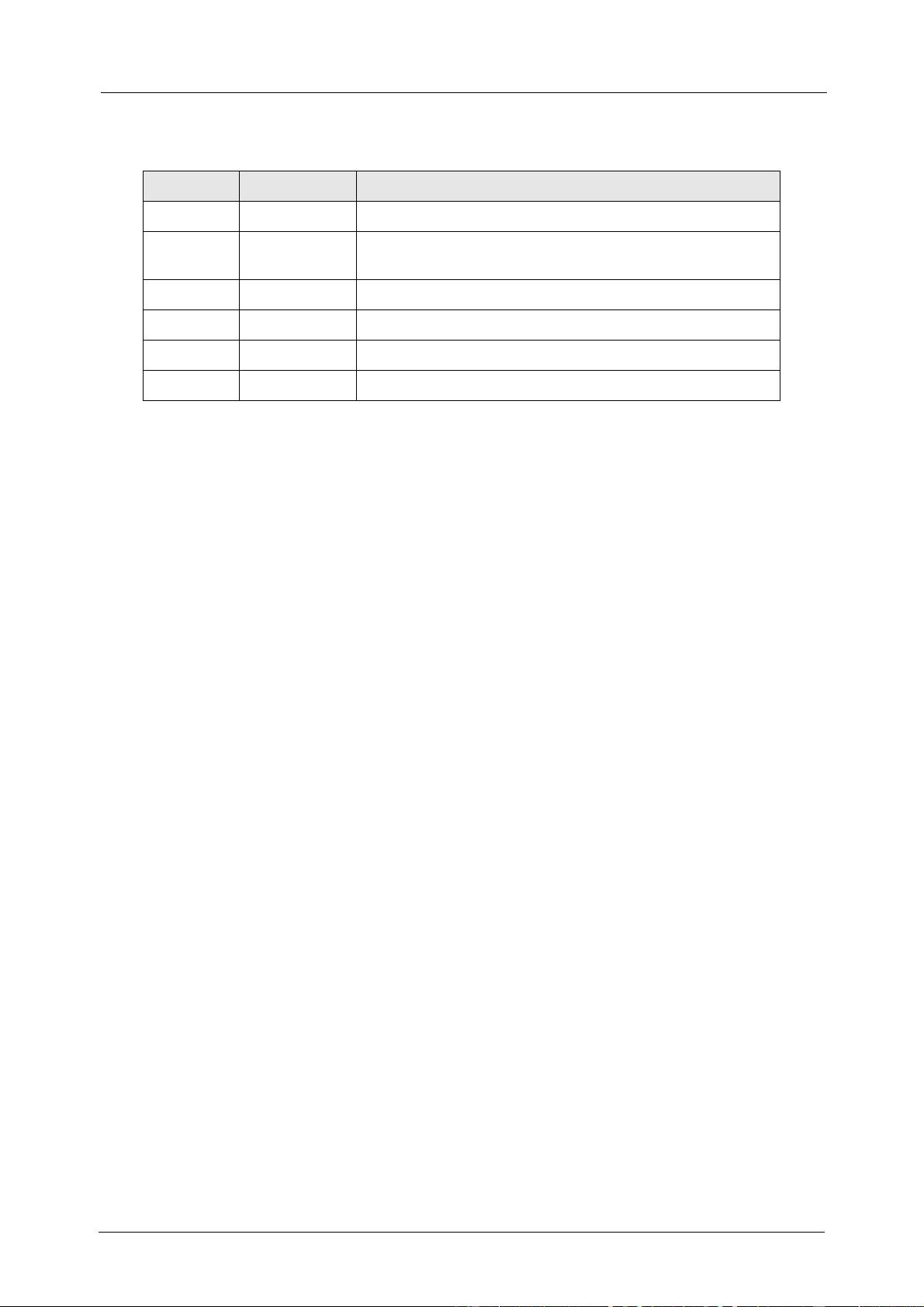

Version Date Notes

1.0 2003 Initial version.

2.0.1 23 apr 04 Updated for new EDA tool releases.

First design example (adder-subtractor) only.

2.0.2 26 may 04 Minor changes.

2.0.3 3 jun 04 Minor changes.

3.0.1 11 oct 05 Use Cadence Encounter as P&R tool.

3.0.2 6 dec 05 Minor issues fixed.

Top-down digital design flow / Table of Contents iii

AVx / version 3.0.2 / 6 Dec 2005

Table of Contents

Chapter 1: Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

1.1 Top-down design flow . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

1.2 EDA tools and design kit configuration . . . . . . . . . . . . . . . . . . . . . . . . . 3

1.3 Design project organisation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

1.4 Installation of the AMS design kit . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

1.5 VHDL example: Adder-subtractor . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

1.6 Text editing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

1.7 Design flow steps . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Chapter 2: VHDL and Verilog simulation . . . . . . . . . . . . . . . . . . . . . . . . . . .9

2.1 Starting the Modelsim graphical environment . . . . . . . . . . . . . . . . . . . . 9

2.2 Simulation of (pre-synthesis) RTL VHDL models . . . . . . . . . . . . . . . . . . .10

2.3 Simulation of the post-synthesis VHDL model with timing data . . . . . . . . .12

2.4 Simulation of the post-PaR Verilog model with timing data . . . . . . . . . . .14

Chapter 3: Logic synthesis . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

3.1 Starting the Design Vision graphical environment . . . . . . . . . . . . . . . . . .17

3.2 RTL VHDL model analysis . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18

3.3 Design elaboration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18

3.4 Design environment definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .19

3.5 Design constraint definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20

3.6 Design mapping and optimization . . . . . . . . . . . . . . . . . . . . . . . . . . . .21

3.7 Report generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .23

3.8 VHDL/Verilog gate-level netlist generation and post-synthesis timing data (SDF)

extraction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .26

3.9 Design constraints generation for placement and routing . . . . . . . . . . . . .28

3.10 Design optimization with tighter constraints . . . . . . . . . . . . . . . . . . . .28

3.11 Using scripts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .28

Chapter 4: Standard cell placement and routing . . . . . . . . . . . . . . . . . . . . . 33

4.1 Starting the Encounter graphical environment . . . . . . . . . . . . . . . . . . . .33

4.2 Design import . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .34

4.3 Global net connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .36

4.4 Operating conditions definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .37

4.5 Floorplan Specification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .37

4.6 CAP cell placement . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .38

4.7 Power ring/stripe creation and routing . . . . . . . . . . . . . . . . . . . . . . . .39

4.8 Core cell placement . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .41

4.9 Timing analysis . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .42

4.10 Clock tree synthesis (optional) . . . . . . . . . . . . . . . . . . . . . . . . . . . . .43

4.11 Design routing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .44

4.12 Timing analysis . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .45

4.13 Design checks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .45

4.14 Report generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .46

4.15 Post-route timing data extraction . . . . . . . . . . . . . . . . . . . . . . . . . . .47

4.16 Post-route netlist generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .47

4.17 GDS2 file generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .47

4.18 Design import in Virtuoso . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .48

4.19 Using scripts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .49

Top-down digital design flow 1

AVx / version 3.0.2 / 6 Dec 2005

Chapter 1: Introduction

This document details the typical steps of a top-down digital VHDL/Verilog design flow with the help of

one simple design example.

The following tools are considered in this document:

• Modelsim v6.1b or higher, from Mentor Graphics.

• Design Compiler and Design Vision 2005.09 or higher from Synopsys.

• Encounter 4.1, and IC 5.0.33 or higher from Cadence Design Systems.

The design kit used is the Hit-Kit 3.70 from AMS. The process is the 0.35 micron 4-metal CMOS called

C35B4.

Next chapters in this document are each addressing a specific set of tasks. Chapter 2 is about VHDL and

Verilog simulation, chapter 3 is about logic synthesis and chapter 4 is about place and route. Steps in these

chapters are not necessarily to be done in the given sequence. Go to “1.7 Design flow steps” to get a typical

sequence of steps.

1.1 Top-down design flow

Figure 1.1 illustrates the flow whose main steps are the following:

• VHDL RTL model creation

The goal here is to develop synthesizable VHDL models at the RTL level (RTL means Register-Transfer

Level). This means that there is a clear separation between control parts (e.g. finite state machines - FSM)

and operative parts (e.g. arithmetic and logic units). Registers are used to store small size data between

clock cycles. RAM/ROM memories are used to store large amounts of data or program code. Blocks such

as FSMs, ALUs, registers are usually described as behavioural models that do not imply any particular

gate-level implementation. Tools used at this step can range from simple text editors to dedicated graph-

ical environments that generate VHDL code automatically.

• RTL simulation

The VHDL RTL models are validated through simulation by means of a number of testbenches also

written in VHDL. The tool used at this step is a logic simulator (in our case, Modelsim).

• RTL synthesis

The synthesis process infers a possible gate-level realisation of the input RTL description that meets

user-defined constraints such as area, timings or power consumption. The design constraints are de-

fined outside the VHDL models by means of tool-specific commands. The targetted logic gates belong

to a library that is provided by a foundry or an IP company as part of a so-called design kit. Typical gate

libraries include a few hundreds of combinational and sequential logic gates. Each logic function is im-

plemented in several gates to accomodate several fanout capabilities or drive strengths. The gate library

剩余57页未读,继续阅读

资源评论

zhengyudennis

- 粉丝: 0

- 资源: 1

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功