没有合适的资源?快使用搜索试试~ 我知道了~

使用PlanAhead进行FPGA部分动态重配设计

温馨提示

试读

27页

部分重配置Partial Reconfiguration(PR)是一种动态修改逻辑模块的技术,通过在不妨碍其它逻辑运行的同时下载部分比特位文件来实现。

资源推荐

资源详情

资源评论

使用PlanAhead进行FPGA部分动态重配设计

目 录

1 概述 ....................................................................................................................................... 3

1.1 部分重配置技术的意义 ..................................................................................................... 3

1.2 支持部分重配置技术的软件与芯片 ................................................................................... 3

2 使用PlanAhead进行部分重配置设计 ...................................................................................... 3

2.1 逻辑设计,生成ngc文件 ................................................................................................... 3

2.1.1 设计顶层文件和可重配置文件 .................................................................................... 3

2.1.2 对各个设计文件综合生成ngc文件 ............................................................................... 4

2.2 使用PlanAhead工具进行部分重配置设计 ......................................................................... 5

2.2.1 新建PlanAhead工程。 ............................................................................................... 5

2.2.2 新建并添加部分可重配置模块 .................................................................................... 7

2.2.2.1 新建第一个可重配置部分U1_RP_led ................................................................ 7

2.2.2.2 添加第二个可重配置部分U2_RP_pulse ............................................................ 9

2.2.3 添加另外的可重配置模块 ......................................................................................... 11

2.2.3.1 添加一个可重配置模块到U1_RP_led .............................................................. 11

2.2.3.2 添加一个可重配置模块到U2_RP_pulse .......................................................... 12

2.2.4 划分可重配置模块的实现区域 .................................................................................. 14

2.2.4.1 为第一个可重配部分U1_RP_led划分物理区域 ................................................ 14

2.2.4.2 为第二个可重配部分U2_RP_pulse划分物理区域 ............................................ 16

2.2.5 添加时序约束 ........................................................................................................... 17

2.2.6 运行部分可重配置规则检查 ...................................................................................... 19

2.2.7 逻辑实现和促进布局 ................................................................................................. 20

2.2.7.1 实现配置config_1 ............................................................................................ 20

2.2.8 新建实现附加配置 .................................................................................................... 23

2.2.9 验证配置 .................................................................................................................. 25

2.2.10 生成和加载bit文件 ........................................................................................... 25

1

概

部

分

逻

辑

1.1 部

分

部

分

大

地

按

需

重

配

需

加

1.2 支

持

Xili

n

影

响

设

计

器

件

这

种

设

计

2

使

对F

P

个

可

置

设

2.1 逻

辑

2.1.1

在ise_to

p

配置模

块

图中clo

c

模块是

可

可替换

的

名字必

须

// black

b

module

r

(

input

input

概

述

分

重配置Par

t

辑

运行的同

时

分

重配置

技

分

重配置允

许

地

提高了 FP

需

加载功能

降

配

置可以让

设

加

载功能,

更

持

部分重

配

n

x公司的IS

E

响

其它器件

运

计

。为进一步

件

之后,后

继

种

成熟的特

性

计

装配、约

束

使

用 Plan

A

P

GA进行部

分

可

重配的文件

进

设

计。

辑

设计,

生

设计顶层

文

p

工程中输入

块

只声明端口

c

ks模块是固

定

可

重配置模

块

的

,比如实

现

须

全部一样,

b

ox definition

r

econ_block_

l

clk

rst

t

ial Reconfi

g

时

下载部分

比

技

术的意义

许

设计者在

系

GA 的灵活

性

降

低了动态

功

设

计人员采用

更

有效利用

芯

配

置技术的

软

E

® 12 中推

出

运

行的前提

下

扩大现有支

持

继

的版本支

持

性

,可以确保

束

、实现和

验

A

head

进

分

重配置设

计

进

行综合,

生

生

成ngc文

件

文

件和可

重

设计的顶层

文

,内部没有

具

定

设计模块,

块

,以黑盒子

的

现

led控制的多

个

都是recon_b

l

for reconfig

u

l

e

d

,

,

g

uration(P

R

比

特位文件来

统运行过程

性

。通过分

时

功

耗;通过时

分

更少或更小

芯

片。

软

件与芯

片

出

的现有软

件

下

对 Xilinx F

P

持

范围,继

持

Artix™-7

和

对预先生成

的

验

证。

进

行部分

重

时,主要包

括

生

成ngc文件;

件

重

配置文件

文

件top.v,

各

具

体实现,

顶

不可重配置,

的

形式出现,

个

可重配模

块

l

ock_le

d

。顶

u

rable module

R

)是一种

动

实现。

中修改功能

,

时

功能减少

了

分

多路复用

设

的器件,从

而

片

件

方法代表

了

P

GA 的部

分

Virtex-4、Vi

和

Virtex®-

7

的结果进行

准

重

配置设

计

括

2个方面的

设

二是使用P

l

各

可重配置模

块

顶

层文件的层

具有具体

的

只声明了端

块

recon_bloc

k

层文件的关

键

recon_block

_

动

态修改逻

辑

,

而无需全

面

了

FPGA

的

设

计功能提

高

而

降低功耗

并

了

部分重配

置

分

功能进行

重

rtex-5、 Vi

r

7

XT 器件。

准

确保存。

P

计

设

计:一是

使

l

anAhead工

具

块

必须是以

“

次图如下图

所

实现逻辑。r

e

口,内部没

有

k

_led,*.v文

件

键

设计代码

如

_

bra

m

模块的技术

面

重新配置

和

的

尺寸和数量

高

解决方案

的

并

提高系统

的

置

技术的新

时

重

配置的软件

t

ex-6、Virte

x

该当前解

决

P

lanAhead

设

使

用XST对设

计

具

,将生成的

n

“

黑盒子”的

所

示。

e

con_block_l

e

有

具体实现

逻

件

的名字可

以

如

下

,通过在不

妨

和

重新建立

连

量

(即成本)

的

灵活性 。

使

的

可升级性。

时

代。 这款

能

工具已被完

全

x

-7 T 和 Ki

决

方案通过

利

设

计环境可

用

计的顶层文

件

n

gc文件进行

部

的

形式出现,

既

e

d和recon_bl

o

逻

辑。设计时

注

以

不一样,但

妨

碍其它

连

接,极

;通过

使

用部分

随时按

能

够在不

全

重新

ntex™-7

利

用分区

用

于管理

件

以及各

部

分重配

既

各可重

o

ck_pulse

注

意,各

是

module

output

/*synthe

s

endmod

u

// black

b

module

r

(

input

input

output

/*sy

n

endmod

u

////////////

/

// Top-

l

////////////

/

module t

(

input

output

output

output

);

clocks U

(

.i_clk

.clk_out

);

recon_bl

o

(

.clk

.rst

.o_led

);

// instant

i

recon_bl

o

(

.clk

.rst

.o_pulse

);

2.1.2

使用XS

T

面的Ad

d

在使用

X

o_l

e

s

is syn_black

_

u

le

b

ox definition

r

econ_block_

p

clk

,

rst,

o_

p

n

thesis syn_bl

a

u

le

/

///////////////////

/

l

evel, static d

e

/

///////////////////

/

op

i_c

l

o_

t

e

o_

p

o_l

e

0_clocks

(i_c

l

(gcl

k

o

ck_led U1_

R

(gc

l

(rs

t

(o_

l

i

ate reconfig

u

o

ck_pulse U

2

(gc

l

(rs

t

(o_

p

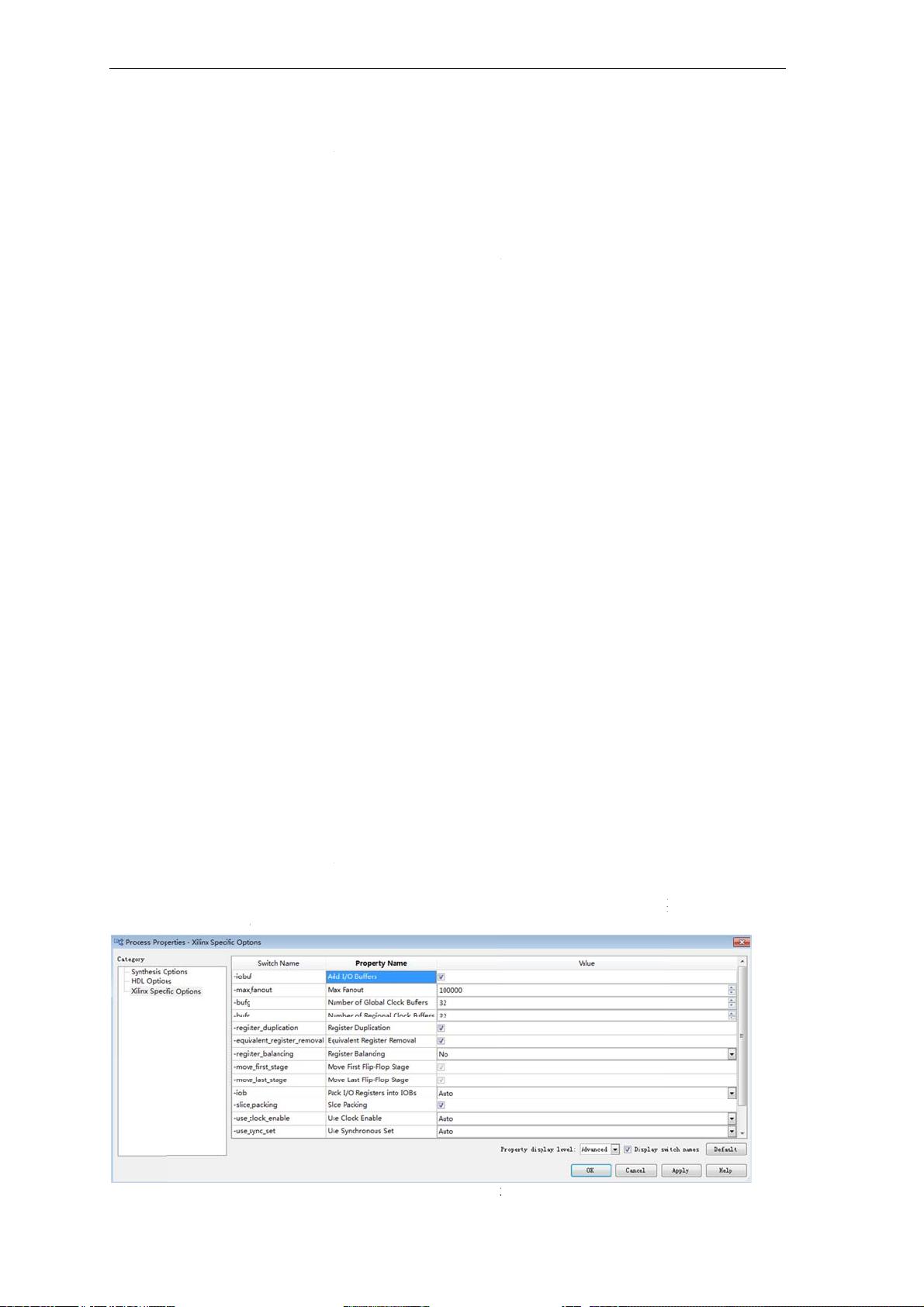

对各个设

计

T

对顶层文件

d

I/O Buffe

r

X

ST对可重配

e

d )

_

box*/;

for reconfig

u

p

ulse

,

p

ulse)

a

ck_box blac

k

/

//////////////////

/

e

sign

/

//////////////////

/

l

k

e

st

p

ulse

ed

l

k)

k

)

R

P_led

l

k)

t

)

l

ed)

u

rable module

2

_RP_pulse

l

k)

t

)

p

ulse)

计

文件综

合

和可重配置

文

r

s这个选项默

置文件进行

综

u

rable module

k

_box_pad_p

i

/

//////////////////

/

/

//////////////////

/

,

,

,

,

,

,

counte

r

,

,

合

生成ngc

文

文

件进行综

合

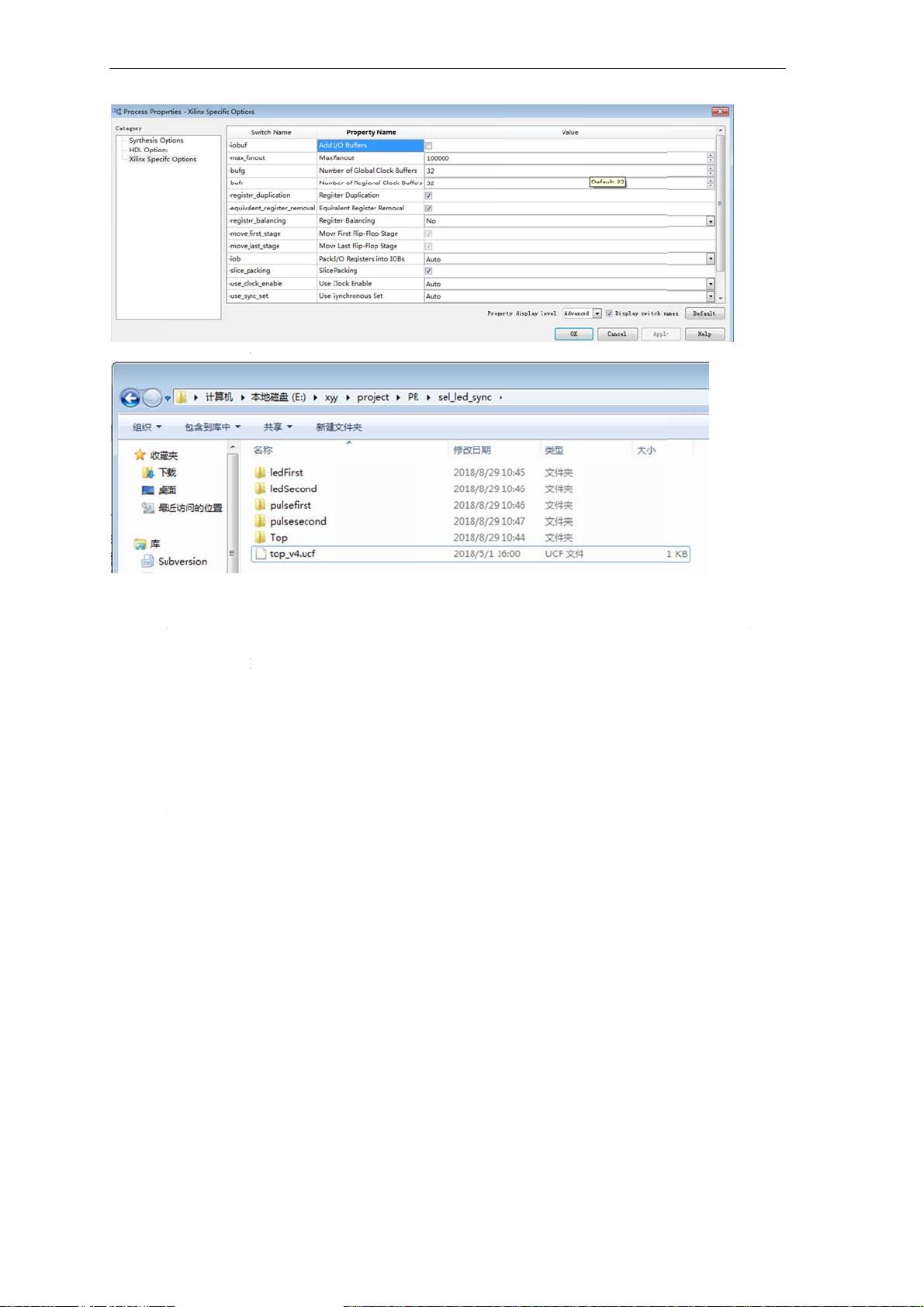

认设置是选

中

综

合生成ngc

文

recon_block

_

i

n="out_cou

n

/

///////

/

///////

文

件

合

,生成ngc

文

中

状态,如

下

文

件时,必须

将

_

counte

r

n

ter"*/;

文

件。在生成

n

下

图所示。

将

该选项不

选

n

gc文件时需

要

选

中,将后面

勾

要注意,综

合

勾

选框里面

的

合

选项里

的

√去掉,

如下图

所

依次将

顶

Top文

件

和ledSe

c

配置,

改

当Pulse

fi

是对应

的

2.2 使

用

2.2.1

1、 开

始

Pla

n

2、在C

r

3、在P

r

4、在S

p

Partial

R

所

示。

顶

层文件和

各

件

夹下面存的

是

c

on

d

是对同

一

改

成ledSecond

控

fi

rs

t

生效时,

D

的

管脚约束

文

用

PlanAh

e

新建Plan

A

始

>所有程序

n

Ahead工具。

r

eate a New

P

r

oject Nam

e

p

ecifythety

p

R

econfigurat

各

可重配置文

件

是

顶层文件

的

一

LED灯D21

进

控

制时,D21

灭

D

20闪,当

将

文

件。

e

ad工具进

行

A

head工程

> Xilinx De

s

选择Create

N

P

lanAhead

P

e

界面,设

置

p

eofprojec

t

ion,然后

点

件

综合生成n

g

的

ngc文件,

其

进

行可重配

置

灭

。Pulsefirst

和

将

该部分逻辑

部

行

部分重

配

。

s

ign Tools >

X

N

ew Projec

t

,

P

rojec

t

界面,

置

工程名字,

t

togreate

界

点

击Next。

如

g

c文件,放

在

其

他文件夹存

置

控制,当le

d

和

p

ulsesecon

d

部

分重配置,

配

置设计

X

ilinx ISE D

e

新建一个Pl

a

点击Next。

工程目录

,

界

面,选择P

o

如

下图所示

。

在

不同的文件

放的是可重

配

d

Firs

t

生效时,

d

是对另外一

改成

p

ulsese

c

e

sign Suite 14

a

nAhead工程

,

其他选项

默

o

st‐synthesi

s

夹下。如下

图

配

置逻辑的n

g

D21闪,当

将

个LED灯D2

0

c

on

d

控制时,

.

7 > PlanAhe

a

。

默

认,然后

s

Project选

项

图

所示

g

c文件。其

中

将

该部分逻

辑

0

进行可重配

置

D20常亮。t

o

a

d > PlanAhe

a

点Next。

项

,并勾选

E

中

ledFirst

辑

部分重

置

控制,

o

p_v4.ucf

a

d,打开

E

nable,

剩余26页未读,继续阅读

资源评论

tian_yi88882019-10-16内容挺详实的

tian_yi88882019-10-16内容挺详实的

FPGA_随风

- 粉丝: 7

- 资源: 35

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功