VHDL 32位超前进位加法器

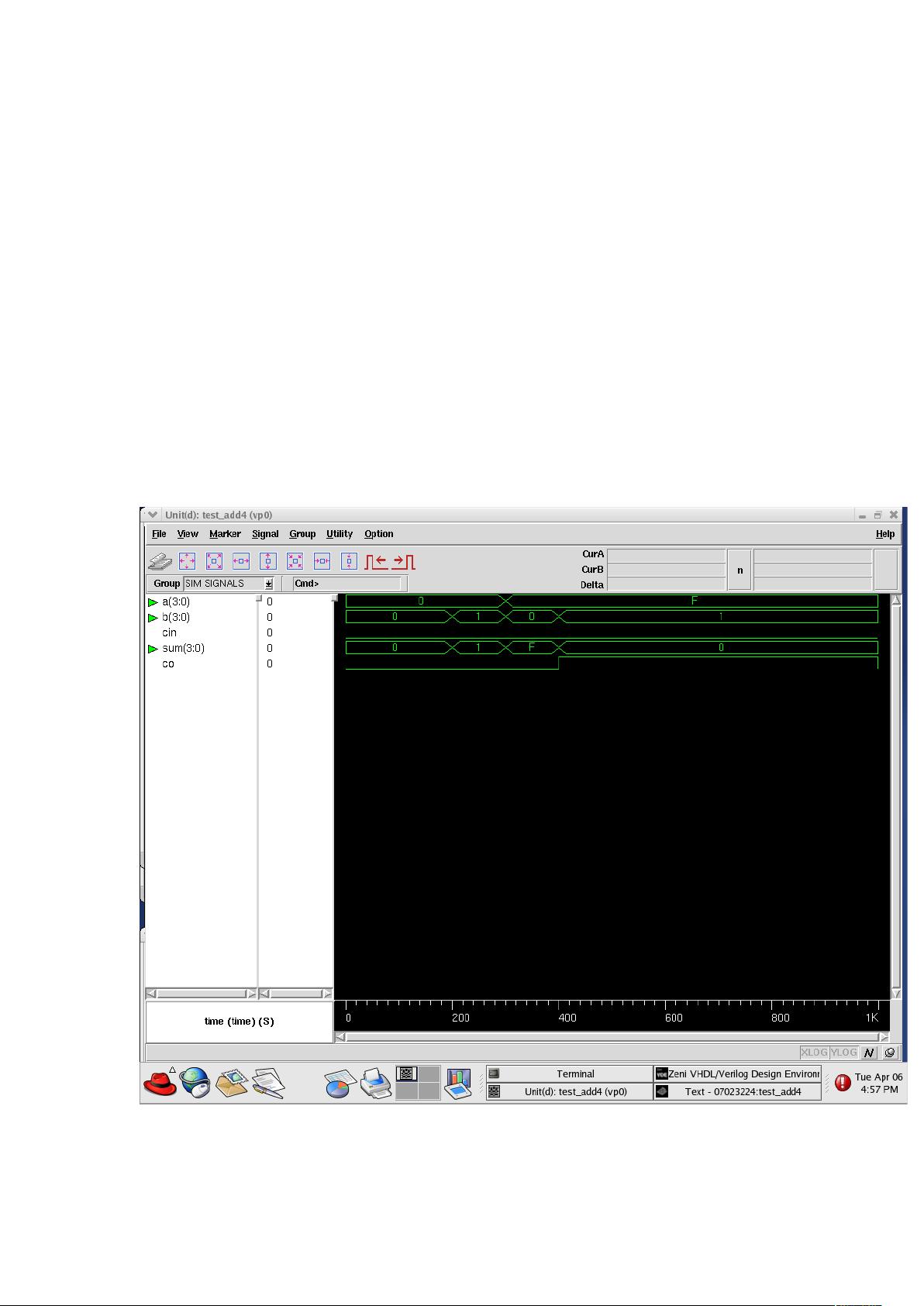

VHDL(VHSIC Hardware Description Language)是一种用于电子设计自动化领域的硬件描述语言,它允许工程师用编程的方式来描述数字系统的逻辑功能和行为。在给定的压缩包中,重点是32位超前进位加法器的设计,这是一种高级的算术逻辑单元(ALU)组成部分,用于快速执行二进制加法。 32位超前进位加法器是比传统全加器更高效的实现方式。在传统的加法器中,每一位都需要等待其左边位的进位计算完成才能进行运算,这会导致计算延迟。而超前进位加法器通过预计算和传播进位信号来减少这种延迟,提高了加法的速度。 "add4.vhd"和"add32.vhd"文件很可能是VHDL代码实现的4位和32位超前进位加法器。VHDL代码会定义实体(entity)来描述硬件接口,以及结构体(architecture)来实现其内部逻辑。例如,实体声明输入(如两个加数和进位输入)和输出(如和与进位输出),而结构体则使用逻辑门(如与门、或门和非门)和触发器等基本元件来描述如何计算这些值。 "test_add32.vhd"和"test_add4.vhd"则是针对上述加法器的测试程序,通常会用到VHDL的`IEEE Std 1076-2008`库中的`std_logic_1164`和`ieee.numeric_std`,通过过程(process)模拟输入信号的变化,并检查输出是否符合预期。这些测试程序确保了设计的正确性,并且可以在硬件仿真器或FPGA上验证其行为。 "Screenshot.png"和"Screenshotadd4.png"可能是电路图或者仿真结果的截图,展示了32位和4位超前进位加法器的逻辑布局或者运行时的波形图。这些图能直观地帮助理解设计的工作原理和性能。 这个压缩包提供了从理论到实践的完整学习资源,涵盖了32位超前进位加法器的设计、实现、测试以及可视化。通过学习和理解这些内容,你可以深入理解VHDL语言,以及如何使用它来设计高性能的数字逻辑系统。同时,这也涉及到数字逻辑设计的基础,包括进位逻辑、并行计算和硬件验证技术,这些都是现代计算机体系结构和集成电路设计中的核心概念。

VHDL adder32.rar (8个子文件)

VHDL adder32.rar (8个子文件)  add4.vhd 2KB

add4.vhd 2KB test_add32.vhd 805B

test_add32.vhd 805B add32.vhd 4KB

add32.vhd 4KB Screenshot.png 53KB

Screenshot.png 53KB Doc1.doc 69KB

Doc1.doc 69KB Screenshotadd4.png 43KB

Screenshotadd4.png 43KB test_add4.vhd 749B

test_add4.vhd 749B VHDL 32位超前进位加法器.doc 165KB

VHDL 32位超前进位加法器.doc 165KB- 1

- 粉丝: 35

- 资源: 2

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功

- 1

- 2

前往页