TLE4473G V53 英飞凌芯片 INFINEON 中文版规格书手册.pdf

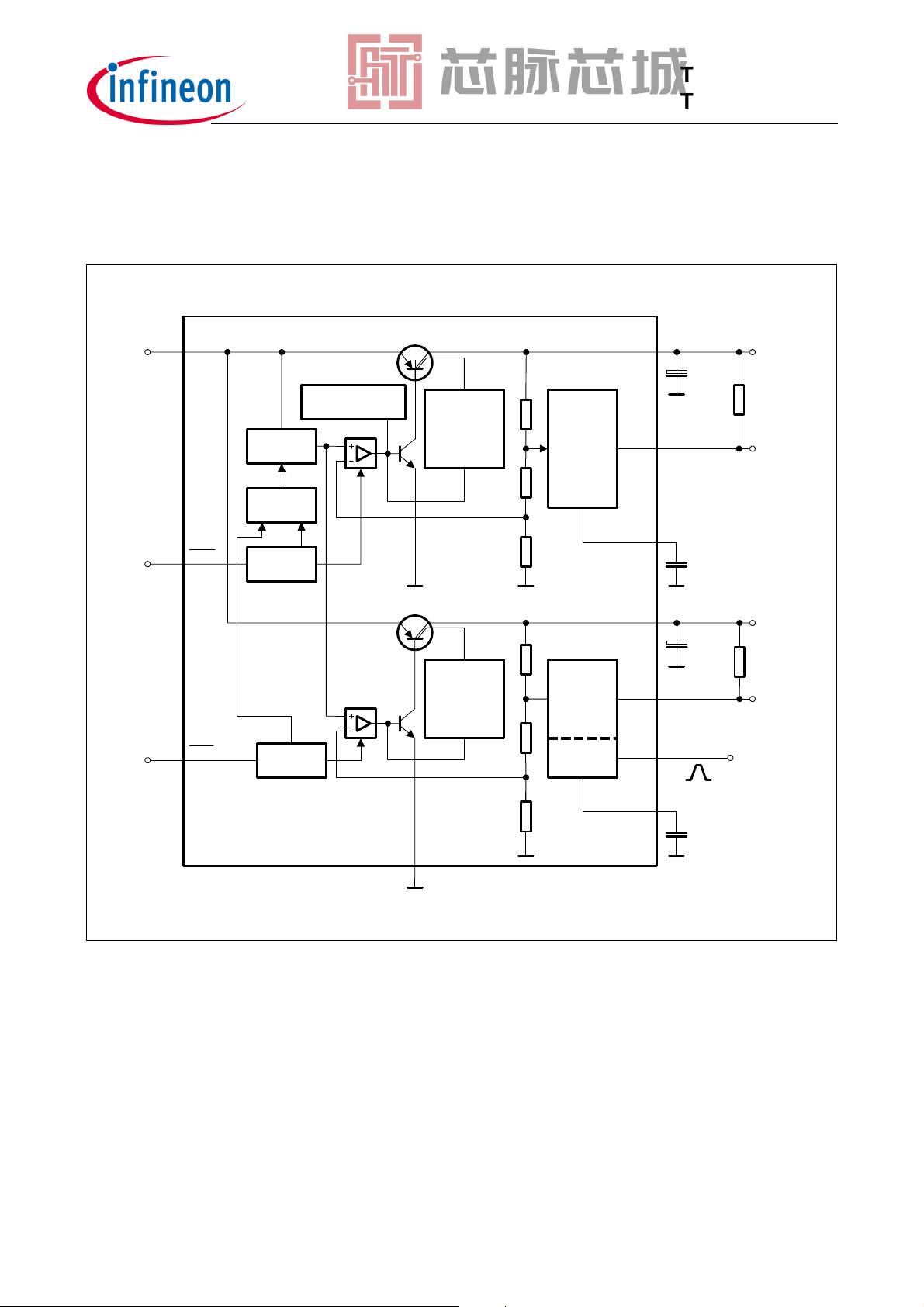

英飞凌的TLE4473G V53是一款双路低压降电压调节器,设计用于汽车应用中的微处理器系统和传感器供电。该芯片在极端条件下表现出色,具有多种保护功能,包括过载、短路和过温保护。以下是关于这款芯片的详细解释: 1. 输出电流和电压: TLE4473G V53提供了两个独立的输出。输出1可提供300mA的电流,电压为3.3V(±3%)或2.6V(±3%),而输出2则提供180mA的电流,电压为5V(±2%)。这使得该芯片能够满足不同负载的需求。 2. 低静态电流消耗: 当两个输出都关闭时,芯片的静态电流消耗小于1微安,有助于降低应用的整体功耗。 3. 工作电压范围: TLE4473G V53能在5.6V至45V的输入电压范围内工作,这使其适用于广泛的电源条件。 4. 极低的压降: 这款芯片的一大特点是其非常低的压降,即使在高负载下也能保持高效的电压转换。 5. 独立的禁用功能: 每个输出都可以单独启用或禁用,允许灵活的电源管理,从而进一步降低功耗。 6. 保护功能: 芯片内置了两个独立的复位电路和一个看门狗定时器,用于监控微控制器。此外,还有针对过载、短路和过温的保护机制,确保系统在异常情况下的稳定性和可靠性。 7. 宽温度范围: TLE4473G V53可在-40°C到150°C的结温范围内正常工作,适应各种恶劣环境。 8. 外部组件: 图1显示了芯片的典型外部组件配置,包括复位发生器、电流和饱和控制以及过电流保护,这些组件帮助实现芯片的功能并增强其性能。 9. 数据手册参考: 用户可以参考TLE4473GV53的数据手册,了解更详细的电气特性、应用电路图、封装信息和推荐的使用方法。 总结来说,英飞凌的TLE4473G V53是一款高性能、低功耗的双路低压降稳压器,特别适合对电源效率和稳定性有高要求的汽车电子应用。其内置的保护机制和灵活的电源管理功能使其在严苛环境中表现出卓越的性能。

剩余15页未读,继续阅读

- 粉丝: 4

- 资源: 4030

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 获取光敏电阻测量值并探索运动检测算法Matlab代码.rar

- 基于 Potts 模型的向量值图像多标签图像分割Matlab代码.rar

- 基于 YCbCr 颜色模型的基于图像处理的森林火灾探测Matlab代码.rar

- 基于局部最大值和最小值分析的连续时间动力学系统的分岔图Matlab代码.rar

- 基于色度的道路跟踪系统 Matlab 代码.rar

- 计算阿特金森循环的各种压力和温度Matlab代码.rar

- 基于运动估计的 3D 视频去噪的简单时间滤波器Matlab代码.rar

- 计算第二类斯特林数Matlab代码.rar

- 计算二元系统液体和蒸汽成分以及闪蒸过程中的温度Matlab代码.rar

- 计算点云的振荡剪切指数的函数Matlab代码.rar

- 静态霍夫曼编码和解码;用于文本压缩的自适应 Huffman 编码和解码Matlab代码.rar

- 将具有延迟的连续时间模型转换为具有扩展状态向量的离散状态空间模型Matlab代码.rar

- 检测彩色图像中的人脸Matlab代码.rar

- 使用 FCD 方法实时高精度地跟踪棋盘格图案中的光学畸变Matlab代码.rar

- 使用 GAUSS-SEIDEL 方法进行潮流分析的程序Matlab代码.rar

- 使用 lsqnonlin 的光束法平差Matlab代码.rar

信息提交成功

信息提交成功