4

DRA710

,

DRA712

DRA714, DRA716, DRA718

ZHCSII1F –JUNE 2016–REVISED MAY 2019

www.ti.com.cn

内容

版权 © 2016–2019, Texas Instruments Incorporated

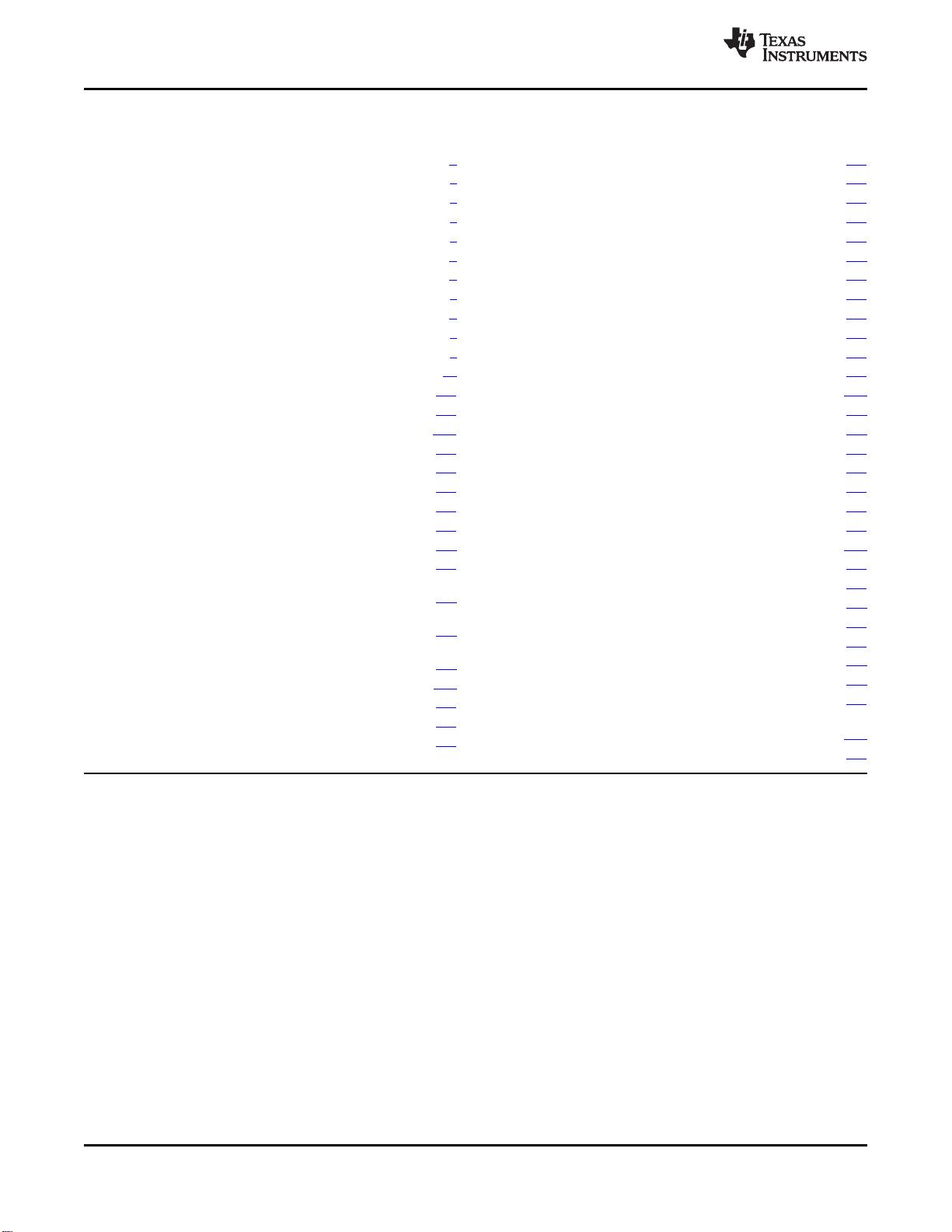

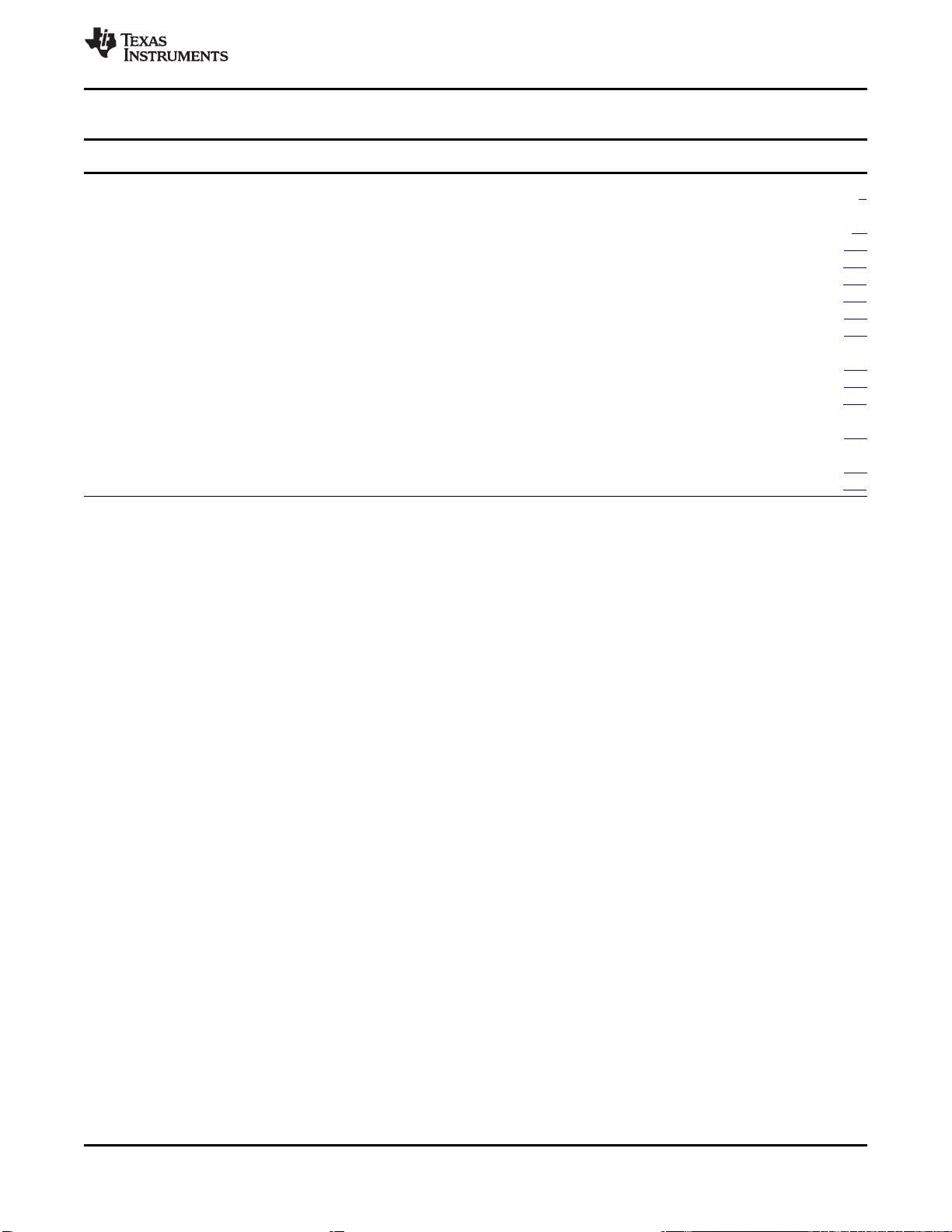

内内容容

1 器器件件概概述述 .................................................... 1

1.1 特性 ................................................... 1

1.2 应用 ................................................... 2

1.3 说明 ................................................... 2

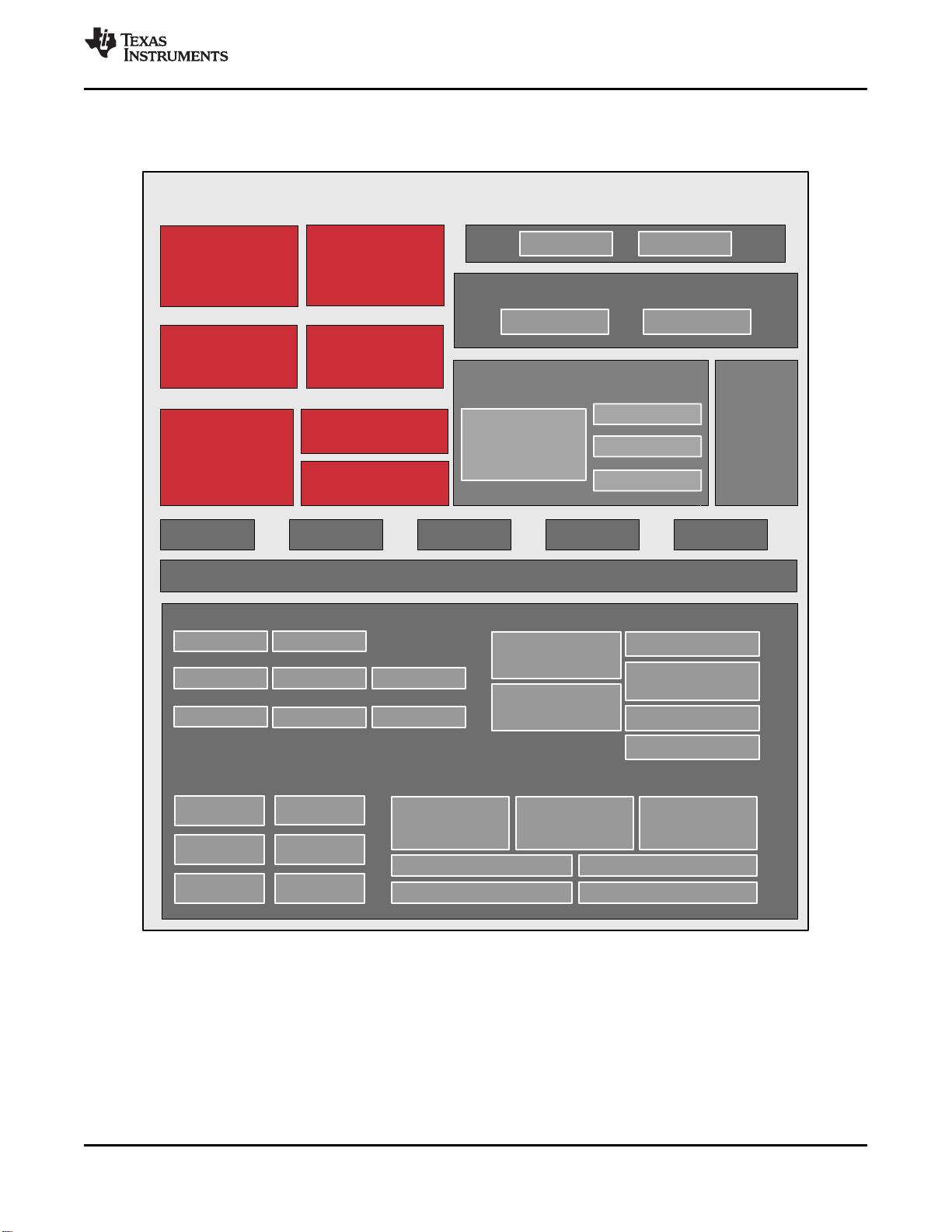

1.4 功能方框图 ........................................... 3

2 修修订订历历史史记记录录............................................... 5

3 Device Comparison ..................................... 6

3.1 Related Products ..................................... 8

4 Terminal Configuration and Functions.............. 9

4.1 Pin Diagram .......................................... 9

4.2 Pin Attributes ......................................... 9

4.3 Signal Descriptions.................................. 68

4.4 Pin Multiplexing .................................... 106

4.5 Connections for Unused Pins...................... 120

5 Specifications ......................................... 121

5.1 Absolute Maximum Ratings........................ 122

5.2 ESD Ratings ....................................... 123

5.3 Power on Hours (POH) Limits ..................... 123

5.4 Recommended Operating Conditions ............. 123

5.5 Operating Performance Points..................... 126

5.6 Power Consumption Summary .................... 146

5.7 Electrical Characteristics........................... 146

5.8 VPP Specifications for One-Time Programmable

(OTP) eFuses ...................................... 154

5.9 Thermal Resistance Characteristics for CBD

Package............................................ 155

5.10 Timing Requirements and Switching

Characteristics ..................................... 157

6 Detailed Description.................................. 331

6.1 Description ......................................... 331

6.2 Functional Block Diagram ......................... 331

6.3 MPU................................................ 333

6.4 DSP Subsystem ................................... 336

6.5 IVA ................................................. 340

6.6 IPU ................................................. 340

6.7 GPU................................................ 341

6.8 BB2D............................................... 343

6.9 PRU-ICSS.......................................... 344

6.10 Memory Subsystem................................ 345

6.11 Interprocessor Communication .................... 348

6.12 Interrupt Controller ................................. 349

6.13 EDMA .............................................. 350

6.14 Peripherals ......................................... 351

6.15 On-chip Debug..................................... 368

7 Applications, Implementation, and Layout ...... 371

7.1 Introduction ........................................ 371

7.2 Power Optimizations ............................... 372

7.3 Core Power Domains .............................. 383

7.4 Single-Ended Interfaces ........................... 394

7.5 Differential Interfaces .............................. 396

7.6 Clock Routing Guidelines .......................... 415

7.7 DDR3 Board Design and Layout Guidelines....... 415

8 Device and Documentation Support.............. 439

8.1 Device Nomenclature .............................. 439

8.2 Tools and Software ................................ 441

8.3 Documentation Support............................ 442

8.4 Related Links ...................................... 442

8.5 Community Resources............................. 442

8.6 商标 ................................................ 443

8.7 静电放电警告....................................... 443

8.8 Glossary............................................ 443

9 Mechanical, Packaging, and Orderable

Information............................................. 444

9.1 Packaging Information ............................. 444

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜

信息提交成功

信息提交成功