没有合适的资源?快使用搜索试试~ 我知道了~

TI-TVP5154A.pdf

需积分: 10 0 下载量 182 浏览量

2022-12-04

00:02:33

上传

评论 4

收藏 1.08MB PDF 举报

温馨提示

试读

93页

TI-TVP5154A.pdf

资源推荐

资源详情

资源评论

TVP5154A

www.ti.com

SLES214C–DECEMBER 2007–REVISED SEPTEMBER 2010

4-Channel Low-Power PAL/NTSC/SECAM Video Decoder

With Independent Scalers and Fast Lock

Check for Samples: TVP5154A

1 Introduction

1.1 Features

1

• Four Separate Video Decoder Channels With • Internal Phase-Locked Loop (PLL) for

Features for Each Channel: Line-Locked Clock (Separate for Each Channel)

and Sampling

– Accept NTSC (J, M, 4.43), PAL (B, D, G, H, I,

M, N, Nc), and SECAM (B, D, G, K, K1, L) • Sub-Carrier Genlock Output for Synchronizing

Video Color Sub-Carrier of External Encoder

– Support ITU-R BT.601 Standard Sampling • Standard Programmable Video Output Format

– High-Speed 9-Bit Analog-to-Digital Converter – ITU-R BT.656, 8-Bit 4:2:2 With Embedded

(ADC) Syncs

– Two Composite Inputs or One S-Video Input – 8-Bit 4:2:2 With Discrete Syncs

(for Each Channel)

• Advanced Programmable Video Output

– Fully Differential CMOS Analog Formats

Preprocessing Channels With Clamping and

– 2× Over-Sampled Raw Vertical Blanking

Automatic Gain Control (AGC) for Best

Interval (VBI) Data During Active Video

Signal to Noise (SNR) Performance

– Sliced VBI Data During Horizontal Blanking

– Brightness, Contrast, Saturation, Hue, and

or Active Video

Sharpness Control Through Inter-Integrated

• VBI Modes Supported:

Circuit (I

2

C)

– Teletext (NABTS, WST)

– Complementary 4-Line (3-H Delay) Adaptive

– Closed-Caption Decode With FIFO, and

Comb Filters for Both Cross-Luminance and

Extended Data Services (EDS)

Cross-Chrominance Noise Reduction

– Wide Screen Signaling (WSS), Video

– Patented Architecture for Locking to Weak,

Program System (VPS), Copy Generation

Noisy, or Unstable Signals

Management System (CGMS), Vertical

• Four Independent Polymorphic Scalers

Interval Time Code (VITC)

• Single or Concurrent Scaled and Unscaled

– Gemstar 1×/2× Electronic Program Guide

Outputs Via Dual Clocking Data, Interleaved

Compatible Mode

54-MHz Data or Single 27-MHz Clock

– Custom Configuration Mode Allows User to

• Scaled/Unscaled Image Toggle Mode Gives

Program the Slice Engine for Unique VBI

Variable Field Rate for Both Scaled and

Data Signals

Unscaled Video

• Improved Fast Lock Mode Can Be Used When

• Low Power Consumption: 700 mW Typical

Input Video Standard Is Known and Signals on

• 128-Pin Thin Quad Flat Pack (TQFP) Package

Switching Channels Are Clean

• Single 14.31818-MHz Crystal for All Standards

• Four Possible I

2

C Addresses Allowing 16

and All Channels

Decoder Channels on a Single I

2

C Bus

• Available in Commercial (0°C to 70°C) and

Industrial (–40°C to 85°C) Temperature Ranges

1.2 Description

The TVP5154A device is a 4-channel, low-power, NTSC/PAL/SECAM video decoder. Available in a

space-saving 128-pin thin quad flat pack (TQFP) package, each channel of the TVP5154A decoder

converts NTSC, PAL, or SECAM video signals to 8-bit ITU-R BT.656 format. Discrete syncs are also

1

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas

Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCTION DATA information is current as of publication date.

Copyright © 2007–2010, Texas Instruments Incorporated

Products conform to specifications per the terms of the Texas

Instruments standard warranty. Production processing does not

necessarily include testing of all parameters.

TVP5154A

SLES214C–DECEMBER 2007–REVISED SEPTEMBER 2010

www.ti.com

available. All four channels of the TVP5154A are independently controllable. The decoders share one

crystal for all channels and for all supported standards. The TVP5154A can be programmed using a single

inter-integrated circuit (I

2

C) serial interface. The decoder uses a 1.8-V supply for its analog and digital

supplies, and a 3.3-V supply for its I/O. The optimized architecture of the TVP5154A decoder allows for

low power consumption. The decoder consumes less than 720 mW of power in typical operation.

Each channel of the TVP5154A is an independent video decoder with a programmable polymorphic

scaler. Each channel converts baseband analog video into digital YCbCr 4:2:2 component video, which

can then be scaled down to any resolution to 1/256 vertical and 15-bit horizontal in 2-pixel decrements.

Composite and S-video inputs are supported. Each channel includes one 9-bit analog-to-digital converter

(ADC) with 2× sampling. Sampling is ITU-R BT.601 (27.0) MHz, generated from a single 14.31818-MHz

crystal or oscillator input) and is line locked. The output formats can be 8-bit 4:2:2 with discrete syncs or

8-bit ITU-R BT.656 with embedded synchronization.

The TVP5154A utilizes Texas Instruments patented technology for locking to weak, noisy, or unstable

signals. A real-time control (RTC) output is generated for each channel for synchronizing downstream

video encoders.

Complementary 4-line adaptive comb filtering is available per channel for both the luma and chroma data

paths to reduce both cross-luma and cross-chroma artifacts. A chroma trap filter also is available.

An improved fast lock mode can be used when the input video standard is known and the signals on the

switching channels are clean. Note, switching from snow and/or noisy channels to good channels takes

longer. In fast lock mode, video lock is achieved in three fields or less.

Video characteristics, including hue, contrast, brightness, saturation, and sharpness, may be

independently programmed for each channel using the industry standard I

2

C serial interface. The

TVP5154A generates synchronization, blanking, lock, and clock signals in addition to digital video outputs

for each channel. The TVP5154A includes methods for advanced vertical blanking interval (VBI) data

retrieval. The VBI data processor slices, parses, and performs error checking on teletext, closed caption,

and other data in several formats.

I

2

C commands can be sent to one or more decoder cores simultaneously, reducing the amount of I

2

C

activity necessary to configure each core. A register controls which decoder core receives I

2

C commands,

and can be configured such that all four decoders receive commands at the same time.

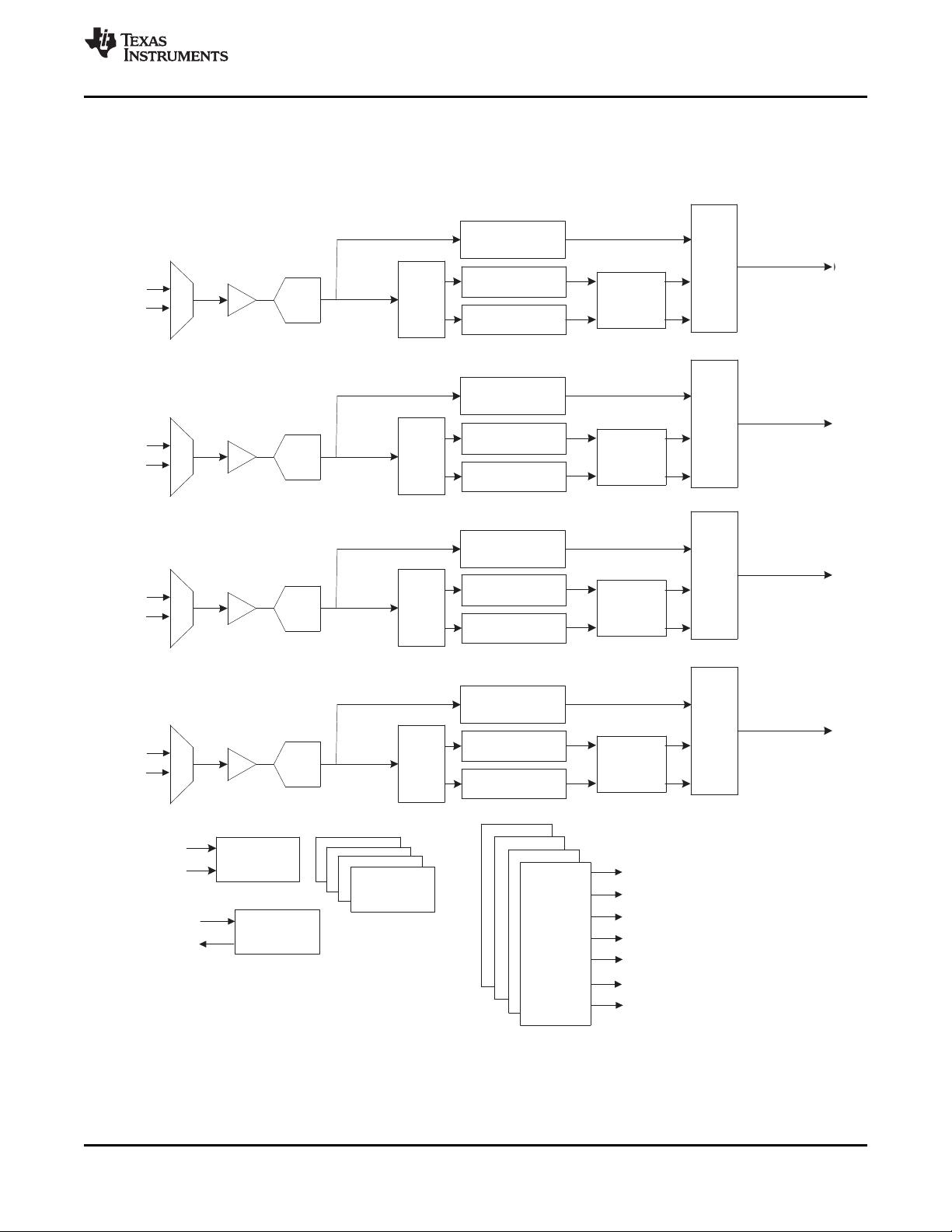

The main blocks for each of the channels of the TVP5154A decoder include:

• Robust sync detector

• ADC with analog processor

• Y/C separation using 4-line adaptive comb filter

• Independent, concurrent scaler outputs

• Chrominance processor

• Luminance processor

• Video clock/timing processor and power-down control

• I

2

C interface

• VBI data processor

1.3 Applications

• Security/Surveillance Digital Video Recorders/Servers and PCI Products

• Automotive Infotainment Video Hub

• Large-Format Video Wall Displays

• Games Systems

2 Introduction Copyright © 2007–2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): TVP5154A

TVP5154A

www.ti.com

SLES214C–DECEMBER 2007–REVISED SEPTEMBER 2010

1.4 Related Products

• TVP5150AM1

• TVP5151

• TVP5146M2

• TVP5147M1

• TVP5158

1.5 Trademarks

PowerPAD is a trademark of Texas Instruments.

Macrovision is a trademark of Macrovision Corporation.

Gemstar is a trademark of Gemstar-TV Guide International.

Other trademarks are the property of their respective owners.

1.6 Document Conventions

Throughout this data manual, several conventions are used to convey information. These conventions are:

• To identify a binary number or field, a lower case b follows the numbers. For example: 000b is a 3-bit

binary field.

• To identify a hexadecimal number or field, a lower case h follows the numbers. For example: 8AFh is a

12-bit hexadecimal field.

• All other numbers that appear in this document that do not have either a b or h following the number

are assumed to be decimal format.

• If the signal or terminal name has a bar above the name (for example, RESETB), then this indicates

the logical NOT function. When asserted, this signal is a logic low, 0, or 0b.

• RSVD indicates that the referenced item is reserved.

1.7 Ordering Information

PACKAGED DEVICES

(1)

T

A

PACKAGE OPTION

128-PIN TQFP PowerPAD™

TVP5154APNP Tray

0°C to 70°C

TVP5154APNPR Tape and reel

TVP5154AIPNP Tray

–40°C to 85°C

TVP5154AIPNPR Tape and reel

(1) For the most current package and ordering information, see the Package Option Addendum at the end

of this document, or see the TI web site at www.ti.com.

Copyright © 2007–2010, Texas Instruments Incorporated Introduction 3

Submit Documentation Feedback

Product Folder Link(s): TVP5154A

TVP5154A

SLES214C–DECEMBER 2007–REVISED SEPTEMBER 2010

www.ti.com

1 Introduction .............................................. 1

3.15 Clock and Data Control ............................. 18

1.1 Features .............................................. 1 4 I

2

C Host Interface ...................................... 19

1.2 Description ........................................... 1 4.1 I

2

C Write Operation ................................. 20

4.2 I

2

C Read Operation ................................. 20

1.3 Applications .......................................... 2

5 Clock Circuits .......................................... 22

1.4 Related Products ..................................... 3

6 Genlock Control and RTC ........................... 23

1.5 Trademarks .......................................... 3

6.1 TVP5154A Genlock Control Interface .............. 23

1.6 Document Conventions .............................. 3

6.2 RTC Mode .......................................... 23

1.7 Ordering Information ................................. 3

6.3 Reset and Power Down ............................ 24

2 Device Details ............................................ 5

6.4 Reset Sequence .................................... 25

2.1 Functional Block Diagram ............................ 5

7 Internal Control Registers ........................... 26

2.2 Terminal Diagram .................................... 6

7.1 Overview ............................................ 26

2.3 Terminal Functions ................................... 7

7.2 Direct Register Definitions .......................... 29

3 Functional Description ................................. 9

7.3 Indirect Register Definitions ........................ 75

3.1 Analog Front End .................................... 9

8 Scaler Configuration .................................. 79

3.2 Composite Processing Block Diagram ............... 9

8.1 Overview ............................................ 79

3.3 Adaptive Comb Filtering ............................ 10

8.2 Horizontal Scaling .................................. 79

3.4 Color Low-Pass Filter ............................... 11

8.3 Vertical Scaling ..................................... 80

3.5 Luminance Processing ............................. 11

8.4 Field Interleaving ................................... 81

9 Electrical Specifications ............................. 82

3.6 Chrominance Processing ........................... 11

9.1 Absolute Maximum Ratings ........................ 82

3.7 Timing Processor ................................... 11

9.2 Recommended Operating Conditions .............. 82

3.8 VBI Data Processor ................................ 12

9.3 Reference Clock Specifications .................... 82

3.9 VBI FIFO and Ancillary Data in Video Stream ..... 13

9.4 Electrical Characteristics ........................... 83

3.10 Raw Video Data Output ............................ 14

9.5 Timing Requirements ............................... 84

3.11 Output Formatter ................................... 14

9.6 I

2

C Host Port Timing ................................ 85

3.12 Synchronization Signals ............................ 14

9.7 Thermal Specifications ............................. 85

3.13 Active Video (AVID) Cropping ...................... 15

10 Schematic ............................................... 86

3.14 Embedded Syncs ................................... 17

11 Revision History ....................................... 87

4 Contents Copyright © 2007–2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): TVP5154A

M

U

X

M

U

X

M

U

X

M

U

X

AIP1A

AIP1B

AIP2A

AIP2B

AIP3A

AIP3B

AIP4A

AIP4B

PGA

PGA

PGA

PGA

9−Bit

A/D

9−Bit

A/D

9−Bit

A/D

9−Bit

A/D

Y/C

VBI Data

Processor (VDP)

Luminance

Processing

Chrominance

Processing

Scaler

Scaler

Scaler

Scaler

Output Formatter

CH1_OUT [7:0]

YC

B

C

R

8−Bit 4:2:2

CH2_OUT [7:0]

YC

B

C

R

8−Bit 4:2:2

CH3_OUT [7:0]

YC

B

C

R

8−Bit 4:2:2

CH4_OUT [7:0]

YC

B

C

R

8−Bit 4:2:2

SCL

SDA

XIN/OSC

XOUT

Horizontal and

Color PLLs

Host

Interface

Embedded

Processor

Timing Processor

FID/GLCO[1−4]

VSYNC/PAL[1−4]

INTERQ/GPCL/BLK[1−4]

HSYNC[1−4]

AVID[1−4]

CLK[1−4]

SCLK[1−4]

Y/CY/CY/C

Separation

Separation Separation Separation

Output Formatter Output Formatter Output Formatter

Luminance

Processing

Chrominance

Processing

Luminance

Processing

Chrominance

Processing

Luminance

Processing

Chrominance

Processing

VBI Data

Processor (VDP)

VBI Data

Processor (VDP)

VBI Data

Processor (VDP)

TVP5154A

www.ti.com

SLES214C–DECEMBER 2007–REVISED SEPTEMBER 2010

2 Device Details

2.1 Functional Block Diagram

Figure 2-1. Functional Block Diagram

Copyright © 2007–2010, Texas Instruments Incorporated Device Details 5

Submit Documentation Feedback

Product Folder Link(s): TVP5154A

剩余92页未读,继续阅读

资源评论

不觉明了

- 粉丝: 3101

- 资源: 5337

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 农村信用社联合社计算机信息系统投产与变更管理办.docx

- 农村信用社联合社计算机信息系统数据管理办法.docx

- 利用SPSS作临床效度分析线上计算网站介绍-医学研究部统计谘.(医学PPT课件).ppt

- 利用Zabbix监控mysqldump定时备份数据库状态.docx

- 利用计算机解决问题的基本过程.doc

- 化工铁路通信工程总结.doc

- 北京大学网络教育软件工程作业.docx

- 医药公司(连锁店)计算机操作规程未新系统的自行按照旧制修改-新系统过制的编号加修模版.doc

- 医药公司(连锁店)计算机系统操作规程模版.doc

- 医药连锁门店计算机系统的操作和管理程序未新系统的自行按照旧制修改-新系统过制的编号加修模版.docx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功