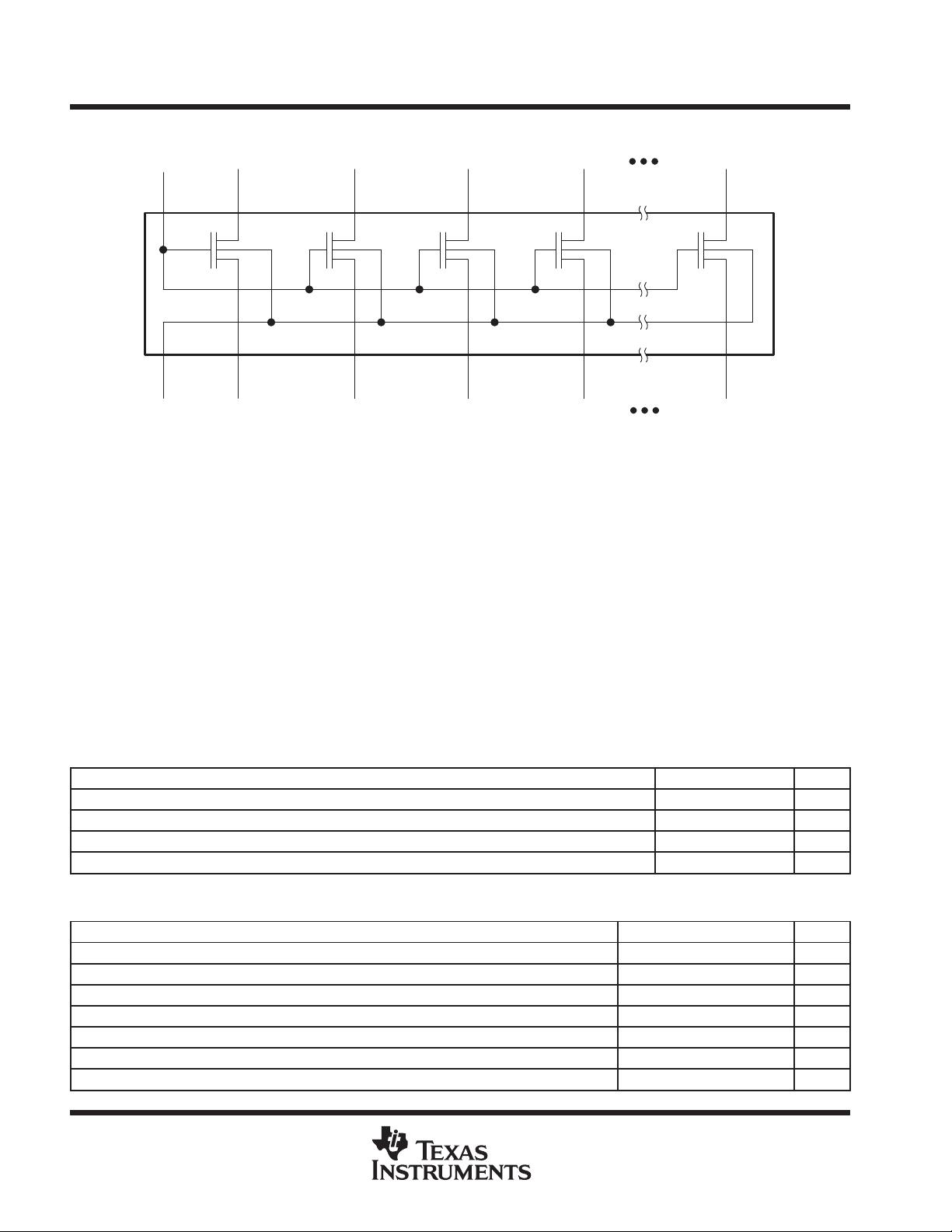

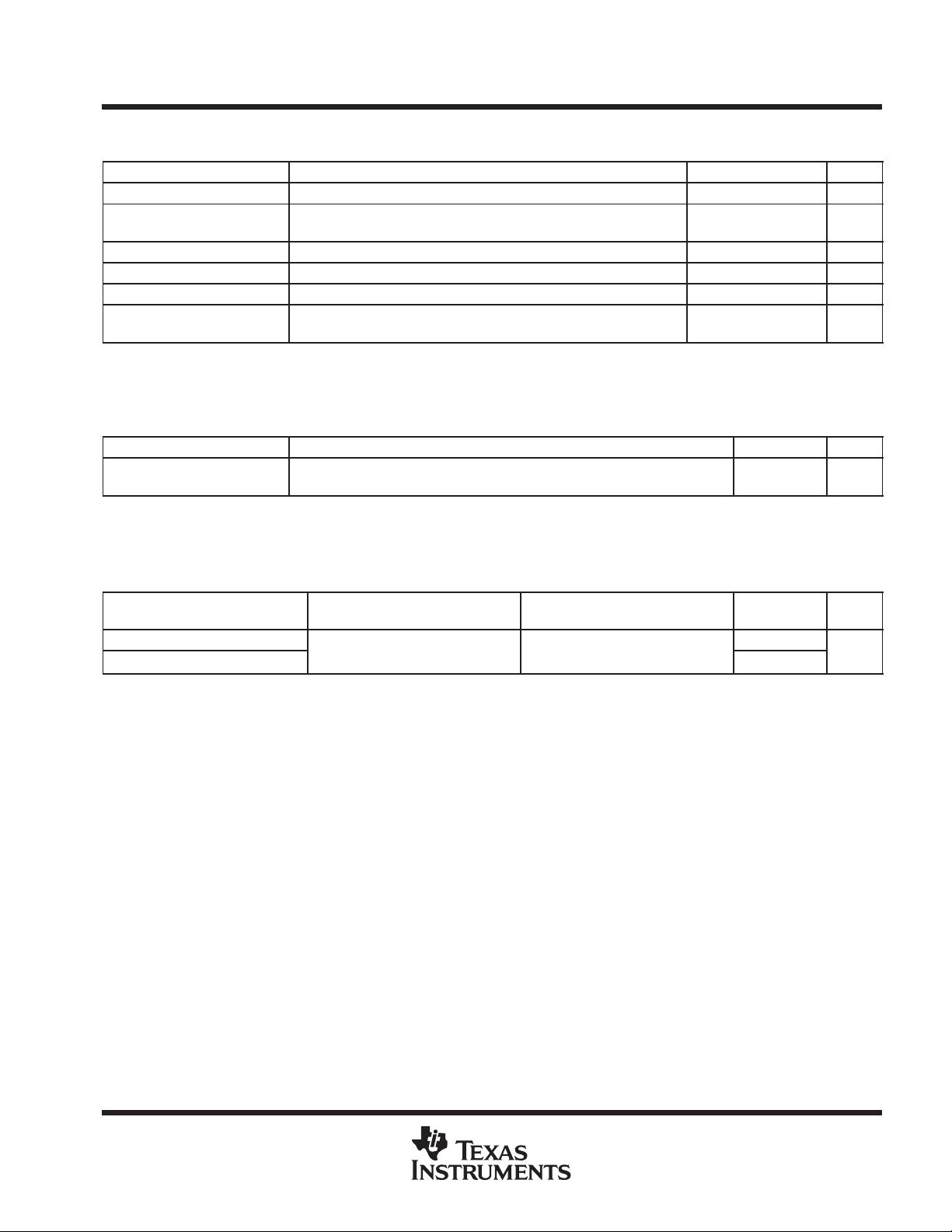

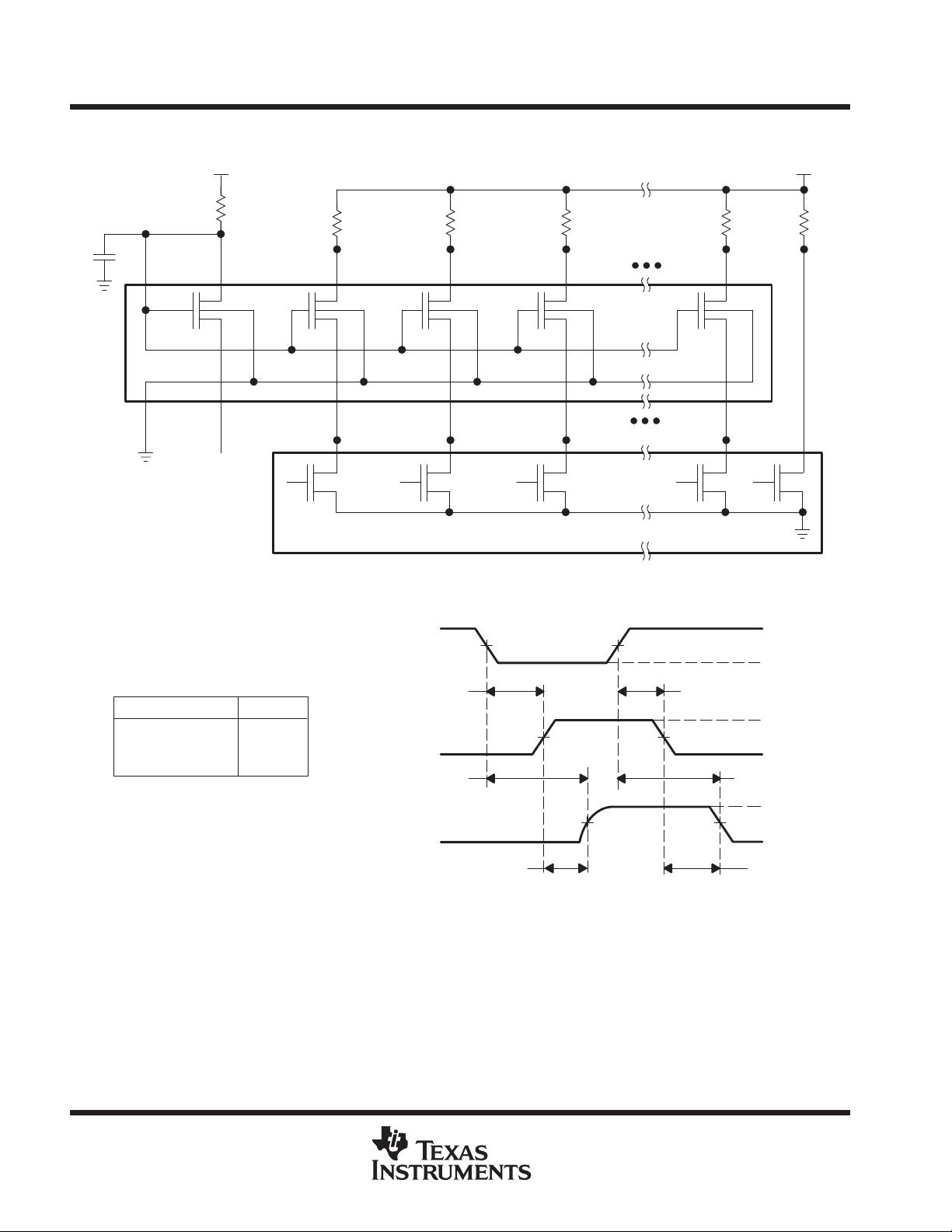

《TI-SN74TVC16222A:高性能低电压限制开关》 TI-SN74TVC16222A是一款专为电压限制应用设计的高性能宽总线集成电路,属于德州仪器(Texas Instruments)的Widebus家族成员。这款器件提供23个并行NMOS传递晶体管,其共同门极控制使得在高频率下实现低延迟的信号传递成为可能。 该芯片的主要特性在于其6.5欧姆的导通电阻,这确保了在端口A和B之间的低损耗连接。这种低的导通电阻使得信号在通过开关时的传播延迟达到最小,从而提高了系统性能。同时,SN74TVC16222A采用流经式的引脚布局,简化了印刷电路板(PCB)的迹线布设,有助于优化电路板的设计。 为了适应不同电压等级的应用,SN74TVC16222A可以直接与GTL+电平接口兼容,增加了设计的灵活性。此外,该器件具备出色的静电放电(ESD)保护能力,超过了JESD 22标准的要求,包括2000V的人体模型(A114-A)、200V的机器模型(A115-A)以及1000V的充电设备模型(C101),确保了在实际操作中的可靠性。 在电压限制功能方面,每个传递晶体管的低电压侧由一个参考晶体管设定电压上限。这一设计是为了保护那些输入端对高状态电压过冲敏感的组件。通过将所有晶体管的栅极级联到参考晶体管,可以实现22位开关功能。在数据表中提到的应用信息部分,提供了更多关于如何利用这一特性来防止电压过冲的详细信息。 值得注意的是,由于TVC阵列中所有晶体管具有相同的电气特性,所以任何晶体管都可以作为参考晶体管使用。由于在器件内部,晶体管之间的特性几乎相等,因此最大输出高状态电压(VOH)大约等于参考电压(VREF),各输出之间偏差极小。这是TVC解决方案相对于离散器件的一个显著优势。 由于制造工艺的对称性,每个比特的端口连接可以作为低电压侧,而I/O信号可以通过每个FET实现双向传输。订购信息显示,该芯片提供四种封装选项:SOP-DL、TSSOP-DG、TSSOP-DGG和TVSOP-DGV,分别适用于不同的温度范围和包装需求。 总结来说,TI-SN74TVC16222A是一款高性能、低电压限制的22位开关集成电路,具有低导通电阻、兼容多种电压电平、出色的ESD保护及灵活的封装选择,是设计中保护敏感电路免受电压过冲影响的理想选择。

剩余16页未读,继续阅读

- 粉丝: 7483

- 资源: 5764

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 核密度估计及ks检验确定最优核密度估计 使用Normal、box、triangle、Epanechnikov四种方法,默认是Normal 矩形框颜色可以自定义设置 可以对实际数据进行更精确的概率分布拟

- foc风机方案 高压 支持顺风启动 使用弦波 svpwm驱动方式 使用龙贝格观测器 无感FOC方案 包括原理图,源代码

- PSO优化极限学习机ELM matlab代码,备注详细,易于使用

- 细说数据分析模型之RFM模型以及代码实现

- 汽车EPB仿真模型,Carsim和Simulink联合仿真 1.其中包括 制动钳系统 的动力学建模 2.电机的转角三环pid控制,可以在模型中通过与制动钳模型的结合,实现电机的堵转效果,真实还

- COMSOL 激光烧蚀3D体热源引力场温度场仿真

- COMSOL 3D脉冲激光刻槽

- Simulink仿真:级联光伏发电MPPT追踪并网 关键词: 参考文献:具备同步电机特性的级联型光伏发电系统+视频讲解 仿真平台:MATLAB Simulink 主要内容:3个单独光伏发电MPPT级联

- FOC电流环模块进行,包含Park,Clark变,id、iq PI控制,限幅输出,角度查表,斜率步长,配合SVPWM模块可以实现电流模式的运行,包含说明书,物有所值,非普通代码,注释超级详细

- critic法计算指标权重 根据指标数据(每行是一个样本,每列是不同变量)计算各个指标的权重值并画图展示 MATLAB代码,备注清晰,易于使用

- 高斯回归拟合x与y,带置信区间 置信区间可自定义 根据案例数据准备自己的自变量x与因变量y数据 按照相应格式替为自己数据即可 MATLAB代码,备注清晰,易于使用

- 加权拟合2个正态分布参数与比例 一组数据可能由2个正态组合形成,可以进行拟合计算得到每组正态分布的参数与比例 matlab代码,根据自己需要修改案例数据即可

- LLC,变频与移相混合控制,有参考文献 变频控制与移相控制组成的混合式控制全桥LLC谐振变器仿真(PFM+PSM混合控制) 输出电压闭环控制,软开关,宽范围,可实现调频和移相的自动切,调频和移相控制

- matlab交通标志识别系统(含gui可视化界面,完整源码,代码配详细注释,程序实现识别交通标志图片并以文字形式输出结果) 附赠报告,代码结构清晰,有注释

- IMU与GPS融合定位,扩展卡尔曼滤波,cpp实现,机器人状态估计,有注释和运行说明

- 双峰高斯分布蒙特卡洛模并画pdf和cdf图 可设置双峰组合分布中不同正态参数的分布比例,也可以对多个组合进行计算 matlab代码,备注清楚,更改为自己需要的分布比例与参数即可

信息提交成功

信息提交成功