没有合适的资源?快使用搜索试试~ 我知道了~

TI-ADS130B04-Q1.pdf

需积分: 9 0 下载量 138 浏览量

2022-11-27

16:53:43

上传

评论 4

收藏 1.72MB PDF 举报

温馨提示

试读

60页

TI-ADS130B04-Q1.pdf

资源推荐

资源详情

资源评论

ADS130B04-Q1 Automotive, 4-Channel, 32-kSPS, Simultaneous-Sampling,

16-Bit, Delta-Sigma ADC

1 Features

• AEC-Q100 qualified for automotive applications:

– Temperature grade 1: –40°C to +125°C, T

A

• Functional Safety-Capable

– Documentation available to aid functional safety

system design

• 4 simultaneous-sampling, differential input ADCs

• Programmable data rate: Up to 32 kSPS

• Programmable gain: Up to 128

• Global-chop mode to remove offset drift over

temperature and time

• High-impedance analog inputs for direct sensor

connection

• Integrated negative charge pump allows input

signal measurements below ground

• Crosstalk between channels: –120 dB

• Low-drift internal reference: 1.2 V

• Precision internal oscillator

• CRC on communications and register map

• Analog and digital supplies: 2.7 V to 3.6 V

• Low power consumption: 5 mW at 3.3-V AVDD

and DVDD

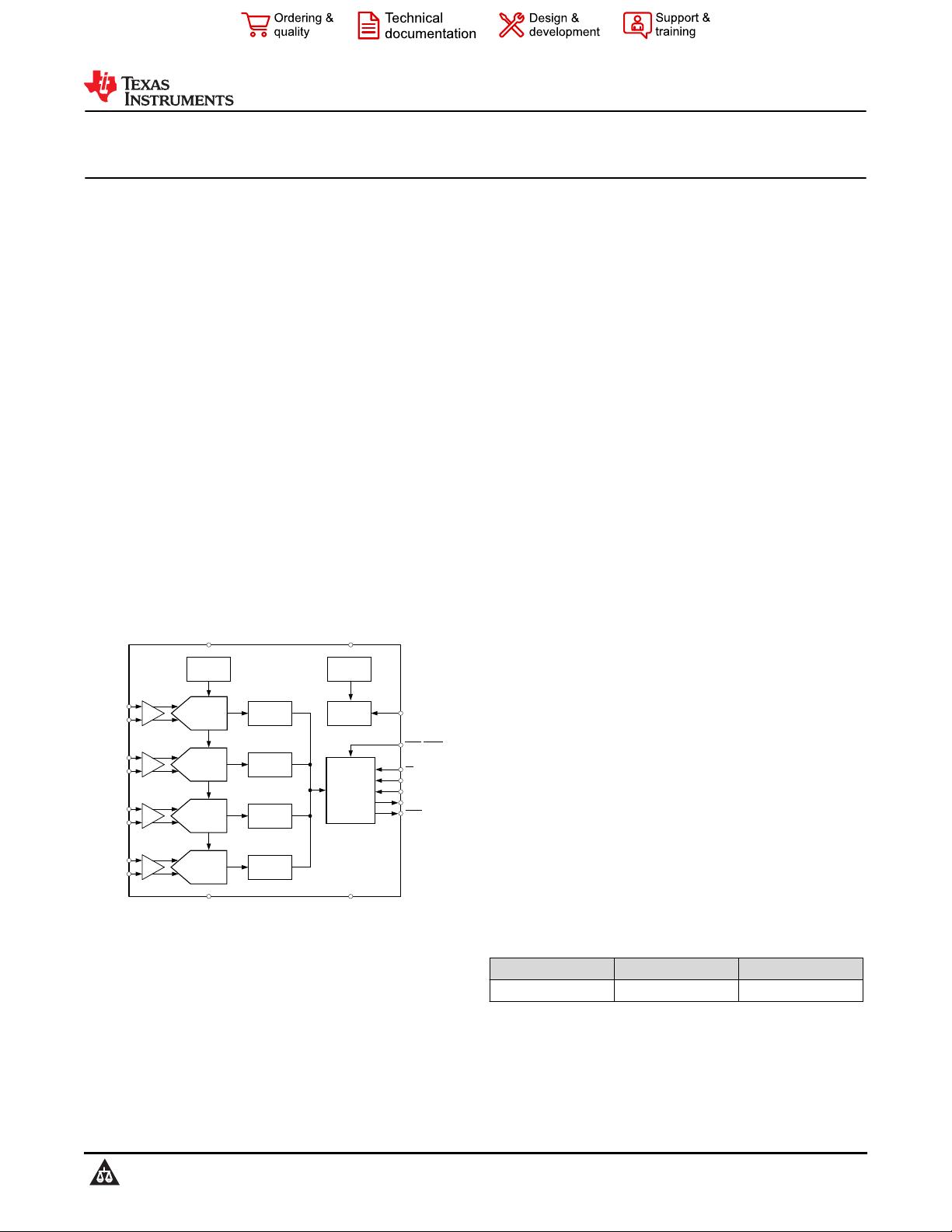

ADC

SCLK

DOUT

DIN

CS

AVDD

AGND

DVDD

DGND

DRDY

Oscillator

CLKIN

1.2-V

Reference

SYNC/RESET

Digital Filter

ADC

Digital Filter

ADC

Digital Filter

ADC

Digital Filter

AIN0P

AIN0N

+

–

AIN1P

AIN1N

+

–

AIN2P

AIN2N

+

–

AIN3P

AIN3N

+

–

Control &

Serial Interface

Clock

Selection

Simplified Block Diagram

2 Applications

• Automotive battery management systems (BMS):

– Current-shunt measurements

– Voltage measurements using external resistor

dividers

– Temperature measurements using thermistors

or analog output temperature sensors

• EV charging stations:

– DC e-metering

• Energy storage systems (ESS)

3 Description

The ADS130B04-Q1 is a four-channel, simultaneous-

sampling, 16-bit, delta-sigma (ΔΣ) analog-to-digital

converter (ADC) that offers wide dynamic range, low

power, and buffered analog inputs, making the device

an excellent fit for automotive battery management

systems (BMS). The ADC inputs can be directly

interfaced to shunt resistors for bidirectional battery-

current measurements, to resistor-divider networks

for high-voltage measurements, or to temperature

sensors (such as thermistors or analog output

temperature sensors).

The individual ADC channels can be independently

configured depending on the sensor input. A low-

noise, programmable gain amplifier (PGA) provides

gains ranging from 1 to 128 to amplify low-level

signals. The device features a global-chop mode to

remove offset drift over temperature and time.

A low-drift, 1.2-V reference and precision oscillator

are integrated into the device reducing printed circuit

board (PCB) area. Optional cyclic redundancy checks

(CRCs) on the data input, data output, and register

map maintain communication integrity.

The complete analog front-end (AFE) is offered in

a 20-pin TSSOP package and is specified over the

automotive temperature range of –40°C to +125°C.

Device Information

(1)

PART NUMBER PACKAGE BODY SIZE (NOM)

ADS130B04-Q1 TSSOP (20) 6.50 mm × 4.40 mm

(1) For all available packages, see the orderable addendum at

the end of the data sheet.

ADS130B04-Q1

SBASAD2 – NOVEMBER 2021

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications,

intellectual property matters and other important disclaimers. PRODUCTION DATA.

Table of Contents

1 Features............................................................................1

2 Applications.....................................................................1

3 Description.......................................................................1

4 Revision History.............................................................. 2

5 Pin Configuration and Functions...................................3

6 Specifications.................................................................. 4

6.1 Absolute Maximum Ratings........................................ 4

6.2 ESD Ratings............................................................... 4

6.3 Recommended Operating Conditions.........................5

6.4 Thermal Information....................................................5

6.5 Electrical Characteristics.............................................6

6.6 Timing Requirements..................................................8

6.7 Switching Characteristics............................................8

6.8 Timing Diagrams.........................................................9

6.9 Typical Characteristics..............................................10

7 Parameter Measurement Information..........................12

7.1 Noise Measurements................................................12

8 Detailed Description......................................................13

8.1 Overview...................................................................13

8.2 Functional Block Diagram.........................................13

8.3 Feature Description...................................................14

8.4 Device Functional Modes..........................................22

8.5 Programming............................................................ 26

8.6 Register Map.............................................................36

9 Application and Implementation..................................46

9.1 Application Information............................................. 46

9.2 Typical Application.................................................... 49

10 Power Supply Recommendations..............................52

10.1 CAP Pin Capacitor Requirement............................ 52

10.2 Power-Supply Sequencing......................................52

10.3 Power-Supply Decoupling.......................................52

11 Layout........................................................................... 52

11.1 Layout Guidelines................................................... 52

11.2 Layout Example...................................................... 53

12 Device and Documentation Support..........................54

12.1 Documentation Support.......................................... 54

12.2 Receiving Notification of Documentation Updates..54

12.3 Support Resources................................................. 54

12.4 Trademarks.............................................................54

12.5 Electrostatic Discharge Caution..............................54

12.6 Glossary..................................................................54

13 Mechanical, Packaging, and Orderable

Information.................................................................... 54

4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

DATE REVISION NOTES

November 2021 * Initial Release

ADS130B04-Q1

SBASAD2 – NOVEMBER 2021

www.ti.com

2 Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

Product Folder Links: ADS130B04-Q1

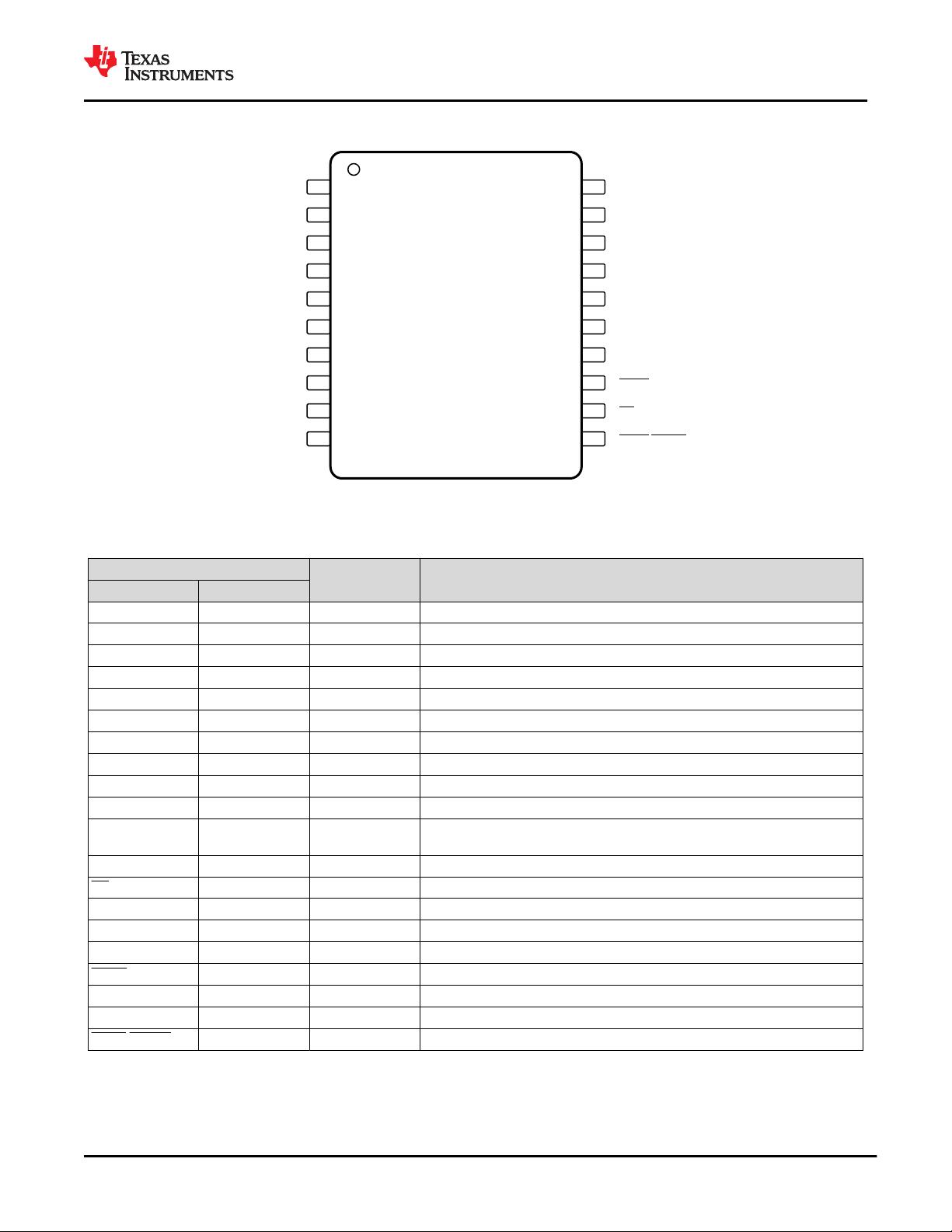

5 Pin Configuration and Functions

1AVDD 20 DVDD

2AGND 19 DGND

3AIN0P 18 CAP

4AIN0N 17 CLKIN

5AIN1N 16 DIN

6AIN1P 15 DOUT

7AIN2P 14 SCLK

8AIN2N 13 DRDY

9AIN3N 12 CS

10AIN3P 11 SYNC/RESET

Not to scale

Figure 5-1. PW Package, 20-Pin TSSOP (Top View)

Table 5-1. Pin Functions

PIN

TYPE DESCRIPTION

(1)

NAME NO.

AGND 2 Supply Analog ground

AIN0N 4 Analog input Negative analog input 0

AIN0P 3 Analog input Positive analog input 0

AIN1N 5 Analog input Negative analog input 1

AIN1P 6 Analog input Positive analog input 1

AIN2N 8 Analog input Negative analog input 2

AIN2P 7 Analog input Positive analog input 2

AIN3N 9 Analog input Negative analog input 3

AIN3P 10 Analog input Positive analog input 3

AVDD 1 Supply Analog supply. Connect a 1-µF capacitor to AGND.

CAP 18 Analog output

Digital low-dropout (LDO) regulator output.

Connect a 220-nF capacitor to DGND.

CLKIN 17 Digital input External clock input

CS 12 Digital input Chip select; active low

DGND 19 Supply Digital ground

DIN 16 Digital input Serial data input

DOUT 15 Digital output Serial data output

DRDY 13 Digital output Data ready; active low

DVDD 20 Supply Digital I/O supply. Connect a 1-µF capacitor to DGND.

SCLK 14 Digital input Serial data clock

SYNC/RESET 11 Digital input Conversion synchronization or system reset; active low

(1) See the Unused Inputs and Outputs section for details on how to connect unused pins.

www.ti.com

ADS130B04-Q1

SBASAD2 – NOVEMBER 2021

Copyright © 2021 Texas Instruments Incorporated

Submit Document Feedback

3

Product Folder Links: ADS130B04-Q1

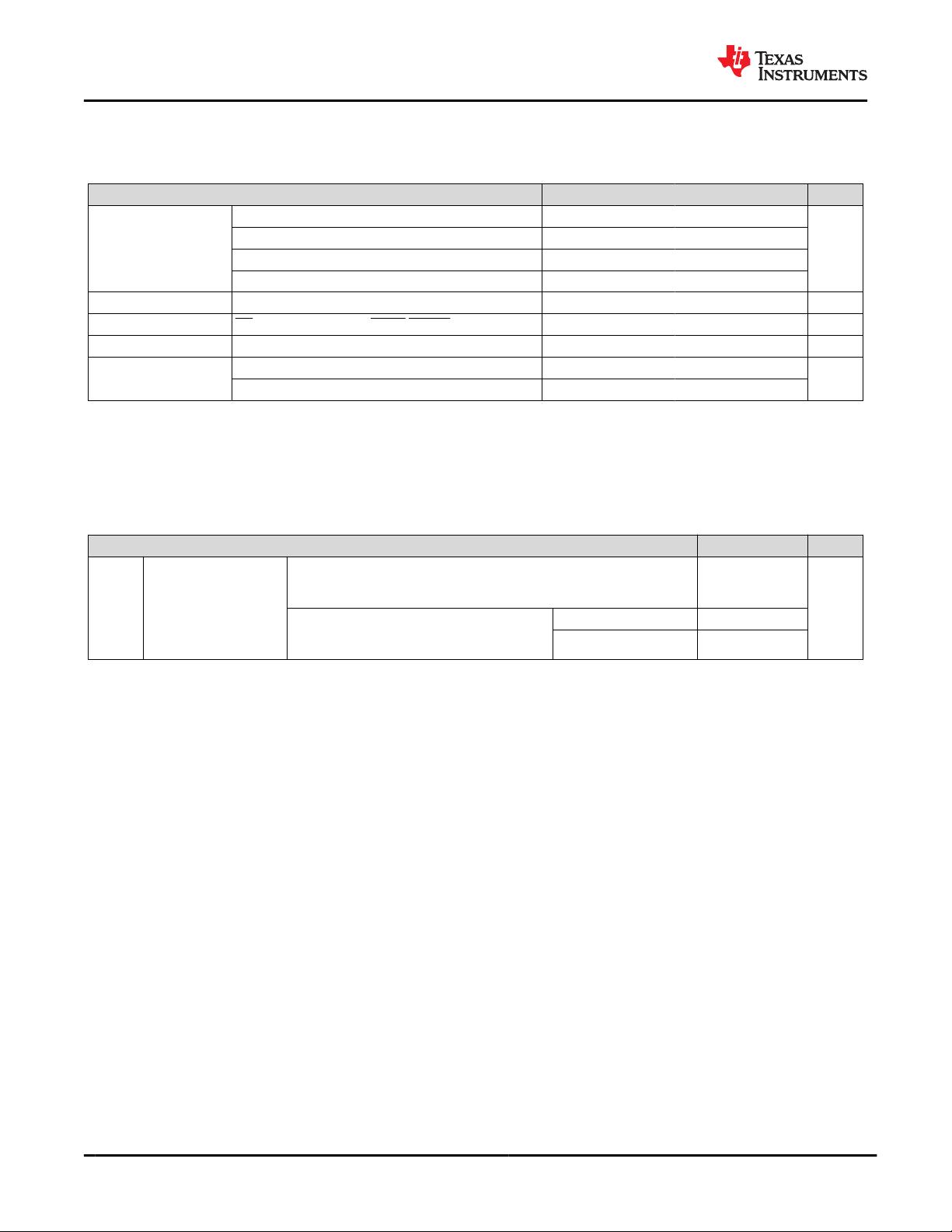

6 Specifications

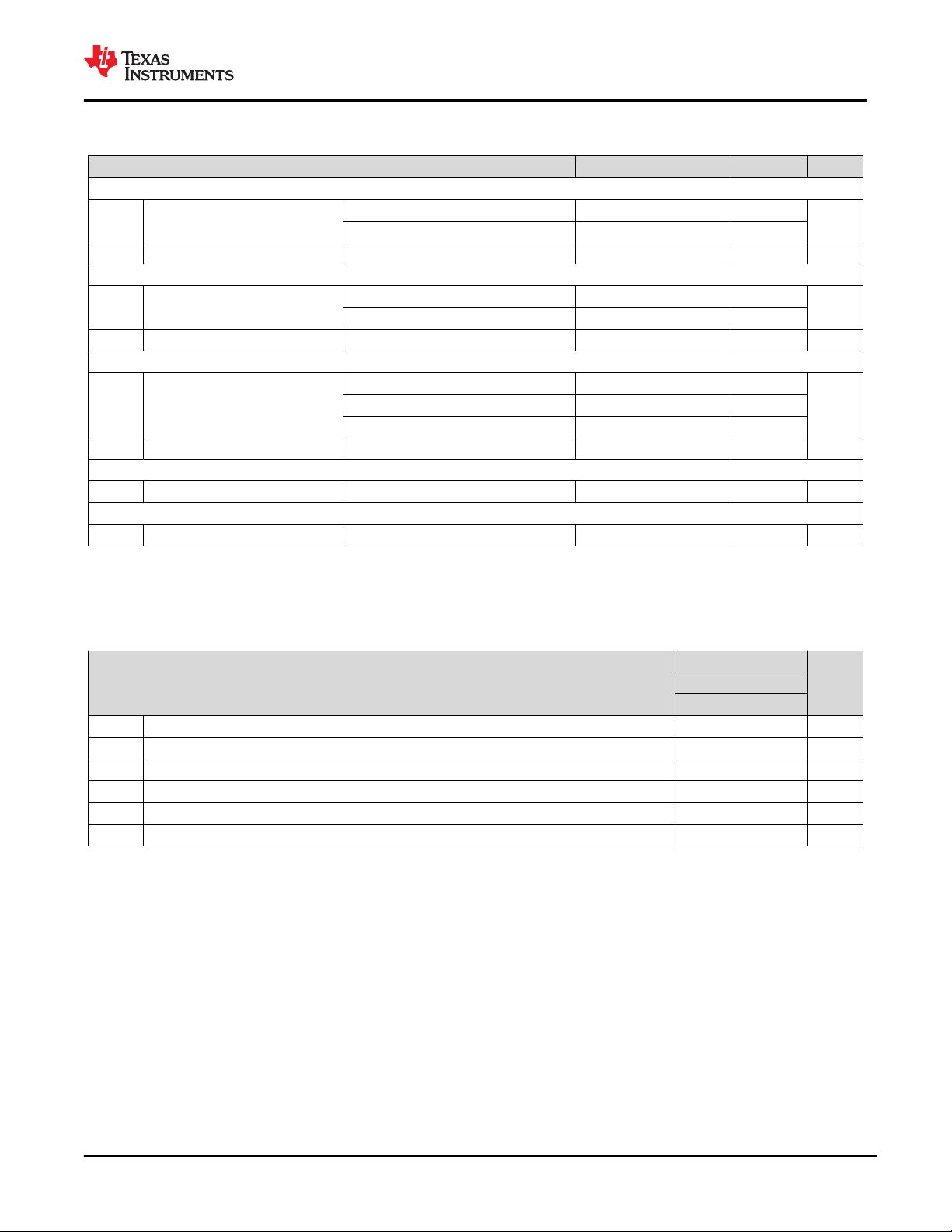

6.1 Absolute Maximum Ratings

See

(1)

MIN MAX UNIT

Power-supply voltage

AVDD to AGND –0.3 3.9

V

AGND to DGND –0.3 0.3

DVDD to DGND –0.3 3.9

CAP to DGND –0.3 2.2

Analog input voltage AINxP, AINxN AGND – 1.6 AVDD + 0.3 V

Digital input voltage CS, CLKIN, DIN, SCLK, SYNC/RESET DGND – 0.3 DVDD + 0.3 V

Input current Continuous, all pins except power-supply pins –10 10 mA

Temperature

Junction, T

J

150

°C

Storage, T

stg

–60 150

(1) Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply

functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions.

If briefly operating outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not

sustain damage, but it may not be fully functional – this may affect device reliability, functionality, performance, and shorten the device

lifetime.

6.2 ESD Ratings

VALUE UNIT

V

(ESD)

Electrostatic discharge

Human-body model (HBM),

per AEC Q100-002

(1)

HBM ESD classification level 2

±2000

V

Charged-device model (CDM),

per AEC Q100-011

CDM ESD classification level C4B

Corner pins ±750

All other non-corner pins ±500

(1) AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

ADS130B04-Q1

SBASAD2 – NOVEMBER 2021

www.ti.com

4 Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

Product Folder Links: ADS130B04-Q1

6.3 Recommended Operating Conditions

over operating ambient temperature range (unless otherwise noted)

MIN NOM MAX UNIT

POWER SUPPLY

Analog power supply

AVDD to AGND 2.7 3.3 3.6

V

AGND to DGND –0.3 0 0.3

Digital power supply DVDD to DGND 2.7 3.3 3.6 V

ANALOG INPUTS

(1)

V

AINxP

,

V

AINxN

Absolute input voltage

Gain = 1, 2 AGND – 0.1 AVDD – 1.2

V

Gain = 4, 8, 16, 32, 64, 128 AGND – 0.3 AVDD – 2.4

V

IN

Differential input voltage V

IN

= V

AINxP

- V

AINxN

–V

REF

/ Gain V

REF

/ Gain V

EXTERNAL CLOCK SOURCE

(2)

f

CLKIN

External clock frequency

High-resolution mode 0.3 8.192 8.2

MHzLow-power mode 0.3 4.096 4.15

Very-low-power mode 0.3 2.048 2.08

Duty cycle 40% 50% 60%

DIGITAL INPUTS

Input voltage DGND DVDD V

TEMPERATURE

T

A

Operating ambient temperature –40 125 °C

(1) The subscript "x" signifies the channel. For example, the positive analog input of channel 0 is named AIN0P. See the Pin Configuration

and Functions section for the pin names.

(2) An external clock is not required when the internal oscillator is used.

6.4 Thermal Information

THERMAL METRIC

(1)

ADS130B04-Q1

UNITPW (TSSOP)

20 PINS

R

θJA

Junction-to-ambient thermal resistance 91.5 °C/W

R

θJC(top)

Junction-to-case (top) thermal resistance 31.4 °C/W

R

θJB

Junction-to-board thermal resistance 43.0 °C/W

Ψ

JT

Junction-to-top characterization parameter 2.0 °C/W

Ψ

JB

Junction-to-board characterization parameter 42.5 °C/W

R

θJC(bot)

Junction-to-case (bottom) thermal resistance N/A °C/W

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application

report.

www.ti.com

ADS130B04-Q1

SBASAD2 – NOVEMBER 2021

Copyright © 2021 Texas Instruments Incorporated

Submit Document Feedback

5

Product Folder Links: ADS130B04-Q1

剩余59页未读,继续阅读

资源评论

不觉明了

- 粉丝: 3101

- 资源: 5337

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功