没有合适的资源?快使用搜索试试~ 我知道了~

TI-BQ25123.pdf

需积分: 9 0 下载量 68 浏览量

2022-11-20

17:12:14

上传

评论 5

收藏 3.2MB PDF 举报

温馨提示

试读

72页

TI-BQ25123.pdf

资源详情

资源评论

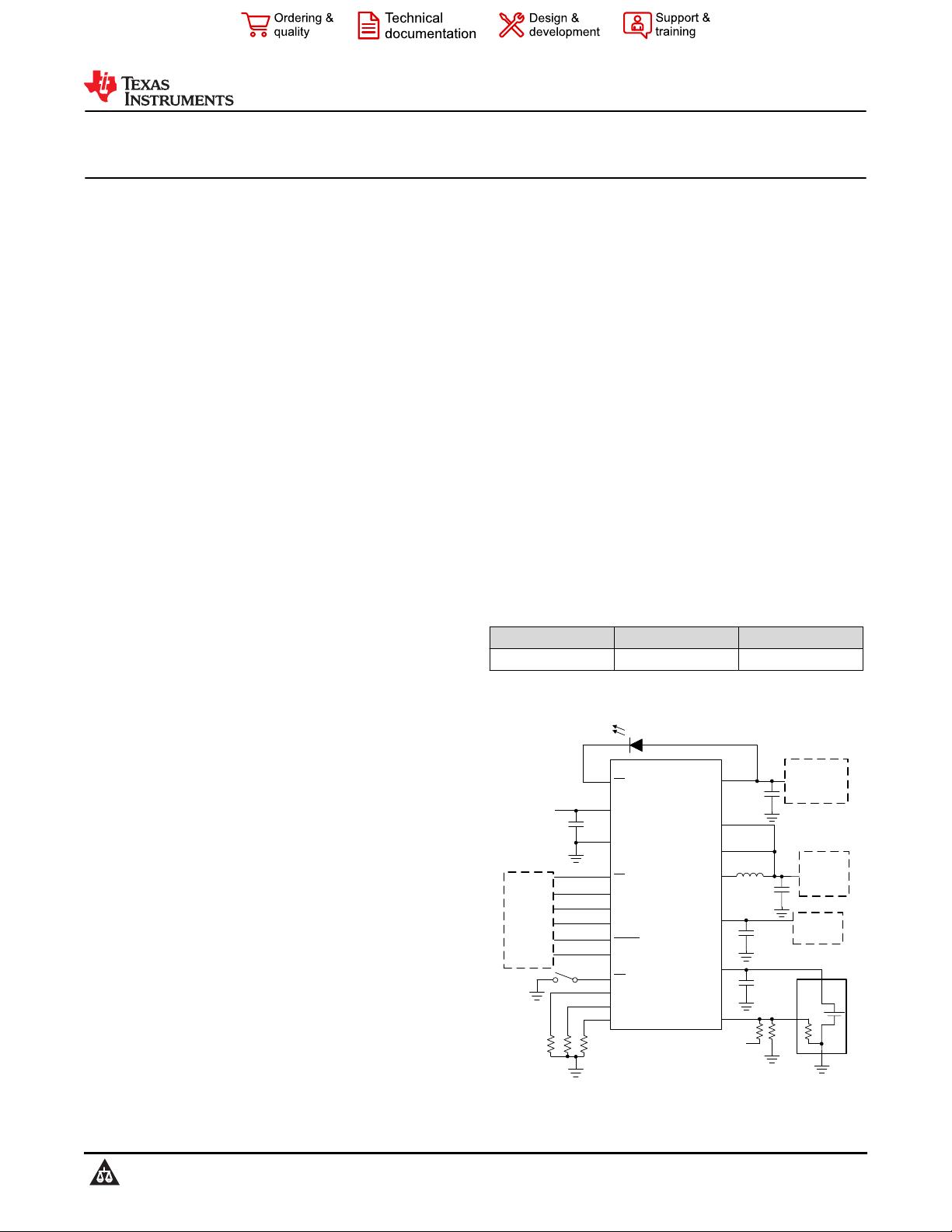

BQ25123 700-nA Low Iq Highly Integrated Battery Charge Management Solution for

Wearables

1 Features

• Increases system operation time between charges

– Configurable 300-mA buck regulator

– 700-nA (typical) Iq with buck converter enabled

(no load)

– Configurable load switch or 100-mA LDO

output

– Up to 300-mA charge current for fast charging

– 0.5% accurate battery voltage regulation

(configurable from 3.6 V to 4.65 V in 10-mV

steps)

– Configurable termination current down to

500 µA

– Simple voltage based battery monitor

• Highly integrated solution with small footprint

– 2.5 mm x 2.5 mm WCSP package and 6

external components for minimal solution

– Push-button wake-up and reset with adjustable

timers

– Power path management for powering the

system and charging the battery

– Power path management enables <50-nA Ship

Mode battery quiescent current for longest shelf

life

– Battery charger operates from 3.4 V – 5.5 V

IN

(5.5-V OVP / 20-V tolerant)

– Dedicated pins for input current limit, charge

current, termination current, and status output

• I

2

C communication control

– Charge voltage and current

– Termination threshold

– Input current limit

– VINDPM threshold

– Timer options

– Load switch control

– Controls for interrupts for faults and status

– System output voltage adjustment

– LDO output voltage adjustment

2 Applications

• Smart watches and other wearable devices

• Fitness accessories

• Health monitoring medical accessories

• Rechargeable toys

3 Description

The BQ25123 is a highly integrated battery charge

management IC that integrates the most common

functions for wearable devices: Linear charger,

regulated output, load switch, manual reset with timer,

and battery voltage monitor. The integrated buck

converter is a high efficiency, low I

Q

switcher using

DCS control that extends light load efficiency down to

10-µA load currents. The low quiescent current during

operation and shutdown enables maximum battery

life. The device supports charge currents from 5 mA

to 300 mA. The input current limit, charge current,

buck converter output voltage, LDO output voltage,

and other parameters are programmable through the

I

2

C interface.

Device Information

(1)

PART NUMBER PACKAGE BODY SIZE (NOM)

BQ25123 DSBGA (25) 2.50 mm x 2.50 mm

(1) For all available packages, see the orderable addendum at

the end of the data sheet.

BQ25123

GND

HOST

SDA

SCL

INT

SW

BAT

MCU /

SYSTEM

-+

NTC

TS

LS / LDO

<100mA

Load

IN

SYS

LSCTRL

VINLS

Unregulated

Load

PMID

IPRETERM

ISET

ILIM

IN

PG

CD

RESET

MR

Simplified Schematic

BQ25123

SLUSCZ6A – JANUARY 2018 – REVISED MAY 2021

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications,

intellectual property matters and other important disclaimers. PRODUCTION DATA.

Table of Contents

1 Features............................................................................1

2 Applications..................................................................... 1

3 Description.......................................................................1

4 Revision History.............................................................. 2

5 Description (continued).................................................. 3

6 Device Comparison Table...............................................3

7 Pin Configuration and Functions...................................4

8 Specifications.................................................................. 6

8.1 Absolute Maximum Ratings........................................ 6

8.2 ESD Ratings............................................................... 6

8.3 Recommended Operating Conditions.........................6

8.4 Thermal Information....................................................7

8.5 Electrical Characteristics.............................................7

8.6 Timing Requirements................................................ 11

8.7 Typical Characteristics.............................................. 14

9 Detailed Description......................................................16

9.1 Overview................................................................... 16

9.2 Functional Block Diagram......................................... 16

9.3 Feature Description...................................................17

9.4 Device Functional Modes..........................................29

9.5 Programming............................................................ 31

9.6 Register Maps...........................................................34

10 Application and Implementation................................ 47

10.1 Application Information........................................... 47

10.2 Typical Application.................................................. 47

11 Layout........................................................................... 63

11.1 Layout Guidelines................................................... 63

11.2 Layout Example...................................................... 63

12 Device and Documentation Support..........................64

12.1 Device Support....................................................... 64

12.2 Receiving Notification of Documentation Updates..64

12.3 Support Resources................................................. 64

12.4 Trademarks.............................................................64

12.5 Electrostatic Discharge Caution..............................64

12.6 Glossary..................................................................64

13 Mechanical, Packaging, and Orderable

Information.................................................................... 64

4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

Changes from Revision * (January 2018) to Revision A (May 2021) Page

• Updated the numbering format for tables, figures, and cross-references throughout the document..................1

BQ25123

SLUSCZ6A – JANUARY 2018 – REVISED MAY 2021

www.ti.com

2 Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

Product Folder Links: BQ25123

5 Description (continued)

The battery is charged using a standard Li-Ion charge profile with three phases: precharge, constant current and

constant voltage. A voltage-based JEITA compatible battery pack thermistor monitoring input (TS) is included

that monitors battery temperature and automatically changes charge parameters to prevent the battery from

charging outside of its safe temperature range. The charger is optimized for 5-V USB input, with 20-V tolerance

to withstand line transients. The buck converter is run from the input or battery. When in battery only mode, the

device can run from a battery up to 4.65 V.

A configurable load switch allows system optimization by disconnecting infrequently used devices. The manual

reset with timer allows mutliple different configuration options for wake are reset optimization. A simple voltage

based monitor provides battery level information to the host in 2% increments from 60% to 100% of the

programmed V

(BATREG)

.

6 Device Comparison Table

PART NUMBER

VINDPM

DEFAULT SYS

OUTPUT

DEFAULT LDO

OUTPUT

DEFAULT VBERG

DEFAULT CHARGE

CURRENT

DEFAULT

TERMINATION

CURRENT

BQ25123 Enabled 1.25 V 3 V 4.2 V 10 mA 2 mA

www.ti.com

BQ25123

SLUSCZ6A – JANUARY 2018 – REVISED MAY 2021

Copyright © 2021 Texas Instruments Incorporated

Submit Document Feedback

3

Product Folder Links: BQ25123

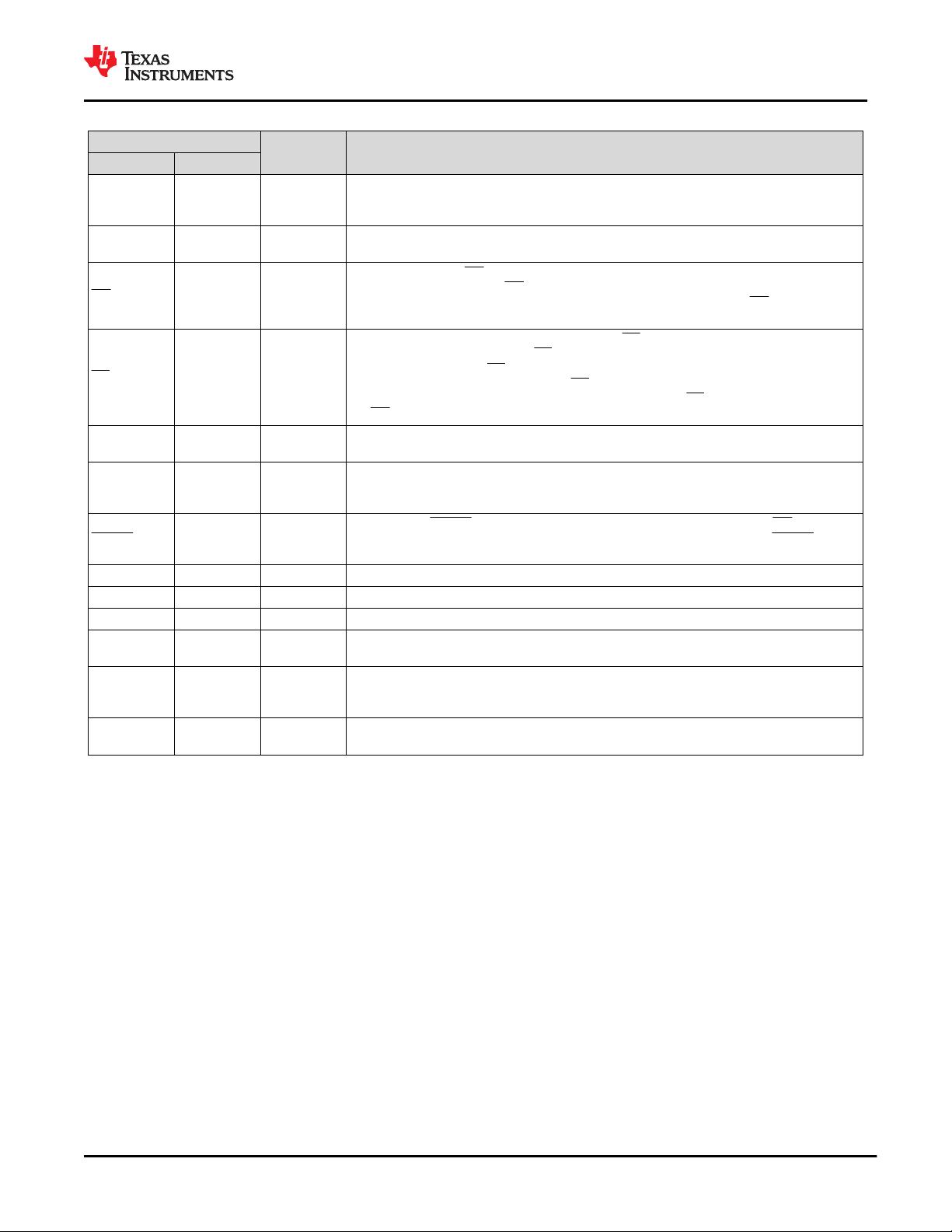

7 Pin Configuration and Functions

1 2 3 4 5

A

B

C

D

E

Not to scale

GND IN PMID SW PGND

BAT BAT PMID VINLS SYS

ISET ILIM TS VINLS LS/LDO

IPRETERM INT RESET PG GND

MR CD LSCTRL SDA SCL

Figure 7-1. YFP Package 25-Pin (DSBGA) Top View

Table 7-1. Pin Functions

PIN

I/O DESCRIPTION

NAME NO.

BAT B1, B2 I/O

Battery Connection. Connect to the positive terminal of the battery. Bypass BAT to GND with

at least 1 µF of ceramic capacitance.

CD E2 I

Chip Disable. Drive CD low to place the part in High-Z mode with battery only present, or

enable charging when V

IN

is valid. Drive CD high for Active Battery mode when battery only

is present, and disable charge when V

IN

is present. CD is pulled low internally with 900 kΩ.

GND A1, D5 - Ground connection. Connect to the ground plane of the circuit.

ILIM C2 I

Adjustable Input Current Limit Programming. Connect a resistor from ILIM to GND to

program the input current limit. The input current includes the system load and the battery

charge current. Connect ILIM to GND to set the input current limit to the internal default

threshold. ILIM can also be updated through I

2

C.

IN A2 I

DC Input Power Supply. IN is connected to the external DC supply. Bypass IN to GND with

at least 1 µF of capacitance using a ceramic capacitor.

INT D2 O

Status Output. INT is an open-drain output that signals charging status and fault interrupts.

INT pulls low during charging. INT is high impedance when charging is complete, disabled,

or the charger is in high impedance mode. When a fault occurs, a 128µs pulse is sent out as

an interrupt for the host. INT charge indicator function is enabled/disabled using the EN_INT

bit in the control register. Connect INT to a logic rail using an LED for visual indication of

charge status or through a 100kΩ resistor to communicate with the host processor.

IPRETERM D1 I

Termination current programming input. Connect a 0-Ω to 10-kΩ resistor from IPRETERM to

GND to program the termination current between 5% and 20% of the charge current. The

pre-charge current is the same as the termination current setting. Connect IPRETERM to

GND to set the termination current to the internal default threshold. IPRETERM can also be

updated through I

2

C.

ISET C1 I

Fast-Charge Current Programming Input. Connect a resistor from ISET to GND to program

the fast-charge current level. Connect a resistor from ISET to GND to set the charge current

to the internal default. ISET can also be updated through I

2

C. While charging, the voltage

at ISET reflects the actual charging current and can be used to monitor charge current if an

ISET resistor is present and the device is not in host mode.

BQ25123

SLUSCZ6A – JANUARY 2018 – REVISED MAY 2021

www.ti.com

4 Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

Product Folder Links: BQ25123

Table 7-1. Pin Functions (continued)

PIN

I/O DESCRIPTION

NAME NO.

LS/LDO C5 O

Load Switch or LDO output. Connect 1 µF of effective ceramic capacitance to this pin to

assure stability. Be sure to account for capacitance bias voltage derating when selecting the

capacitor.

LSCTRL E3 I

Load Switch and LDO Control Input. Pull high to enable the LS/LDO output, pull low to

disable the LS/LDO output.

MR E1 I

Manual Reset Input. MR is a push-button input that must be held low for greater than t

RESET

to assert the reset output. If MR is pressed for a shorter period, there are two programmable

timer events, t

WAKE1

and t

WAKE2

, that trigger an interrupt to the host. The MR input can also

be used to bring the device out of Ship mode.

PG D4 O

Open-drain Power Good status indication output. PG pulls to GND when V

IN

is above

V

(BAT)

+ V

SLP

and less that V

OVP

. PG is high-impedance when the input power is not within

specified limits. Connect PG to the desired logic voltage rail using a 1kΩ to 100kΩ resistor,

or use with an LED for visual indication. PG can also be configured as a push-button voltage

shifted output (MRS) in the registers, where the output of the

PG pin reflects the status of

the MR input, but pulled up to the desired logic voltage rail using a 1kΩ to 100kΩ resistor.

PGND A5 -

Power ground connection. Connect to the ground plane of the circuit. Connect the output

filter cap from the buck converter to this ground as shown in the layout example.

PMID A3, B3 I/O

High Side Bypass Connection. Connect at least 3µF of ceramic capacitance with DC bias

derating from PMID to GND as close to the PMID and GND pins as possible. When entering

Ship Mode, PMID is discharged by a 20-kΩ internal discharge resistor.

RESET D3 O

Reset Output. RESET is an open drain active low output that goes low when MR is held

low for longer than t

RESET

, which is configurable by the MRRESET registers. RESET is

deasserted after the t

RESET_D,

typically 400ms.

SCL E5 I I

2

C Interface Clock. Connect SCL to the logic rail through a 10-kΩ resistor.

SDA E4 I/O I

2

C Interface Data. Connect SDA to the logic rail through a 10-kΩ resistor.

SW A4 O Inductor Connection. Connect to the switched side of the external inductor.

SYS B5 I

System Voltage Sense Connection. Connect SYS to the system output at the output bulk

capacitors. Bypass SYS locally with at least 4.7 µF of effective ceramic capacitance.

TS C3 I

Battery Pack NTC Monitor. Connect TS to the center tap of a resistor divider from VIN to

GND. The NTC is connected from TS to GND. The TS function provides four thresholds for

JEITA compatibility. TS faults are reported by the I

2

C interface during charge mode.

VINLS B4, C4 I

Input to the Load Switch / LDO output. Connect 1 µF of effective ceramic capacitance from

this pin to GND.

www.ti.com

BQ25123

SLUSCZ6A – JANUARY 2018 – REVISED MAY 2021

Copyright © 2021 Texas Instruments Incorporated

Submit Document Feedback

5

Product Folder Links: BQ25123

剩余71页未读,继续阅读

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论0

最新资源