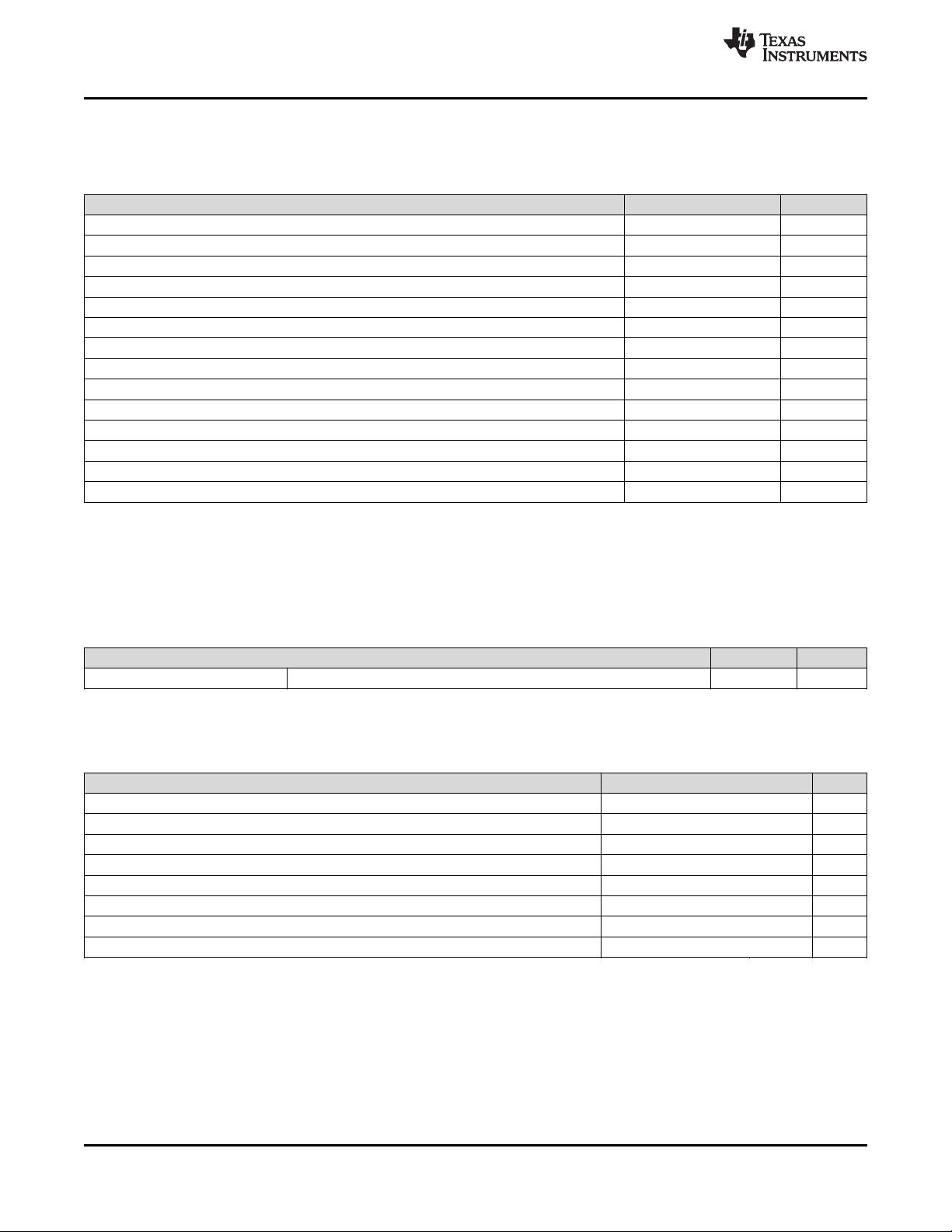

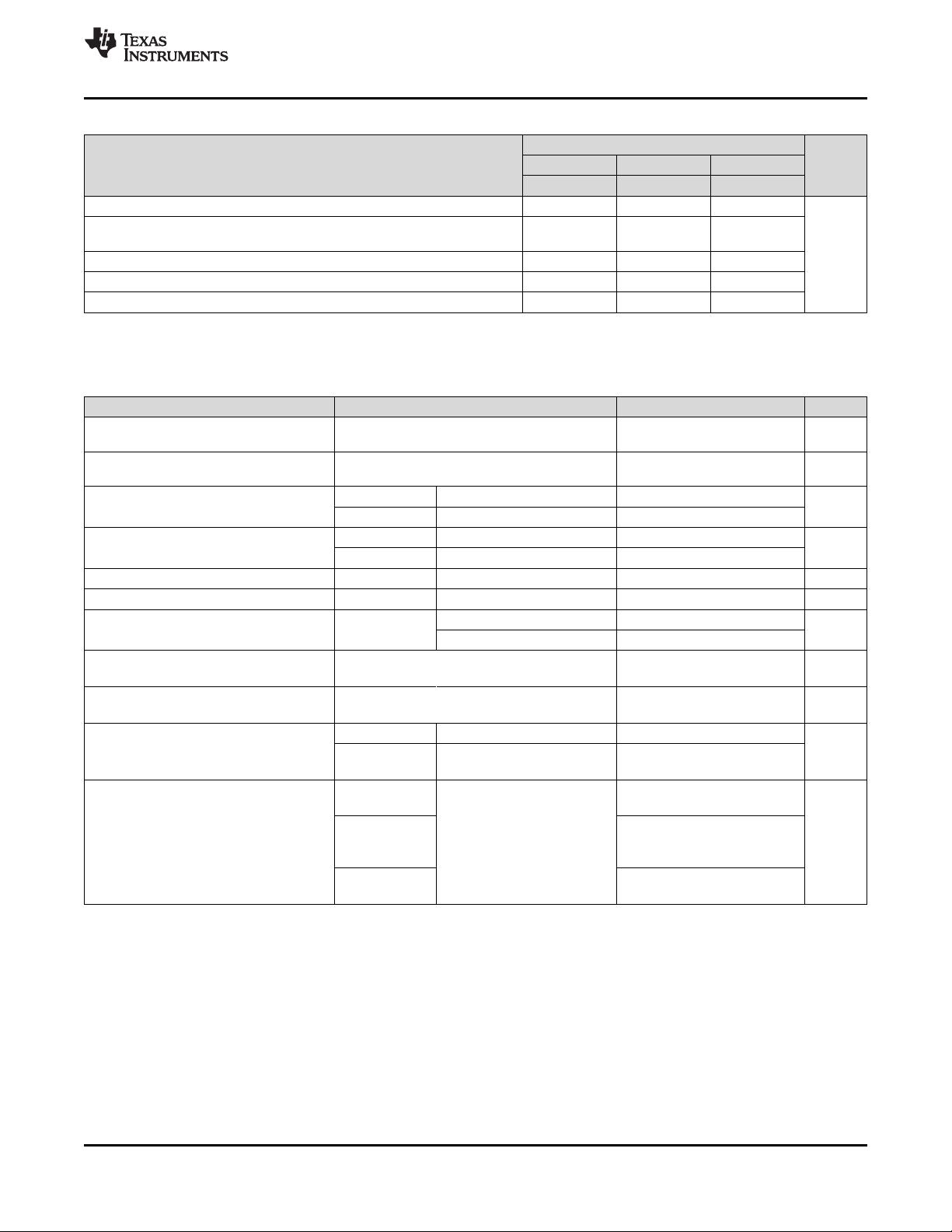

"TI-TPIC6C596.pdf" 本文档主要介绍了TI公司的TPIC6C596设备,该设备是一个8位移寄存器,具有低电阻、低电流和高输出电流的特点,适用于中等负载电路、继电器、磁阀和低电压负载等应用。下面详细介绍该设备的特点和应用。 特点 1. 低电阻(RDS(on)):TPIC6C596设备具有低电阻特点,电阻值仅为7Ω(典型值),使其在高频率应用中的energy loss最小化。 2. 高输出电流:设备具有高输出电流能力,输出电流可达250mA,满足中等负载电路的需求。 3. 掉电保护:TPIC6C596设备具有内置的电压clamp,保护输出端口免受电压 transient干扰的影响。 4. ESD保护:设备具有2500 V的ESD保护能力,防止静电干扰对设备的影响。 5. 低功率消耗:TPIC6C596设备具有低功率消耗特点,适用于低功率应用场景。 6. 高输出电压:设备的输出电压可达33 V,适用于中等电压负载应用。 应用 1. 仪器集群:TPIC6C596设备适用于仪器集群应用,例如仪器仪表、自动控制系统等。 2. 告示灯控制:设备适用于告示灯控制应用,例如汽车告示灯、工业告示灯等。 3. LED照明控制:TPIC6C596设备适用于LED照明控制应用,例如汽车LED照明、工业LED照明等。 4. 继电器驱动:设备适用于继电器驱动应用,例如汽车继电器、工业继电器等。 5. 汽车应用:TPIC6C596设备适用于汽车应用,例如汽车告示灯、汽车LED照明、汽车继电器等。 技术参数 1. 输出电流:250mA 2. 输出电压:33 V 3. 电阻(RDS(on)):7 Ω(典型值) 4. ESD保护:2500 V 5. 工作温度:-40°C至125°C 6. 存储温度:-65°C至150°C 结论 TPIC6C596设备是一款功能强大且灵活的8位移寄存器,适用于中等负载电路、继电器、磁阀和低电压负载等应用。该设备具有低电阻、低电流和高输出电流的特点,且具有ESD保护和低功率消耗的特点,非常适用于汽车、工业和仪器等领域的应用。

剩余30页未读,继续阅读

- 粉丝: 7127

- 资源: 5764

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 上帝视角了解中国地势:全国100+250+500+1000+1500+2000+2500+3000+4000+5000+6000+7000+8000等高线、南北东西分区山峰主峰、平原盆地沙漠等特征区

- 基于滴滴平台数据测算的城市发展环境指数.zip

- 带货云豹直播完美无bug直播带货系统购物直播+带视频教程

- 机械设计新能源汽车换电站总装step全套技术资料100%好用.zip

- 机械设计移动开放式喷砂机sw14全套技术资料100%好用.zip

- IIT BHU 校园道路数据集(4590 张图像)JPG.7z

- 入职90天个人发展指引:从自我分析到职业发展里程碑

- 基于C语言的简单停车场管理系统实现与应用

- 信息安全领域的钓鱼邮件防范技巧与应对措施

- 河南工程学院oj答案河南工程学院ACM程序设计竞赛与OJ基础题目解析及答案(C语言实现)

- Evaluating the Evolution of YOLO (You Only LookOnce) Models: A Comprehensive Benchmark Study of YOLO

- 机械设计牙刷全自动成型包装一体机sw12全套技术资料100%好用.zip

- IT部门网络管理绩效考核体系的构建

- 基于查询的图像外推技术QueryOTR:混合Transformer架构用于无缝图像扩展与外画

- 头盔合规检测的数据集(1K+ 张图像)YOLOv9+JPG+TXT

- 机械设计液晶面板BUFFER设备sw18全套技术资料100%好用.zip

信息提交成功

信息提交成功