没有合适的资源?快使用搜索试试~ 我知道了~

stm32h745zi.pdf

需积分: 9 20 下载量 13 浏览量

2020-12-02

16:09:41

上传

评论

收藏 3.34MB PDF 举报

温馨提示

试读

252页

双32位Arm®Cortex®-M7高达480MHz和-M4 mcu,高达2MB闪存,1MB RAM, 46 com。和模拟接口,SMPS

资源详情

资源评论

资源推荐

This is information on a product in full production.

May 2019 DS12923 Rev 1 1/252

STM32H745xI/G

Dual 32-bit Arm

®

Cortex

®

-M7 up to 480MHz and -M4 MCUs,

up to 2MB Flash, 1MB RAM, 46 com. and analog interfaces, SMPS

Datasheet - production data

Features

Dual core

• 32-bit Arm

®

Cortex

®

-M7 core with double-

precision FPU and L1 cache: 16 Kbytes of data

and 16 Kbytes of instruction cache; frequency

up to 480 MHz, MPU, 1027 DMIPS/

2.14 DMIPS/MHz (Dhrystone 2.1), and DSP

instructions

• 32-bit Arm

®

32-bit Cortex

®

-M4 core with FPU,

Adaptive real-time accelerator (ART

Accelerator™) for internal Flash memory and

external memories, frequency up to 240 MHz,

MPU, 300 DMIPS/1.25 DMIPS /MHz

(Dhrystone 2.1), and DSP instructions

Memories

• Up to 2 Mbytes of Flash memory with read-

while-write support

• 1 Mbyte of RAM: 192 Kbytes of TCM RAM (inc.

64 Kbytes of ITCM RAM + 128 Kbytes of

DTCM RAM for time critical routines),

864 Kbytes of user SRAM, and 4 Kbytes of

SRAM in Backup domain

• Dual mode Quad-SPI memory interface

running up to 133 MHz

• Flexible external memory controller with up to

32-bit data bus: SRAM, PSRAM,

SDRAM/LPSDR SDRAM, NOR/NAND Flash

memory clocked up to 125 MHz in

Synchronous mode

• CRC calculation unit

Security

• ROP, PC-ROP, active tamper

General-purpose input/outputs

• Up to 168 I/O ports with interrupt capability

Reset and power management

• 3 separate power domains which can be

independently clock-gated or switched off:

– D1: high-performance capabilities

– D2: communication peripherals and timers

– D3: reset/clock control/power management

• 1.62 to 3.6 V application supply and I/Os

• POR, PDR, PVD and BOR

• Dedicated USB power embedding a 3.3 V

internal regulator to supply the internal PHYs

• Embedded regulator (LDO) to supply the digital

circuitry

• High power-efficiency SMPS step-down

converter regulator to directly supply V

CORE

and/or external circuitry

• Voltage scaling in Run and Stop mode (6

configurable ranges)

• Backup regulator (~0.9 V)

• Voltage reference for analog peripheral/V

REF+

• 1.2 to 3.6 V V

BAT

supply

• Low-power modes: Sleep, Stop, Standby and

V

BAT

supporting battery charging

Low-power consumption

• V

BAT

battery operating mode with charging

capability

• CPU and domain power state monitoring pins

• 2.95 µA in Standby mode (Backup SRAM OFF,

RTC/LSE ON)

FBGA

TFBGA240+25

(14x14 mm)

UFBGA176+25

(10x10 mm)

FBGA

LQFP144

(20x20 mm)

LQFP176

(24x24 mm)

LQFP208

(28x28 mm)

www.st.com

STM32H745xI/G

2/252 DS12923 Rev 1

Clock management

• Internal oscillators: 64 MHz HSI, 48 MHz

HSI48, 4 MHz CSI, 32 kHz LSI

• External oscillators: 4-48 MHz HSE,

32.768 kHz LSE

• 3× PLLs (1 for the system clock, 2 for kernel

clocks) with Fractional mode

Interconnect matrix

• 3 bus matrices (1 AXI and 2 AHB)

• Bridges (5× AHB2-APB, 2× AXI2-AHB)

4 DMA controllers to unload the CPU

• 1× high-speed master direct memory access

controller (MDMA) with linked list support

• 2× dual-port DMAs with FIFO

• 1× basic DMA with request router capabilities

Up to 35 communication peripherals

• 4× I2Cs FM+ interfaces (SMBus/PMBus)

• 4× USARTs/4x UARTs (ISO7816 interface,

LIN, IrDA, up to 12.5 Mbit/s) and 1x LPUART

• 6× SPIs, 3 with muxed duplex I2S audio class

accuracy via internal audio PLL or external

clock, 1x I2S in LP domain (up to 150 MHz)

• 4x SAIs (serial audio interface)

• SPDIFRX interface

• SWPMI single-wire protocol master I/F

• MDIO Slave interface

• 2× SD/SDIO/MMC interfaces (up to 125 MHz)

• 2× CAN controllers: 2 with CAN FD, 1 with

time-triggered CAN (TT-CAN)

• 2× USB OTG interfaces (1FS, 1HS/FS) crystal-

less solution with LPM and BCD

• Ethernet MAC interface with DMA controller

• HDMI-CEC

• 8- to 14-bit camera interface (up to 80 MHz)

11 analog peripherals

• 3× ADCs with 16-bit max. resolution (up to 36

channels, up to 3.6 MSPS)

• 1× temperature sensor

• 2× 12-bit D/A converters (1 MHz)

• 2× ultra-low-power comparators

• 2× operational amplifiers (7.3 MHz bandwidth)

• 1× digital filters for sigma delta modulator

(DFSDM) with 8 channels/4 filters

Graphics

• LCD-TFT controller up to XGA resolution

• Chrom-ART graphical hardware Accelerator™

(DMA2D) to reduce CPU load

• Hardware JPEG Codec

Up to 22 timers and watchdogs

• 1× high-resolution timer (2.1 ns max

resolution)

• 2× 32-bit timers with up to 4 IC/OC/PWM or

pulse counter and quadrature (incremental)

encoder input (up to 240 MHz)

• 2× 16-bit advanced motor control timers (up to

240 MHz)

• 10× 16-bit general-purpose timers (up to

240 MHz)

• 5× 16-bit low-power timers (up to 240 MHz)

• 4× watchdogs (independent and window)

• 2× SysTick timers

• RTC with sub-second accuracy and hardware

calendar

Debug mode

• SWD & JTAG interfaces

• 4-Kbyte Embedded Trace Buffer

True random number generators (3

oscillators each)

96-bit unique ID

Optional support of extended temperature

range up to 125 °C (specific part numbers)

All packages are ECOPACK

®

2 compliant

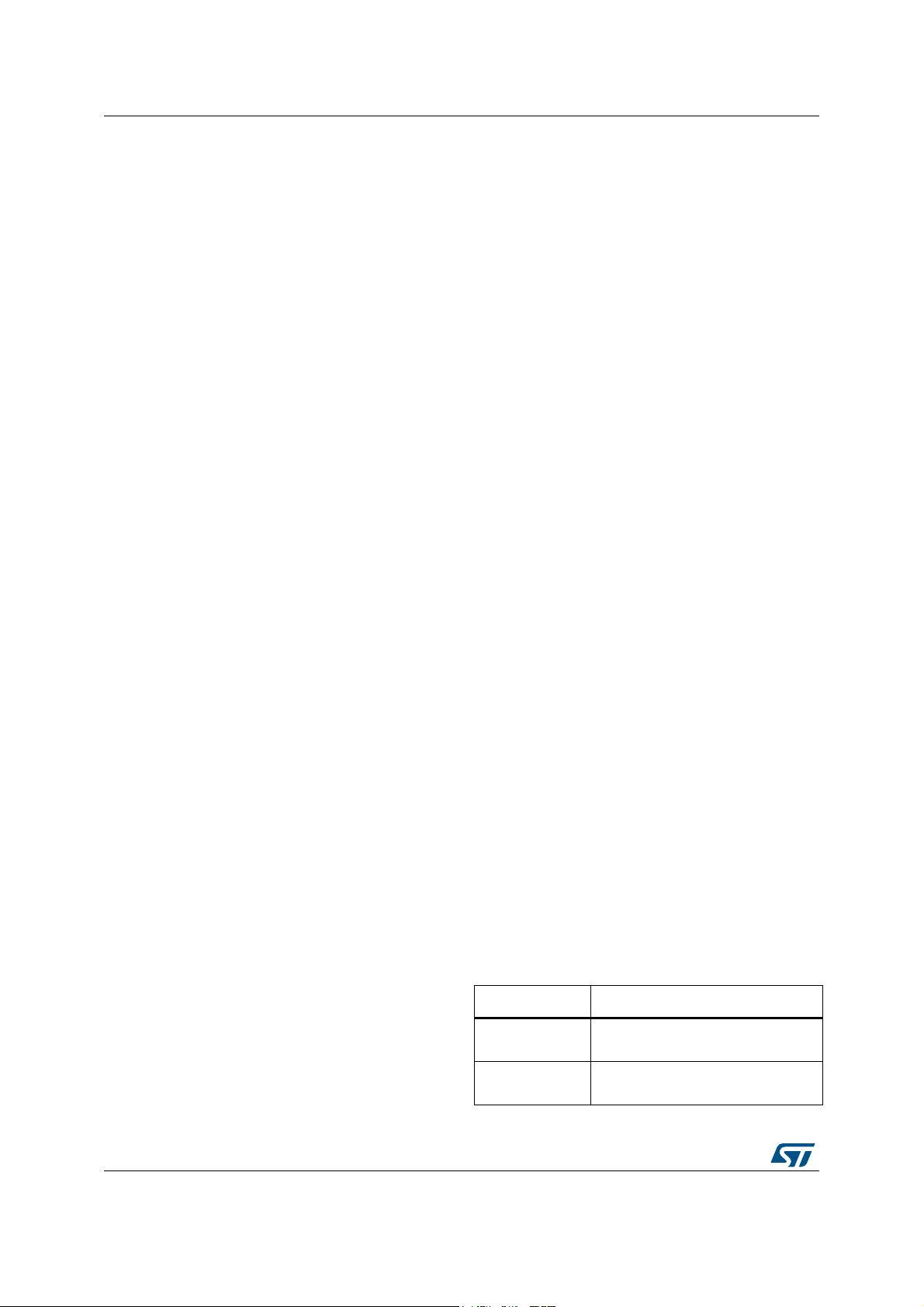

Table 1. Device summary

Reference Part number

STM32H745xI

STM32H745ZI, STM32H745II,

STM32H745BI, STM32H745XI

STM32H745xG

STM32H745ZG, STM32H745IG,

STM32H745BG, STM32H745XG

DS12923 Rev 1 3/252

STM32H745xI/G Contents

6

Contents

1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

2 Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

3 Functional overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

3.1 Dual Arm

®

Cortex

®

cores . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

3.1.1 Arm

®

Cortex

®

-M7 with FPU . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

3.1.2 Arm

®

Cortex

®

-M4 with FPU . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

3.2 Memory protection unit (MPU) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

3.3 Memories . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

3.3.1 Embedded Flash memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

3.3.2 Embedded SRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

3.3.3 ART™ accelerator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

3.4 Boot modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

3.5 Power supply management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

3.5.1 Power supply scheme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

3.5.2 Power supply supervisor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

3.5.3 Voltage regulator (SMPS step-down converter and LDO) . . . . . . . . . . . 28

3.5.4 SMPS step-down converter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

3.6 Low-power strategy . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

3.7 Reset and clock controller (RCC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

3.7.1 Clock management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

3.7.2 System reset sources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

3.8 General-purpose input/outputs (GPIOs) . . . . . . . . . . . . . . . . . . . . . . . . . . 31

3.9 Bus-interconnect matrix . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

3.10 DMA controllers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

3.11 Chrom-ART Accelerator™ (DMA2D) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

3.12 Nested vectored interrupt controller (NVIC) . . . . . . . . . . . . . . . . . . . . . . . 34

3.13 Extended interrupt and event controller (EXTI) . . . . . . . . . . . . . . . . . . . . 34

3.14 Cyclic redundancy check calculation unit (CRC) . . . . . . . . . . . . . . . . . . . 34

3.15 Flexible memory controller (FMC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

3.16 Quad-SPI memory interface (QUADSPI) . . . . . . . . . . . . . . . . . . . . . . . . . 35

Contents STM32H745xI/G

4/252 DS12923 Rev 1

3.17 Analog-to-digital converters (ADCs) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

3.18 Temperature sensor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

3.19 V

BAT

operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

3.20 Digital-to-analog converters (DAC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

3.21 Ultra-low-power comparators (COMP) . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

3.22 Operational amplifiers (OPAMP) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

3.23 Digital filter for sigma-delta modulators (DFSDM) . . . . . . . . . . . . . . . . . . 38

3.24 Digital camera interface (DCMI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

3.25 LCD-TFT controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

3.26 JPEG Codec (JPEG) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

3.27 Random number generator (RNG) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

3.28 Timers and watchdogs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

3.28.1 High-resolution timer (HRTIM1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

3.28.2 Advanced-control timers (TIM1, TIM8) . . . . . . . . . . . . . . . . . . . . . . . . . 43

3.28.3 General-purpose timers (TIMx) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

3.28.4 Basic timers TIM6 and TIM7 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

3.28.5 Low-power timers (LPTIM1, LPTIM2, LPTIM3, LPTIM4, LPTIM5) . . . . 44

3.28.6 Independent watchdogs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

3.28.7 Window watchdogs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

3.28.8 SysTick timer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

3.29 Real-time clock (RTC), backup SRAM and backup registers . . . . . . . . . . 45

3.30 Inter-integrated circuit interface (I

2

C) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

3.31 Universal synchronous/asynchronous receiver transmitter (USART) . . . 46

3.32 Low-power universal asynchronous receiver transmitter (LPUART) . . . . 47

3.33 Serial peripheral interface (SPI)/inter- integrated sound interfaces (I2S) . 48

3.34 Serial audio interfaces (SAI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

3.35 SPDIFRX Receiver Interface (SPDIFRX) . . . . . . . . . . . . . . . . . . . . . . . . . 49

3.36 Single wire protocol master interface (SWPMI) . . . . . . . . . . . . . . . . . . . . 49

3.37 Management Data Input/Output (MDIO) slaves . . . . . . . . . . . . . . . . . . . . 50

3.38 SD/SDIO/MMC card host interfaces (SDMMC) . . . . . . . . . . . . . . . . . . . . 50

3.39 Controller area network (FDCAN1, FDCAN2) . . . . . . . . . . . . . . . . . . . . . 50

3.40 Universal serial bus on-the-go high-speed (OTG_HS) . . . . . . . . . . . . . . . 51

3.41 Ethernet MAC interface with dedicated DMA controller (ETH) . . . . . . . . . 51

DS12923 Rev 1 5/252

STM32H745xI/G Contents

6

3.42 High-definition multimedia interface (HDMI)

- consumer electronics control (CEC) . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

3.43 Debug infrastructure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

4 Memory mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

5 Pin descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

6 Electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

6.1 Parameter conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

6.1.1 Minimum and maximum values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

6.1.2 Typical values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

6.1.3 Typical curves . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

6.1.4 Loading capacitor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

6.1.5 Pin input voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

6.1.6 Power supply scheme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 106

6.1.7 Current consumption measurement . . . . . . . . . . . . . . . . . . . . . . . . . . 107

6.2 Absolute maximum ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 107

6.3 Operating conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

6.3.1 General operating conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

6.3.2 VCAP external capacitor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 112

6.3.3 SMPS step-down converter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

6.3.4 Operating conditions at power-up / power-down . . . . . . . . . . . . . . . . . 114

6.3.5 Embedded reset and power control block characteristics . . . . . . . . . . 115

6.3.6 Embedded reference voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 116

6.3.7 Supply current characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 117

6.3.8 Wakeup time from low-power modes . . . . . . . . . . . . . . . . . . . . . . . . . . 137

6.3.9 External clock source characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . 138

6.3.10 Internal clock source characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . 142

6.3.11 PLL characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 145

6.3.12 Memory characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 147

6.3.13 EMC characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 148

6.3.14 Absolute maximum ratings (electrical sensitivity) . . . . . . . . . . . . . . . . 150

6.3.15 I/O current injection characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . 151

6.3.16 I/O port characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 152

6.3.17 NRST pin characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 159

6.3.18 FMC characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 159

剩余251页未读,继续阅读

weixin_47201184

- 粉丝: 0

- 资源: 4

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论0