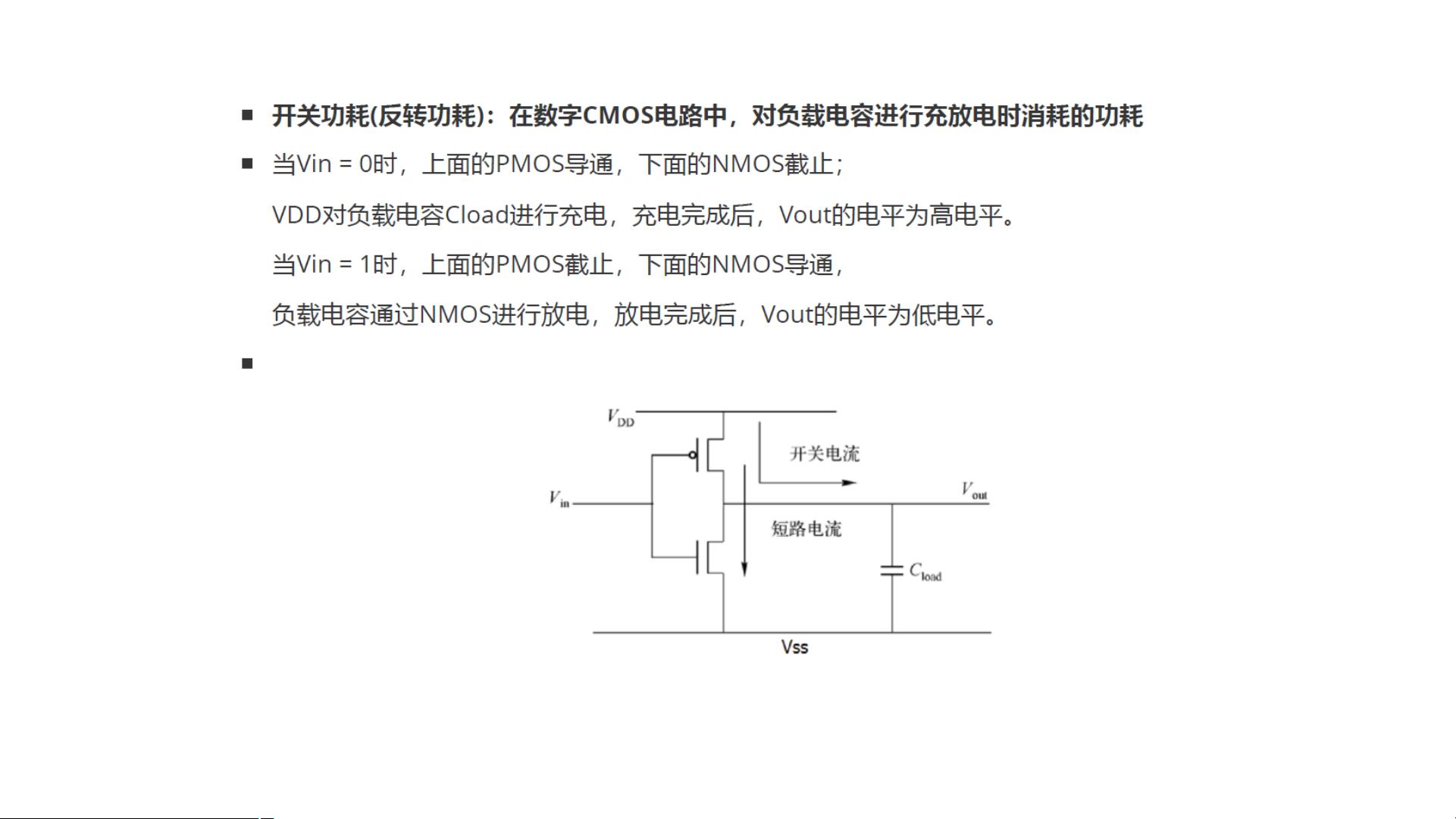

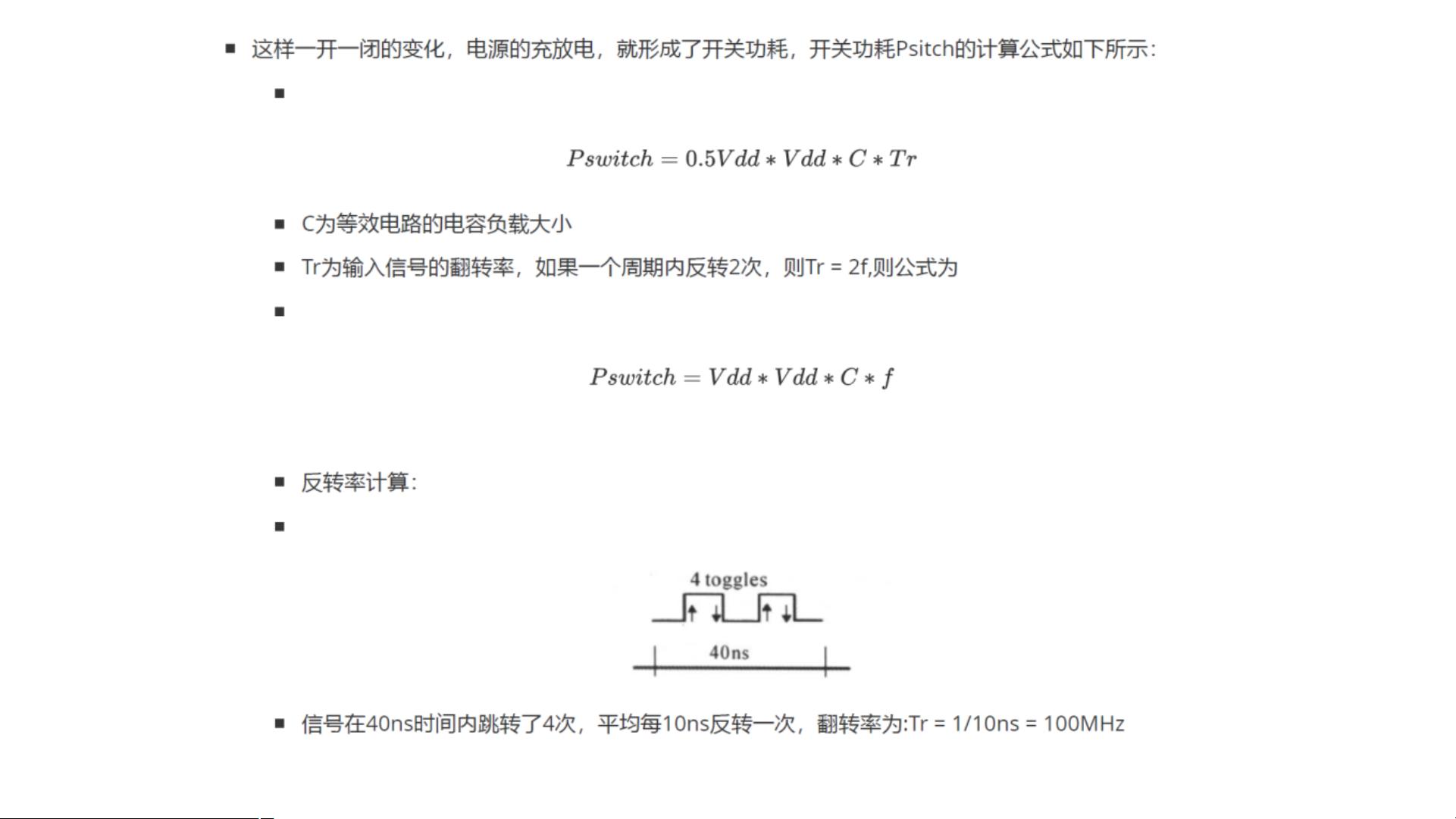

### 数字IC\FPGA低功耗设计 #### 一、芯片功耗的构成 在讨论数字集成电路(Digital IC)及现场可编程门阵列(FPGA)的低功耗设计之前,我们首先需要理解芯片功耗的基本构成。芯片功耗主要分为两大类:动态功耗和静态功耗。 1. **动态功耗**: - **开关功耗**:当信号通过晶体管时,由于电容充放电而产生的能量损耗。 - **短路功耗**:在逻辑门中,由于晶体管的短暂导通状态导致电流直接从电源到地,从而产生的功耗。 - **浪涌功耗**:电路转换过程中瞬时电流的增加,通常是由于电路状态改变时的暂态过程造成的。 2. **静态功耗**: - 静态功耗是指电路处于静态状态时的功耗,即电路不进行任何计算或状态变化时的功耗。主要包括漏电流功耗等。 #### 二、低功耗设计策略 为了降低芯片的功耗,可以从多个层次上进行优化设计: 1. **系统与架构级**: - 在这个级别上,主要是从整体系统的角度考虑如何降低功耗。例如,可以通过改变数据流和控制流来减少不必要的计算,或者利用动态电压和频率调整技术(DVFS)来根据任务需求调节电压和频率。 - **节省70%以上的功耗**:在这个层次上的设计优化通常可以带来显著的节能效果,因为它们针对的是整个系统的运行模式和结构,而非单一的逻辑单元或电路。 2. **RTL级(寄存器传输级)**: - 在这一层面上,设计人员可以通过选择不同的算法或数据表示方式来减少功耗。此外,还可以采用一些特定的技术来降低功耗,如: - **Verilog可实现的低功耗设计**:利用Verilog硬件描述语言中的特性来减少功耗。这包括使用条件编译、循环展开等技术来减少不必要的逻辑操作。 - **多阈值电压设计**:利用不同阈值电压的晶体管(HVT/LVT/SVT)来平衡性能和功耗的需求。一般来说,高阈值电压(HVT)晶体管具有较低的功耗但较高的延迟,而低阈值电压(LVT)晶体管则相反。 - **电源门控**:通过关闭未使用的电路区域的电源来降低功耗。 - **减少负载电容**:通过减少信号线的负载电容来降低开关功耗。 3. **门级**: - 在门级层面,设计人员可以通过优化逻辑门的连接和布局来减少功耗。例如,减少门之间的连线长度可以降低开关功耗;选择合适的逻辑门类型也可以帮助降低功耗。 - 具体来说,可以通过以下几种方法: - 减少负载电容:通过优化门的输入和输出结构来降低每个门的电容负载。 - 电源门控:在某些情况下,可以考虑将电源门控技术应用到门级设计中,以进一步降低功耗。 - 工艺库的选择:使用具有低功耗特性的工艺库来进行设计。 数字IC和FPGA的低功耗设计是一项多方面的工程,涉及从系统级到门级等多个层次的设计优化。通过综合运用上述策略和技术,可以有效降低芯片的整体功耗,从而提高能效并延长电池寿命。

- 粉丝: 0

- 资源: 1

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功