没有合适的资源?快使用搜索试试~ 我知道了~

506549_Grantley_PDG_506549_v1.5.2

需积分: 35 20 下载量 135 浏览量

2019-04-14

20:41:10

上传

评论 1

收藏 32.56MB PDF 举报

温馨提示

试读

830页

506549_Grantley_PDG_506549_v1.5.2The Grantley platform consists of the Haswell-EP processor, Haswell-EP 4S processor or Haswell-EN processor used in conjunction with the Wellsburg PCH. This is a twochip platform as opposed to traditional three-chip platforms (CPU, Memory Controller and I/O Controller) made possible because this family of processors includes an integrated memory controller (IMC) and integrated I/O (IIO) (such as PCI Express* and DMI2) on a single silicon die. The Grantley platform supports only a single PCH connected to CPU0.

资源推荐

资源详情

资源评论

Grantley

Platform Design Guide

April 2014

Intel Confidential

Doc. No.: 506549, Rev.: 1.5.2

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR

OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND

CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED

WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A

PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

A "Mission Critical Application" is any application in which failure of the Intel Product could result, directly or indirectly, in personal injury or death.

SHOULD YOU PURCHASE OR USE INTEL'S PRODUCTS FOR ANY SUCH MISSION CRITICAL APPLICATION, YOU SHALL INDEMNIFY AND HOLD INTEL AND

ITS SUBSIDIARIES, SUBCONTRACTORS AND AFFILIATES, AND THE DIRECTORS, OFFICERS, AND EMPLOYEES OF EACH, HARMLESS AGAINST ALL

CLAIMS COSTS, DAMAGES, AND EXPENSES AND REASONABLE ATTORNEYS' FEES ARISING OUT OF, DIRECTLY OR INDIRECTLY, ANY CLAIM OF

PRODUCT LIABILITY, PERSONAL INJURY, OR DEATH ARISING IN ANY WAY OUT OF SUCH MISSION CRITICAL APPLICATION, WHETHER OR NOT INTEL

OR ITS SUBCONTRACTOR WAS NEGLIGENT IN THE DESIGN, MANUFACTURE, OR WARNING OF THE INTEL PRODUCT OR ANY OF ITS PARTS.

Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or

characteristics of any features or instructions marked "reserved" or "undefined". Intel reserves these for future definition and shall have no

responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The information here is subject to change without

notice. Do not finalize a design with this information.

The products described in this document may contain design defects or errors known as errata which may cause the product to deviate from published

specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an order number and are referenced in this document, or other Intel literature, may be obtained by calling

1-800-548-4725, or go to: http://www.intel.com/design/literature.htm

Any software source code reprinted in this document is furnished under a software license and may only be used or copied in accordance with the

terms of that license.

This document contains information on products in the design phase of development.

Intel processor numbers are not a measure of performance. Processor numbers differentiate features within each processor family, not across different

processor families: Go to: http://www.intel.com/products/processor_number

Code Names are only for use by Intel to identify products, platforms, programs, services, etc. ("products") in development by Intel that have not been

made commercially available to the public, i.e., announced, launched or shipped. They are never to be used as "commercial" names for products. Also,

they are not intended to function as trademarks.

Intel

®

High Definition Audio (Intel

®

HD Audio) requires an Intel

®

HD Audio enabled system. Consult your PC manufacturer for more information.

Sound quality will depend on equipment and actual implementation. For more information about Intel

®

HD Audio, refer to http://www.intel.com/

design/chipsets/hdaudio.htm.

Intel

®

64 architecture requires a system with a 64-bit enabled processor, chipset, BIOS and software. Performance will vary depending on the specific

hardware and software you use. Consult your PC manufacturer for more information. For more information, visit http://www.intel.com/

content/www/us/en/architecture-and-technology/microarchitecture/intel-64-architecture-general.html.

Intel

®

Virtualization Technology (Intel

®

VT) requires a computer system with an enabled Intel

®

processor, BIOS, and virtual machine monitor (VMM).

Functionality, performance or other benefits will vary depending on hardware and software configurations. Software applications may not be

compatible with all operating systems. Consult your PC manufacturer. For more information, visit http://www.intel.com/go/virtualization.

The original equipment manufacturer must provide TPM functionality, which requires a TPM-supported BIOS. TPM functionality must be initialized and

may not be available in all countries.

No computer system can provide absolute security under all conditions. Intel

®

Trusted Execution Technology (Intel

®

TXT) requires a computer with

Intel

®

Virtualization Technology, an Intel TXT-enabled processor, chipset, BIOS, Authenticated Code Modules and an Intel TXT-compatible measured

launched environment (MLE). Intel TXT also requires the system to contain a TPM v1.s. For more information, visit http://www.intel.com/technology/

security.

BlueMoon, BunnyPeople, Celeron, Celeron Inside, Centrino, Centrino Inside, Cilk, Core Inside, E-GOLD, i960, Intel, the Intel logo, Intel AppUp, Intel

Atom, Intel Atom Inside, Intel Core, Intel Inside, Intel Insider, the Intel Inside logo, Intel NetBurst, Intel NetMerge, Intel NetStructure, Intel

SingleDriver, Intel SpeedStep, Intel Sponsors of Tomorrow., the Intel Sponsors of Tomorrow. logo, Intel StrataFlash, Intel vPro, Intel XScale, InTru,

the InTru logo, the InTru Inside logo, InTru soundmark, Itanium, Itanium Inside, MCS, MMX, Moblin, Pentium, Pentium Inside, Puma, skoool, the

skoool logo, SMARTi, Sound Mark, The Creators Project, The Journey Inside, Thunderbolt, Ultrabook, vPro Inside, VTune, Xeon, Xeon Inside, X-GOLD,

XMM, X-PMU and XPOSYS are trademarks of Intel Corporation in the U.S. and/or other countries.

*Other names and brands may be claimed as the property of others.

Copyright

©

2012–2014, Intel Corporation. All rights reserved.

Grantley

Platform Design Guide April 2014

2 Intel Confidential Doc. No.: 506549, Rev.: 1.5.2

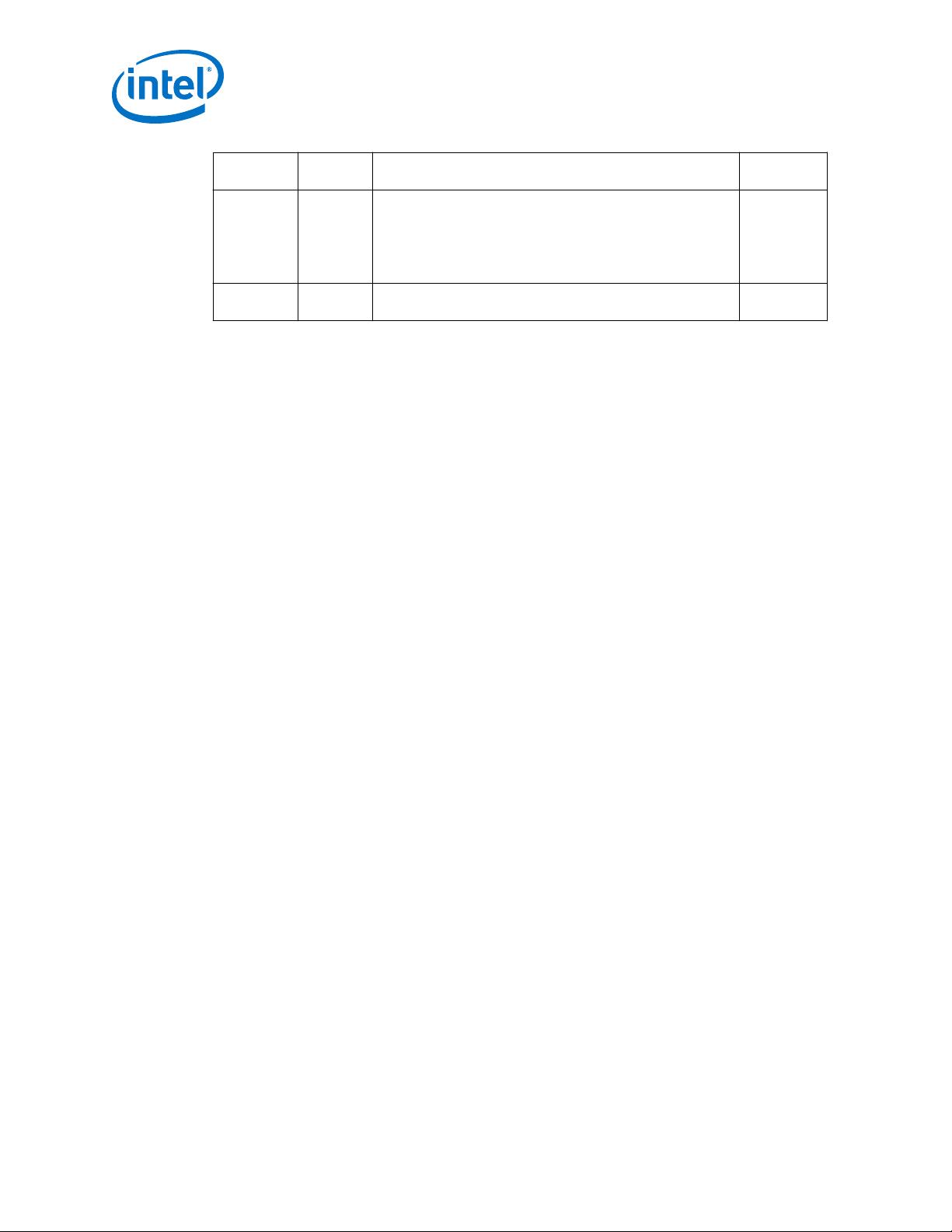

Revision History

Document

Number

Revision

Number

Description Revision

Date

506549 1.5.2 • Chapter 4: Platform Clocking chapter updated with new

guidelines

• Chapter 6: Fixed typo in DDR4 section for "DDR4 Source-

Synchronous Signal Group Routing Guidelines, 3SPC", Table

176.

— Changed "DQ/ECC Characteristic Trace Impedance (Zo),"

stripline, from 8 ohms to 38 ohms.

• Chapter 13: Table 422, deleted SKUs: 130W and 80W.

Chapter 13: Table 429, edited Skt VDDQ loading and

expanded Note #5.

Chapter 13.3.4, PVDDQ DDR3 VR, fixed typos.

April 2014

506549 1.5.1 • Ch 3: Fiberweave guidelines updated for more accurate

wording

• Ch 4: added note to PCI 33mhz double loaded clocks

• Ch 7: Updated Trace Spacing and length requirements in the

DIMM Pin Field and for 2SPC and 1SPC

• Ch 7: Updated DDR3 DIMM Reference Voltage Guidelines

VREFDQ filter circuit

• Ch 12: update to HSW-EN top side probe for 2S

• Ch 13:Grantley Platf Pwr Distrib Guidelines - cleanup typos

• Ch 13.2.1: PVCCIN_CPUx VR12.5 Output Guidelines for

HSX-EP/-EN, Table 421 - updated and Notes added

• Ch 13.2.1.4: VR Ready Output - updated

• Ch 13.3.1: PVDDQ DDR4 VR Recommendations, Table 428 -

updated and Note added.

• Ch PVPP_DDRxx VR Recommendations, Table 433 -

updated.

• Ch 13.6: Fast PROCHOT# Protection, Fig. 503 - Note added.

• Ch 13.7: Related Documents Table - added.

February

2014

506549 1.5 • Added EN guidelines throughout PDG

• Various updates to interfaces; updates are marked with

change bars

September

2013

506549 1.2 • Added guidelines for Polarity swap

• Updated guidelines for dualstrip line and broadside coupling

• Added stack up diagram for PCIe riser, and various updates

to stack up diagrams

• Various updates to interfaces.

April 2013

506549 1.0 • Added 10 layer and 12 layer stack up guidelines

• Removed DDR3 EN socket B3 recommendations. Design

rules for DDR3 socket R3 are still WIP

• Updated EP design guidelines to all sections.

October

2012

506549 0.7 • CPU: updated EP information, and added brand new EN

content.

• Wellsburg PCH: updates to SATA, USB, USB 3.0, PCIe*/DMI,

power delivery, SPI, Intel

®

ME, SMLink, Intel

®

HD audio

July 2012

continued...

Revision History—Grantley

Grantley

April 2014 Platform Design Guide

Doc. No.: 506549, Rev.: 1.5.2 Intel Confidential 3

Document

Number

Revision

Number

Description Revision

Date

• Power delivery updates: Aztec City power block diagram,

CPU power delivery, PVCCIN VR load limits & caps, VccIN

load line, Vccin Dyn load description, Mayan C CRB layout,

Aztec C CRB layout, DDR4 Mem DIMMS power delivery, Fast

ProcHOT for CPU and system PSU's (new)

• Misc: Added x540 Ethernet controller information

31272 0.5 Initial release of the document February

2012

Grantley—Revision History

Grantley

Platform Design Guide April 2014

4 Intel Confidential Doc. No.: 506549, Rev.: 1.5.2

Contents

Revision History..................................................................................................................3

1.0 Introduction and Overview......................................................................................... 39

1.1 Grantley Platform Overview....................................................................................40

1.2 Document Scope / PDG Disclaimer.......................................................................... 41

2.0 Stack-up, Placement and PCB Guidelines.................................................................... 43

2.1 Board Stack-ups................................................................................................... 43

2.1.1 8-Layer FR4 Stack-up................................................................................43

2.1.2 14-Layer FR4 Stack-up.............................................................................. 44

2.1.3 10-Layer Dual Stripline FR4 Stack-up.......................................................... 46

2.1.4 12-Layer Dual-stripline Half-width FR4 Stack-up........................................... 46

2.2 Common Field Solved Impedance Table................................................................... 47

2.3 High-Speed PCB Loss............................................................................................ 50

2.3.1 High Speed Differential Loss Magnitude Requirement..................................... 51

2.3.2 Insertion Loss and Measurement.................................................................51

2.3.3 Humidity Impact on Loss........................................................................... 55

2.4 Component Quadrant Layouts................................................................................ 56

2.4.1 Haswell-EP/EP 4S Processor Quadrant Layout............................................... 57

2.4.2 Haswell-EN Processor Quadrant Layout........................................................ 57

2.4.3 Wellsburg PCH Quadrant Layout..................................................................58

3.0 General High Speed Guidelines................................................................................... 60

3.1 Length Matching Requirements............................................................................... 60

3.2 Routing Clearance from Vertical Features................................................................. 68

3.3 Controlling Voltage Regulator VR Noise.................................................................... 69

3.4 Reference Plane....................................................................................................74

3.5 Escape Routing.....................................................................................................77

3.6 Routing Through or Escaping a Pin Field...................................................................82

3.7 Layer Transitions and Via Stubs.............................................................................. 84

3.8 Connector Routing Guideline.................................................................................. 90

3.9 Routing Under Connector Footprint..........................................................................91

3.10 PCIe* and DMI2 General Routing Guidelines........................................................... 93

3.11 Signal Integrity Guidelines................................................................................... 94

3.12 Dual Stripline Routing Guidelines...........................................................................99

3.13 Signal Polarity Considerations............................................................................. 106

3.14 Recessed Ground Plane for Edge Card Connector................................................... 111

4.0 Platform Clocking......................................................................................................113

4.1 General Routing Guidelines for Reference Clocks..................................................... 113

4.2 Platform Clocks with extCLK Solution..................................................................... 115

4.2.1 Clock Generator and Buffer Settings.......................................................... 116

4.2.2 General Routing Rules for extCLK Mode......................................................116

4.2.3 Reference Board Topology Examples (extCLK).............................................119

4.2.4 Clock Driver Decoupling and Clock Power Delivery....................................... 142

4.2.5 CK420BQ Power Plane Filtering................................................................. 143

4.2.6 DB1x00Z ZL Power Plane Filtering............................................................. 144

4.2.7 EMI Constraints...................................................................................... 144

Contents—Grantley

Grantley

April 2014 Platform Design Guide

Doc. No.: 506549, Rev.: 1.5.2 Intel Confidential 5

剩余829页未读,继续阅读

资源评论

weixin_44919540

- 粉丝: 0

- 资源: 2

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功