qiangdaqi.rar_VHDL qiangdaqi_抢答器_电子抢答器

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

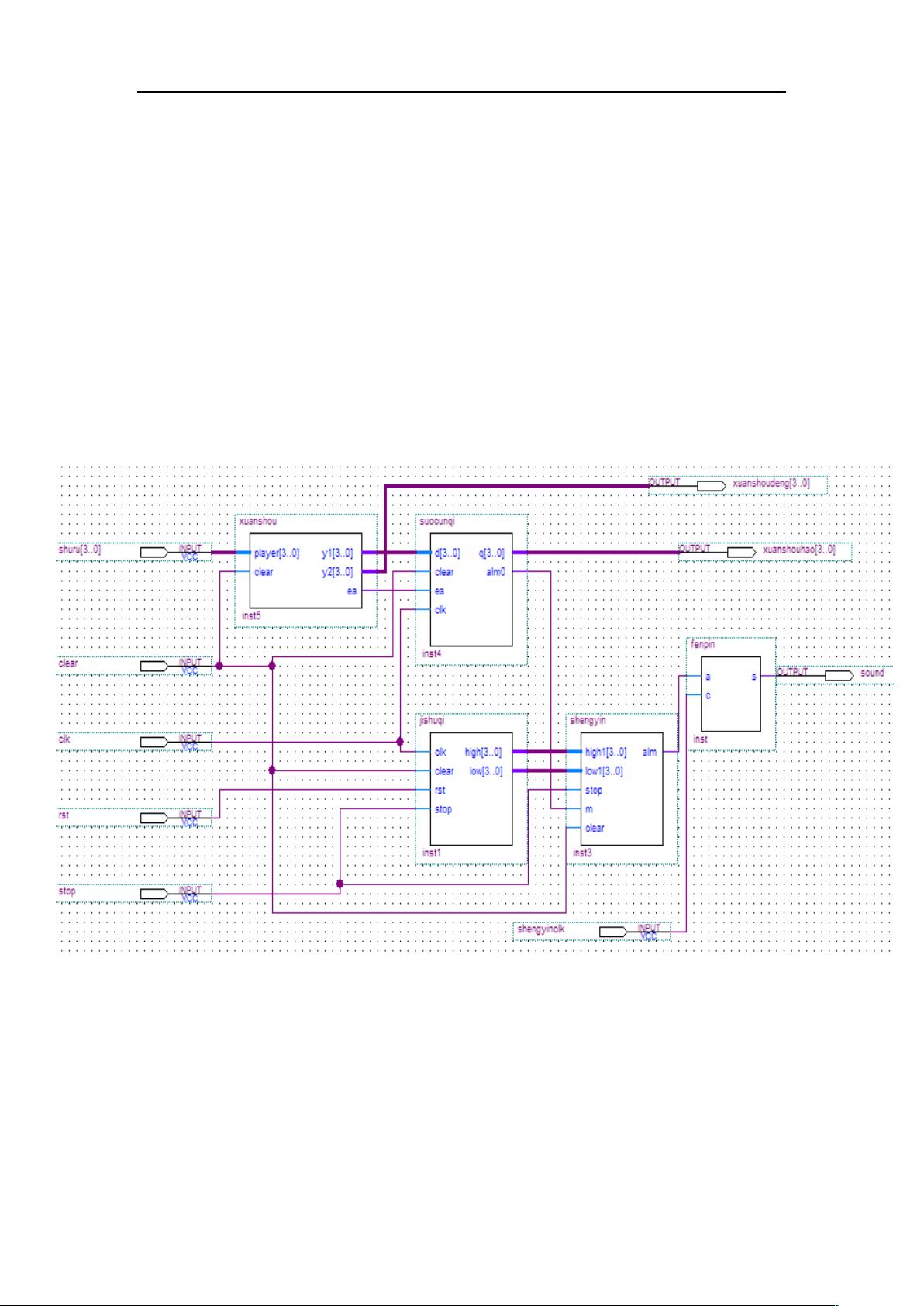

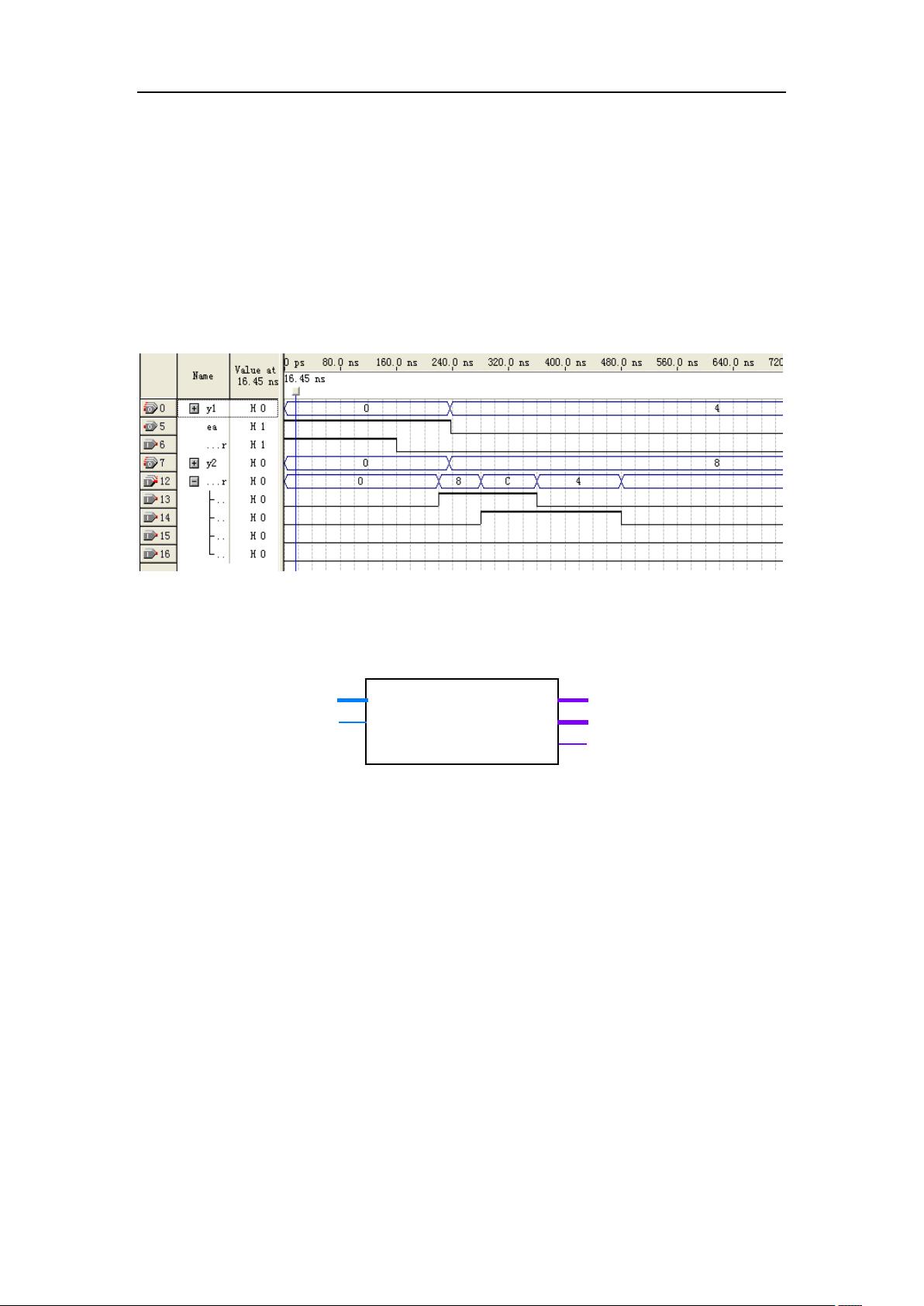

《基于VHDL的电子抢答器设计与实现》 在现代科技的推动下,电子抢答器已经广泛应用于各种知识竞赛、娱乐节目等场合,它不仅能够公正、公平地判断选手的抢答顺序,还提供了计分、计时等多种功能,大大提升了活动的趣味性和互动性。本设计以“qiangdaqi.rar”为载体,详细阐述了一款基于VHDL语言的电子抢答器的设计原理与实现方法。 VHDL(VHSIC Hardware Description Language),即超高速集成电路硬件描述语言,是电子设计自动化(EDA)领域的重要工具,用于描述数字系统的结构和行为。在电子抢答器的设计中,VHDL被用来编写逻辑电路的代码,实现抢答器的控制逻辑、计时逻辑以及显示逻辑。 该电子抢答器支持八位选手同时参与,这意味着需要设计一个8输入的抢答信号检测电路。在VHDL中,我们可以定义一个8位的并行输入信号,当任意一位选手按下抢答按钮时,对应的输入信号变为高电平。为了防止多个选手同时按下按钮导致的冲突,还需要设置优先级判断电路,确保最先按下按钮的选手能够成功触发抢答。 报警功能是抢答器的关键部分,它需要在有选手成功抢答后立即发出信号,提醒裁判和其他选手。这一功能可以通过一个计数器来实现,当检测到有效的抢答信号时,计数器清零并开始计数,达到预设值时触发报警电路。报警信号可以通过LED灯闪烁或者蜂鸣器发声等形式体现。 再者,计分系统则需要记录每个选手的得分情况。可以设计一个带有加法逻辑的计分模块,每次抢答成功后,对应选手的分数增加。为了保证计分的准确性和可读性,可能需要将计分结果显示在LCD显示器上,这需要额外的驱动电路和数据处理。 计时功能通常包括答题时间和倒计时两种模式。答题时间可以设定一个固定的时间段,当开始答题后开始倒计时,到达预设时间后停止计时;倒计时模式则是允许选手在规定时间内自由抢答,时间耗尽后结束抢答。 在“qiangdaqi.doc”文档中,详细描述了以上各个部分的设计细节和VHDL代码实现,包括模块划分、接口定义、时序逻辑和状态机设计等。通过阅读这份文档,读者可以深入理解如何利用VHDL语言构建一个完整的电子抢答系统,同时也能了解到数字电路设计的基本流程和方法。 总结来说,这款“qiangdaqi.rar”中的电子抢答器设计,涵盖了VHDL编程、数字逻辑设计、系统集成等多个方面,是学习和实践数字系统设计的优秀实例。通过这样的项目,不仅可以提升对VHDL的理解,还能锻炼解决实际问题的能力,对于电子工程和计算机科学的学习者来说,具有很高的参考价值。

qiangdaqi.rar (1个子文件)

qiangdaqi.rar (1个子文件)  qiangdaqi.doc 123KB

qiangdaqi.doc 123KB- 1

- 粉丝: 91

- 资源: 1万+

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- IPinfo API 的官方 Java 库(IP 地理位置和其他类型的 IP 数据).zip

- IntelliJ IDEA 针对 Square 的 Java 和 Android 项目的代码样式设置 .zip

- Gradle,Maven 插件将 Java 应用程序打包为原生 Windows、MacOS 或 Linux 可执行文件并为其创建安装程序 .zip

- Google Maps API Web 服务的 Java 客户端库.zip

- Google Java 核心库.zip

- GitBook 教授 Javascript 编程基础知识.zip

- Generation.org 开发的 JAVA 模块练习.zip

- FastDFS Java 客户端 SDK.zip

- etcd java 客户端.zip

- Esercizi di informatica!执行计划,metti alla prova!.zip

信息提交成功

信息提交成功