四人抢答器设计报告

一、设计任务及要求

1、设计用于竞赛的四人抢答器

(1)有多路抢答器,台数为四;

(2)具有抢答开始后 20 秒倒计时,20 秒倒计时后无人抢答显示超时,并报

警;

(3)能显示超前抢答台号并显示犯规报警;

2、系统复位后进入抢答状态,当有一路抢答键按下时,该路抢答信号将其余各

路抢答封锁,同时铃声响起,直至该路按键放松,显示牌显示该路抢答台号;

3、用 VHDL 语言设计符合上述功能要求的四人抢答器,并用层次设计方法设

计该电路;

4、完成电路全部设计后,通过系统实验箱下载验证设计课题的正确性。

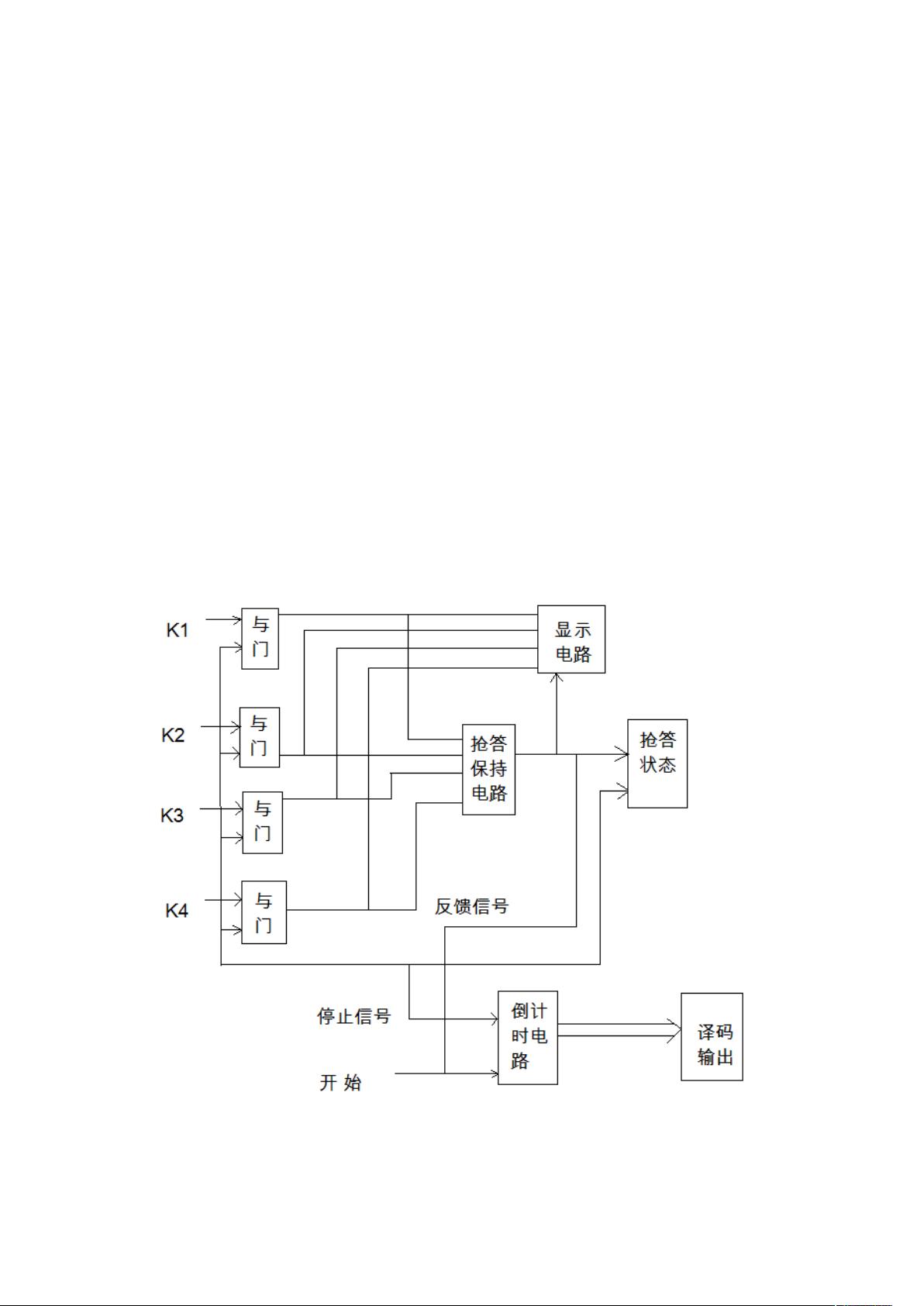

二、四人抢答器框图及设计说明

系统复位后,反馈信号为一个高电平,K1、K2、K3、K4 输入有效。当抢

答开始后,在第一位按键后,保持电路低电平,同时送显示电路,让其保存按

键的台号并输出,同时反馈给抢答台,使所有抢答台输入无效,计时电路停止;

当在规定的时间内无人抢答时,倒计时电路输出超时信号;当主持人开始说话

未说完有人抢先按键时,显示犯规信号。当选手回答正确时加分,回答错误时

减分。由主持人控制加减分数。

三、设计思路:根据设计框图和设计要求,本次实验可以采用模块化设计方法

来实现智力竞赛四人抢答器。将抢答器划分为抢答鉴别保持模块,倒计时模块,

记分模块和判断显示模块。再利用元件例化语句将这四个模块组成总的抢答器

的设计电路。选用模式五进行程序的下载。

四、VHDL 语言设计与分析

1、鉴别模块

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity jianbie is

port(nu1,nu2,nu3,nu4:in std_logic;

clk,en,rst:in std_logic;

warn:out std_logic;

back:buffer std_logic;

s:out std_logic_vector(3 downto 0));

end jianbie;

architecture jianbiebeh of jianbie is

signal num,warnd:std_logic;

signal cnt:std_logic_vector(2 downto 0);

begin

num<=nu1 or nu2 or nu3 or nu4;

p1:process(rst, nu1,nu2,nu3,nu4,back) --判断抢答信号

begin

if rst='1' then back<='1';s<="0000";

elsif back='1' then

if nu1='1' then s<="0001";back<='0'; --一号台抢答,输出 S 为 1

elsif nu2='1' then s<="0010";back<='0'; --二号台抢答,输出 S 为 2

elsif nu3='1' then s<="0011";back<='0'; --三号台抢答,输出 S 为 3

elsif nu4='1' then s<="0100";back<='0'; --四号台抢答,输出 S 为 4

else back<='1'; s<="0000"; --无人抢答,输出 S 为 0

end if ;

end if;

end process p1;

p2:process(clk,en,back,rst,cnt)

begin

if rst='1' then cnt<="000";warnd<='0';

elsif clk'event and clk='1' then

if en='0' and back='0' then

if cnt<"111" then warnd<=not warnd; cnt<=cnt+1;

else warnd<='0';

end if; end if;

end if;

end process p2;

warn<=warnd;

end jianbiebeh;

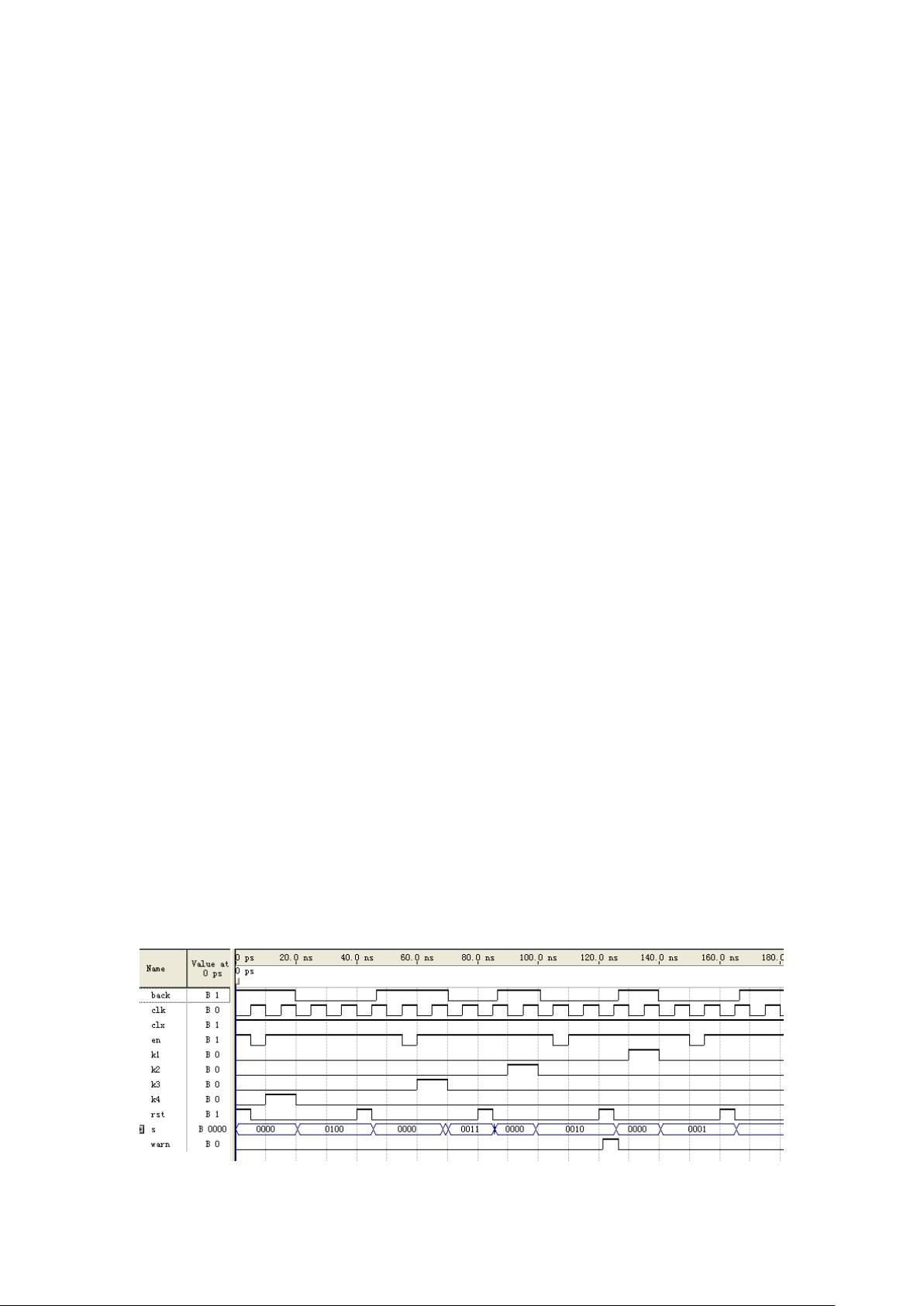

鉴别保持模块由两个进程组成,进程一主要用于鉴别强大信号,进程二用于

鉴别是否为超前抢答,若是超前抢答,则输出报警信号。其中鉴别保持模块的

波形如下:

如图所示,抢答开始前需要一个 RST 信号,其由主持人控制。当 RST 为

高电平时则抢答开始。输出 S 显示为抢答台号,当主持人还没有复位就有选手

抢答,则输出一个 WARN 的高电平信号。

2、计时模块

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity jishibaojing is

port(clk,rst,agree,stop:in std_logic;

warn:buffer std_logic;

cone:buffer std_logic_vector(3 downto 0);

cten:buffer std_logic_vector(3 downto 0));

end jishibaojing;

architecture jishibeh of jishibaojing is

signal cc:std_logic;

begin

p1:process(warn,clk,rst,agree,stop,cone) --个位计时

begin

if rst='1' then cone<="0000";

elsif stop='0' then cten<="0000";

elsif clk'event and clk='1' then cc<='0';

if agree='1' and warn='0' then cone<=cone-1;

if cone="0000" then cone<="1001";cc<='1'; end if;

end if;

end if;

end process p1;

p2:process(cc,rst,agree,stop,cten) --十位计时

begin

if rst='1' then cten<="0010";

elsif stop='0' then cten<="0010";