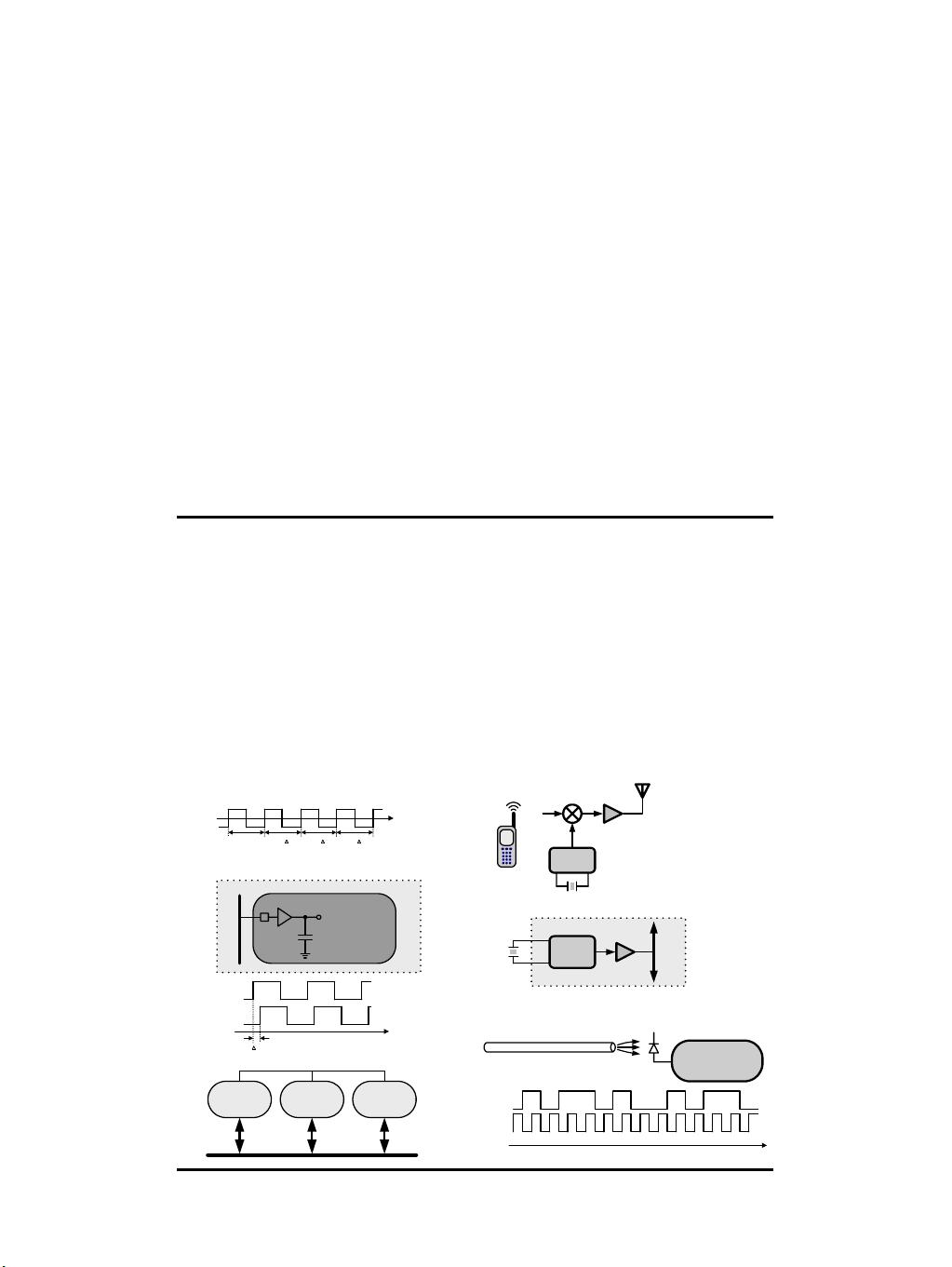

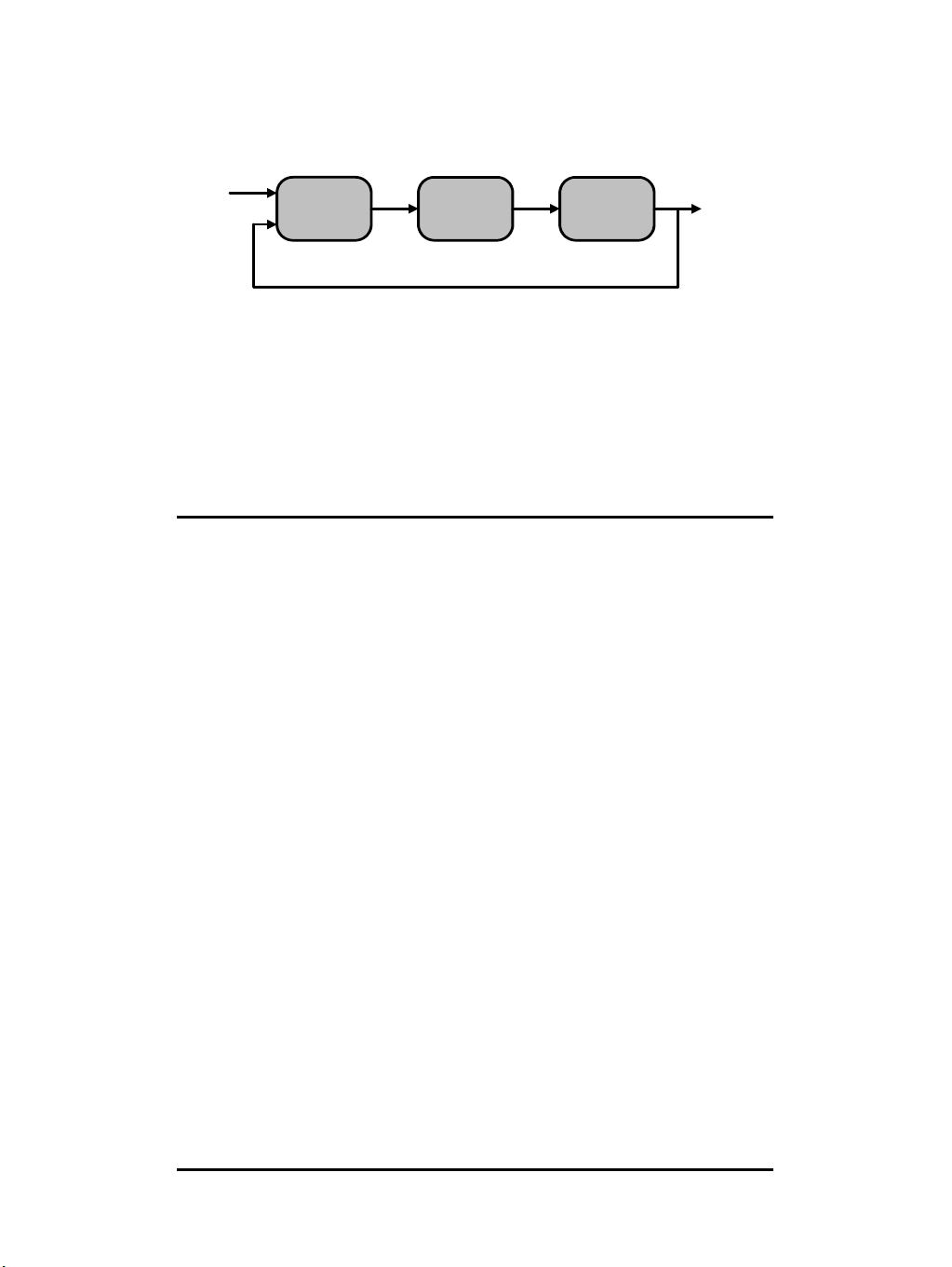

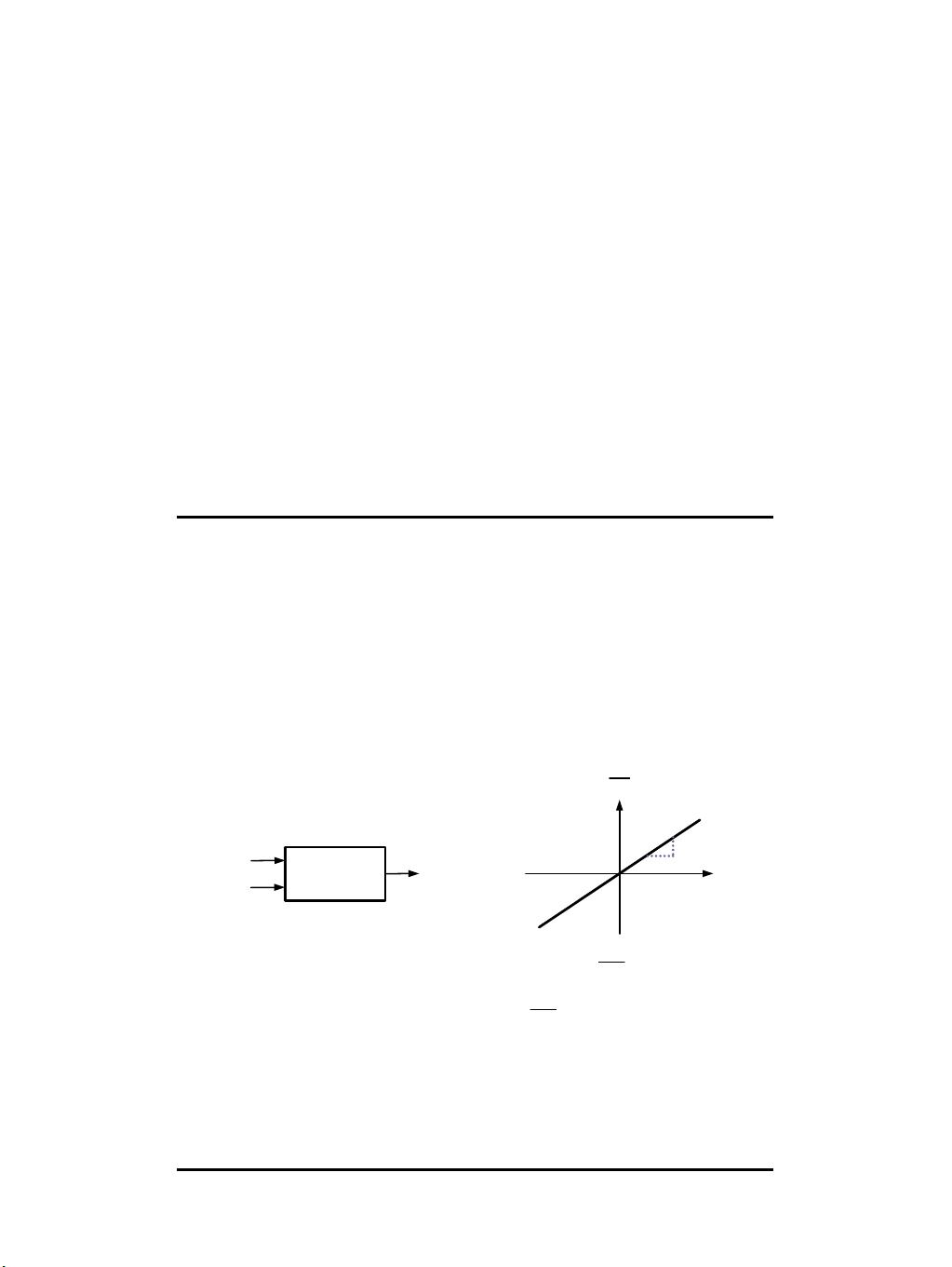

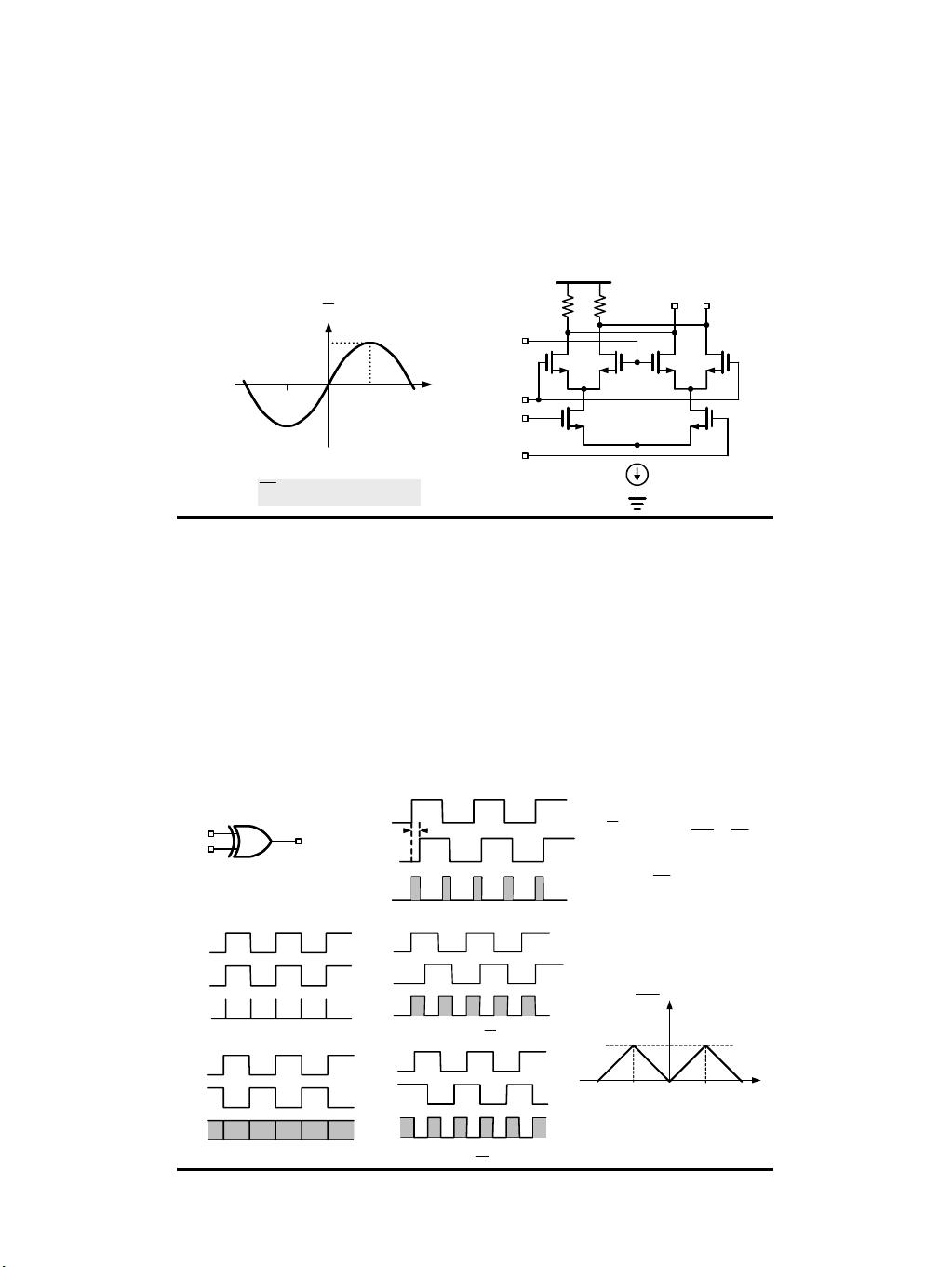

PLL,即Phase-Locked Loop(锁相环),是电子工程领域中一种重要的频率合成与相位控制技术。在通信、计算机、仪器仪表等众多领域都有着广泛的应用。锁相环能够实现信号间的频率同步,通过调整环路内的振荡器频率,使其与外部参考信号保持固定的相位关系,从而达到跟踪或锁定外部信号频率的目的。 PLL锁相环主要由以下几个关键组件构成: 1. **参考源(Reference Oscillator)**:提供稳定的参考频率,这是锁相环工作的基准。 2. **分频器(Divider)**:通常称为分频因子N,用于将参考频率降低到与振荡器可产生的频率相近。 3. **压控振荡器(VCO, Voltage-Controlled Oscillator)**:根据输入的控制电压改变其输出频率,是锁相环的核心部分。 4. **相位比较器(Phase Comparator)**:检测VCO输出信号与参考信号之间的相位差,并将其转换为电压信号。 5. **低通滤波器(LPF, Low-Pass Filter)**:平滑相位比较器输出的电压脉冲,只允许低频成分通过,形成控制电压供给VCO。 锁相环的工作原理可以简单概括为以下步骤: 1. VCO产生的信号经过分频器,其输出与参考信号进行相位比较。 2. 相位比较器将两者的相位差转换为电压信号。 3. 该电压信号通过LPF滤波,去除高频噪声,得到控制电压。 4. 控制电压作用于VCO,改变其输出频率,使得VCO信号的相位向参考信号靠近。 5. 当VCO输出信号与参考信号的相位差趋于零时,即实现了锁相,此时VCO频率被锁定在参考频率的整数倍上。 锁相环的设计主要包括以下几个方面: - **环路带宽(Loop Bandwidth)**:决定锁相环响应速度和稳定性的关键参数,过宽可能导致噪声引入,过窄则响应慢。 - **分频因子N**:需根据应用需求选择,以确保VCO频率与参考频率相匹配。 - **VCO的线性度**:保证控制电压与频率变化成线性关系,以确保良好的锁相性能。 - **低通滤波器设计**:选择合适的截止频率和滚降率,以平衡锁定速度和噪声抑制。 PLL的应用非常广泛,例如在数字通信系统中,用于频率合成、载波恢复、数据同步等;在数字电路中,用于时钟恢复和时钟同步;在模拟电路中,用于频率调制解调等。 "PLL.pdf" 这份文档很可能包含了关于PLL锁相环的详细设计方法、工作原理、应用实例以及相关的电路分析等内容,对于深入理解和研究锁相环技术极具价值。通过阅读这份资料,你可以更全面地掌握PLL的理论知识和实际应用技巧。

PLL.rar (1个子文件)

PLL.rar (1个子文件)  PLL.pdf 1.07MB

PLL.pdf 1.07MB- 1

- 粉丝: 97

- 资源: 1万+

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功

评论0