a

AD1896

*

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties that

may result from its use. No license is granted by implication or otherwise

under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective companies.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 www.analog.com

Fax: 781/326-8703 © 2003 Analog Devices, Inc. All rights reserved.

REV. A

192 kHz Stereo Asynchronous

Sample Rate Converter

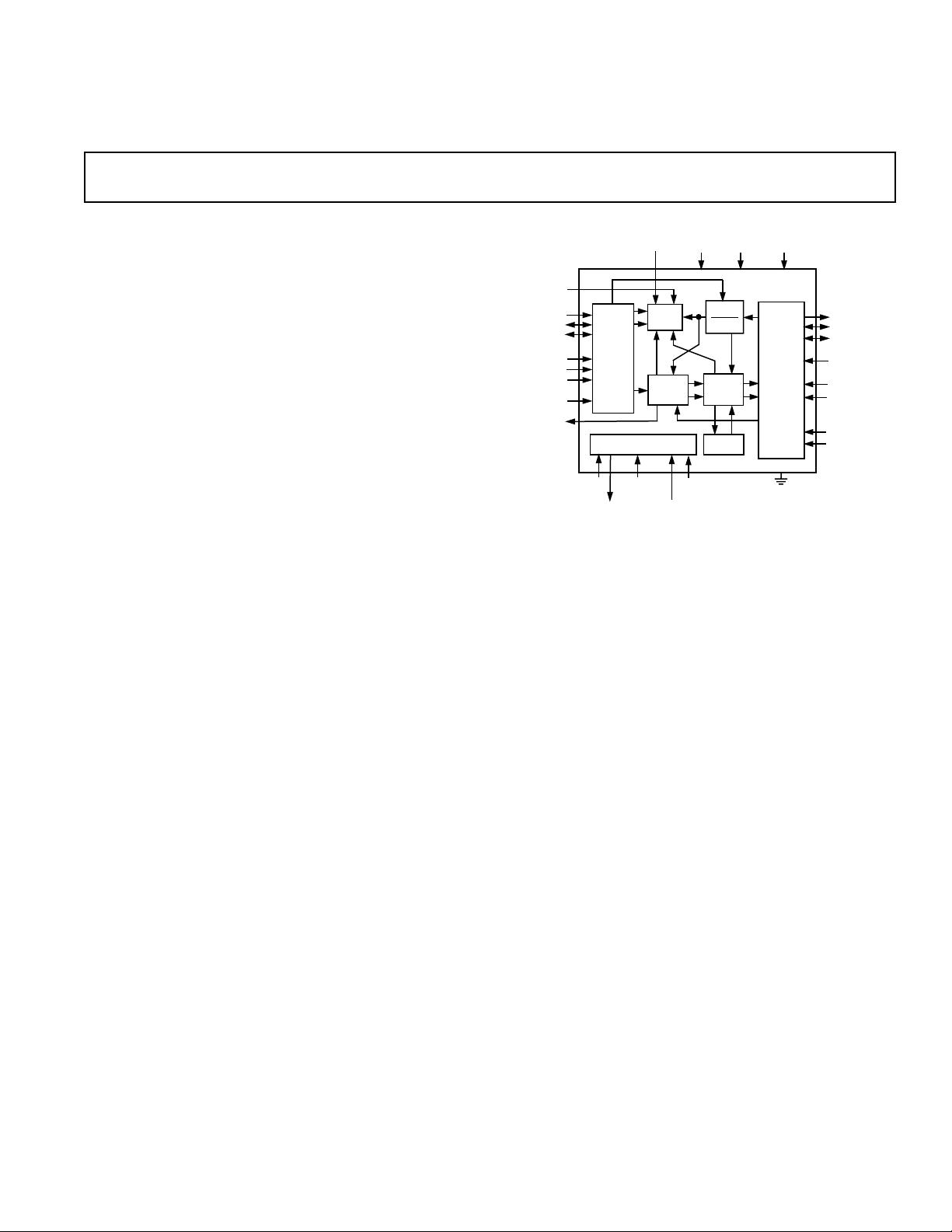

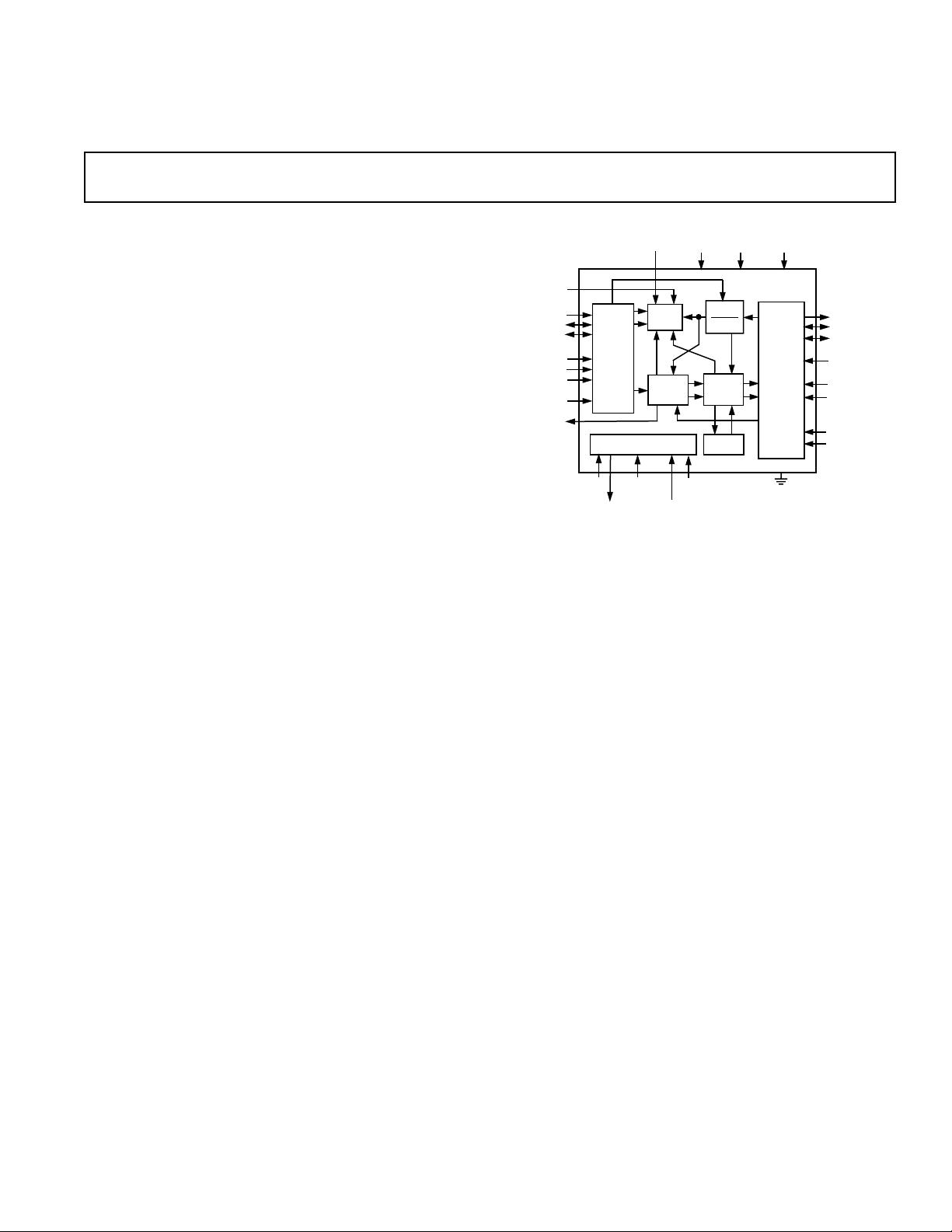

FUNCTIONAL BLOCK DIAGRAM

GRPDLYS VDD_IO

VDD_CORE

SERIAL

INPUT

FIFO

FS

OUT

FS

IN

SERIAL

OUTPUT

DIGITAL

PLL

FIR

FILTER

CLOCK DIVIDER

ROM

AD1896

BYPASS

MUTE_O

MUTE_I

SDATA_I

SCLK_I

LRCLK_I

SMODE_IN_0

SMODE_IN_1

SMODE_IN_2

MCLK_I

MCLK_O

MSMODE_0

MSMODE_2

MSMODE_1

WLNGTH_O_0

WLNGTH_O_1

SMODE_O_0

SMODE_O_1

TDM_IN

SDATA_O

SCLK_O

LRCLK_O

RESET

PRODUCT OVERVIEW

The AD1896 is a 24-bit, high performance, single-chip, second-

generation asynchronous sample rate converter. Based on Analog

Devices experience with its first asynchronous sample rate

converter, the AD1890, the AD1896 offers improved performance

and additional features. This improved performance includes a

THD + N range of –117 dB to –133 dB depending on the sample

rate and input frequency, 142 dB (A-Weighted) dynamic range,

192 kHz sampling frequencies for both input and output sample

rates, improved jitter rejection, and 1:8 upsampling and 7.75:1

downsampling ratios. Additional features include more serial

formats, a bypass mode, better interfacing to digital signal pro-

cessors, and a matched-phase mode.

The AD1896 has a 3-wire interface for the serial input and

output ports that supports left-justified, I

2

S, and right-justified

(16-, 18-, 20-, 24-bit) modes. Additionally, the serial output

port supports TDM mode for daisy-chaining multiple AD1896s to

a digital signal processor. The serial output data is dithered down

to 20, 18, or 16 bits when 20-, 18-, or 16-bit output data is se-

lected. The AD1896 sample rate converts the data from the

serial input port to the sample rate of the serial output port. The

sample rate at the serial input port can be asynchronous with

respect to the output sample rate of the output serial port. The

master clock to the AD1896, MCLK, can be asynchronous to

both the serial input and output ports.

MCLK can be generated either off-chip or on-chip by the AD1896

master clock oscillator. Since MCLK can be asynchronous to the

input or output serial ports, a crystal can be used to generate

MCLK internally to reduce noise and EMI emissions on the

board. When MCLK is synchronous to either the output or input

serial port, the AD1896 can be configured in a master mode where

MCLK is divided down and used to generate the left/right

and bit clocks for the serial port that is synchronous to MCLK.

The AD1896 supports master modes of 256 ¥ f

S

, 512 ¥ f

S

,

and 768 ¥ f

S

for both input and output serial ports.

Conceptually, the AD1896 interpolates the serial input data by

a rate of 2

20

and samples the interpolated data stream by the

output sample rate. In practice, a 64-tap FIR filter with 2

20

polyphases, a FIFO, a digital servo loop that measures the time

difference between the input and output samples within 5 ps,

and a digital circuit to track the sample rate ratio are used to

perform the interpolation and output sampling. Refer to the

Theory of Operation section. The digital servo loop and sample

rate ratio circuit automatically track the input and output

sample rates.

(Continued on Page 17)

FEATURES

Automatically Senses Sample Frequencies

No Programming Required

Attenuates Sample Clock Jitter

3.3 V–5 V Input and 3.3 V Core Supply Voltages

Accepts 16-/18-/20-/24-Bit Data

Up to 192 kHz Sample Rate

Input/Output Sample Ratios from 7.75:1 to 1:8

Bypass Mode

Multiple AD1896 TDM Daisy-Chain Mode

Multiple AD1896 Matched-Phase Mode

142 dB Signal-to-Noise and Dynamic Range

(A-Weighted, 20 Hz–20 kHz BW)

Up to –133 dB THD + N

Linear Phase FIR Filter

Hardware Controllable Soft Mute

Supports 256 f

S

, 512 f

S

, or 768 f

S

Master

Mode Clock

Flexible 3-Wire Serial Data Port with Left-Justified,

I

2

S, Right-Justified (16-,18-, 20-, 24-Bits), and

TDM Serial Port Modes

Master/Slave Input and Output Modes

28-Lead SSOP Plastic Package

APPLICATIONS

Home Theater Systems, Studio Digital Mixers,

Automotive Audio Systems, DVD, Set-Top Boxes,

Digital Audio Effects Processors, Studio-to-Transmitter

Links, Digital Audio Broadcast Equipment,

DigitalTape Varispeed Applications

*Patents pending.

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜

信息提交成功

信息提交成功