FIR Compiler v7.2

LogiCORE IP Product Guide

Vivado Design Suite

PG149 January 21, 2021

FIR Compiler v7.2 www.xilinx.com 2

PG149 January 21, 2021

Table of Contents

IP Facts

Chapter 1: Overview

Navigating Content by Design Process . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

Filter Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

Feature Summary. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Licensing and Ordering . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Chapter 2: Product Specification

Performance. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Resource Utilization. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Port Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Chapter 3: Designing with the Core

Clocking. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Resets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

AXI4-Stream Considerations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Core Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Input and Output Sample Rate . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

Resource Considerations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

Chapter 4: Design Flow Steps

Customizing and Generating the Core . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

System Generator for DSP. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

Constraining the Core . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

Simulation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

Synthesis and Implementation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

Chapter 5: C Model

Unpacking and Model Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

Installation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

C Model Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

MATLAB Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

Send Feedback

FIR Compiler v7.2 www.xilinx.com 3

PG149 January 21, 2021

Dependent Libraries . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 114

Chapter 6: Test Bench

Demonstration Test Bench . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 115

Simulation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 117

Appendix A: Upgrading

Migrating to the Vivado Design Suite from ISE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 118

Upgrading within the Vivado Design Suite. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126

Appendix B: Debugging

Finding Help on Xilinx.com . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 127

Debug Tools . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 128

Simulation Debug. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 129

AXI4-Stream Interface Debug . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 130

Appendix C: Additional Resources and Legal Notices

Xilinx Resources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 131

Documentation Navigator and Design Hubs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 131

References . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 131

Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 133

Please Read: Important Legal Notices . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 134

Send Feedback

FIR Compiler v7.2 4

PG149 January 21, 2021 www.xilinx.com Product Specification

Introduction

The Xilinx® LogiCORE™ IP FIR Compiler core

provides a common interface to generate

highly parameterizable, area-efficient

high-performance FIR filters.

Features

• AXI4-Stream-compliant interfaces

• High-performance finite impulse response

(FIR), polyphase decimator, polyphase

interpolator, half-band, half-band

decimator and half-band interpolator,

Hilbert transform and interpolated filter

implementations

• Support for up to 256 sets of coefficients,

with 2 to 2048 coefficients per set when

handling more than one set.

• Input data up to 49-bit precision

• Filter coefficients up to 49-bit precision

• Support for up to 1024 interleaved data

channels

• Support for advanced interleaved data

channel sequences

• Support for multiple parallel data channels

with shared control logic

• Interpolation and decimation factors of up

to 64 generally and up to 1024 for single

channel filters

• Support for sample frequency greater than

clock frequency

• Online coefficient reload capability

• User-selectable output rounding

• Efficient multi-column structures for all

filter implementations and optimizations

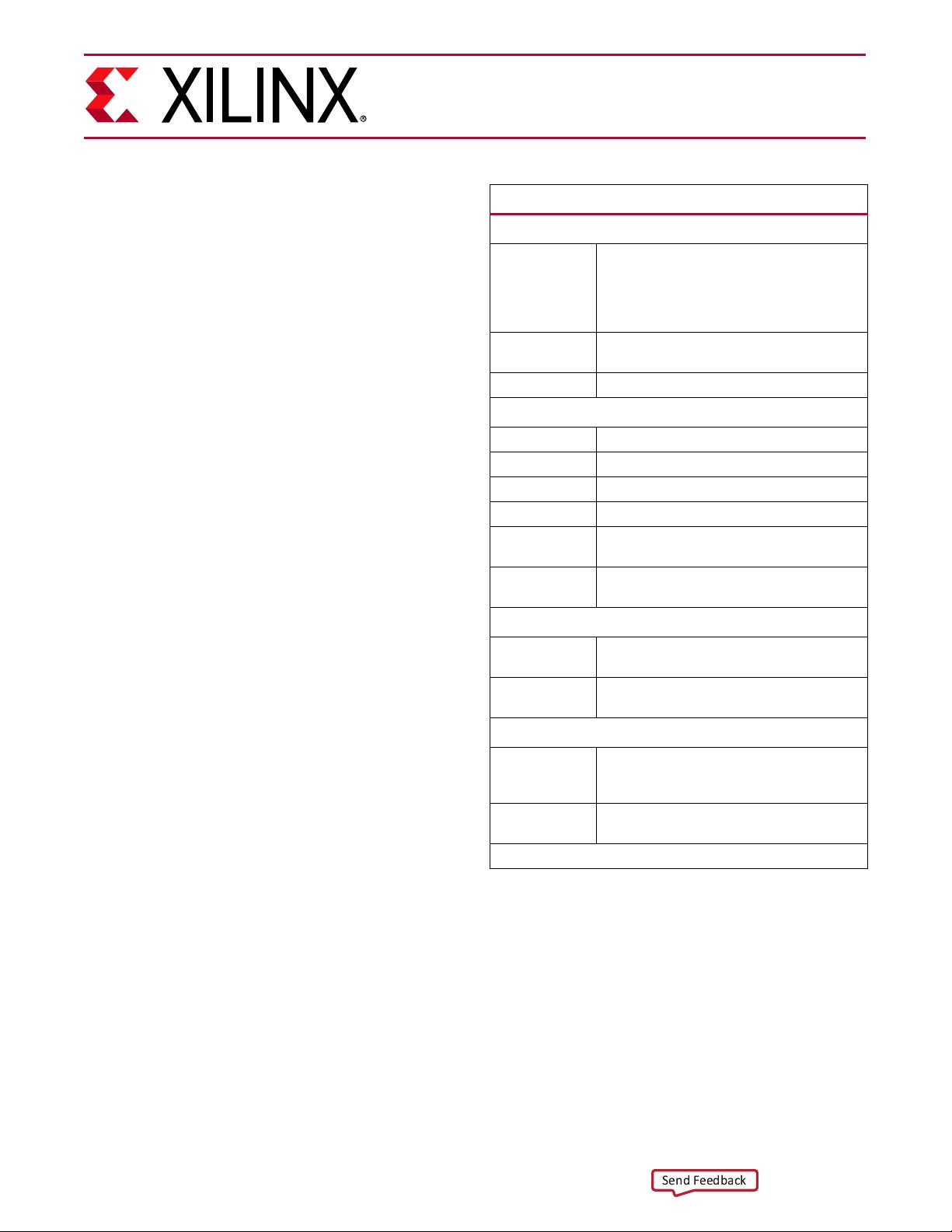

IP Facts

LogiCORE IP Facts Table

Core Specifics

Supported

Device Family

(1)

Versal™ ACAP, UltraScale+™, UltraScale™,

Zynq-7000 SoC

7 Series

Supported User

Interfaces

AXI4-Stream

Resources

Performance and Resource Utilization web

page

Provided with Core

Design Files Encrypted RTL

Example Design Not Provided

Test Bench VHDL

Constraints File Not Provided

Simulation

Model

Encrypted VHDL

Supported

S/W Driver

N/A

Tested Design Flows

(2)

Design Entry

Vivado® Design Suite

System Generator for DSP

Simulation

For supported simulators, see the

Xilinx Design Tools: Release Notes Guide.

Synthesis Vivado Synthesis

Support

Release Notes

and Known

Issues

Master Answer Record: 54502

All Vivado IP

Change Logs

Master Vivado IP Change Logs: 72775

Xilinx Support web page

Notes:

1. For a complete listing of supported devices, see the Vivado IP

catalog.

2. For the supported versions of third-party tools, see the

Xilinx Design Tools: Release Notes Guide.

Send Feedback

FIR Compiler v7.2 5

PG149 January 21, 2021 www.xilinx.com

Chapter 1

Overview

Navigating Content by Design Process

Xilinx documentation is organized around a set of standard design processes to help you

find relevant content for your current development task. This document covers the

following design processes:

• Hardware, IP, and Platform Development: Creating the PL IP blocks for the hardware

platform, creating PL kernels, subsystem functional simulation, and evaluating the

Vivado timing, resource and power closure. Also involves developing the hardware

platform for system integration. Topics in this document that apply to this design

process include:

°

Port Descriptions in Chapter 2

°

Clocking in Chapter 3

°

Resets in Chapter 3

°

Customizing and Generating the Core in Chapter 4

Filter Types

A wide range of filter types can be implemented in the Vivado® Integrated Design

Environment (IDE): single-rate, polyphase decimators and interpolators and half-band

decimators and interpolators. Structure in the coefficient set is exploited to produce

area-efficient FPGA implementations. Sufficient arithmetic precision is employed in the

internal datapath to avoid the possibility of overflow.

The conventional single-rate FIR version of the core computes the convolution sum defined

in Equation 1-1, where N is the number of filter coefficients.

Equation 1-1

yk() an()xk n–()

n 0=

N 1–

= k 01…,,=

Send Feedback

评论0