没有合适的资源?快使用搜索试试~ 我知道了~

资源推荐

资源详情

资源评论

FPGA DDS IP 核实现

DDS(Direct Digital Synthesizer),即直接数字频率合成器,本文主要介绍如

何调用 Xilinx 的 DDS IP 核生成某一频率的 Sin 和 Cos 信号,以及 LFM 信号。

1. 相关参数的介绍及求解

(1)DDS 输出频率

输出频率

out

f

是系统时钟频率

clk

f

、相位累加器中相位数据位宽

)(n

B

和相位

增量

的函数。

)(

2

n

B

clk

out

f

f

因此,要得到输出频率

out

f

,要求相位增量

为

clk

B

out

f

f

n )(

2

如果要采用时分复用的多个通道,则降低每个通道的有效时钟效率。对于 C

个通道,要求相位增量为

clk

B

out

f

Cf

n )(

2

(2)频率分辨率

频率分辨率

f

是系统时钟频率

clk

f

和相位累加器数据位宽

)(n

B

的函数。

)(

2

n

B

clk

f

f

对于时分复用的多通道,频率分辨率随通道数的增加而提高,对于 C 个通道:

C

f

f

n

B

clk

)(

2

(3)相位增量

相位增量值是无符号的,当相位增量值与相位位宽匹配时,也可以将其看作

有符号数。假设相位增量和相位数据位宽均为 N,如果看成无符号数,范围由 0

到

N

2

表示的是

3600,

的角度范围;如果看成有符号数,则范围变成

)1(

2

N

到

)1(

2

N

,相位表示的是

180180 ,

的角度范围。根据正弦信号的周期性和对称性,

两种表示范围内的信号采样是一致的。相位增量定义了综合其的输出频率。相位

增量是系统时钟频率

clk

f

、输出频率

out

f

和相位数据位宽

)(n

B

的函数。

clk

B

out

f

f

n )(

2

2. 线性调频信号

线性调频信号的时间函数表达式可表示为

]

2

,

2

[)],2(exp[)(

2

0

TT

tKttfjts

其瞬时频率为

]

2

,

2

[,)(

2

1

)(

0

TT

tKtft

dt

d

tf

其中,

T

B

K

,B 为信号调频宽度,T 为信号脉宽。

由此可见,线性调频信号的频率变化为线性关系,在已知调频范围和信号脉

宽的情况下,调频率为 K 为已知确定。从而,根据线性调频公式可以得到信号的

瞬时频率。

用 DDS 实 现 线 性 调 频 的 基 本 思 路 为 : 以

t

为 最 小 时 间 单 位 , 根 据

tKnfKtff

illout

计算出某时刻的瞬时频率,再由

clk

B

out

f

f

n )(

2

得出相位

增量

。将

按照设定的时间单位输入到 DDS IP 核中即可生成线性调频信号。

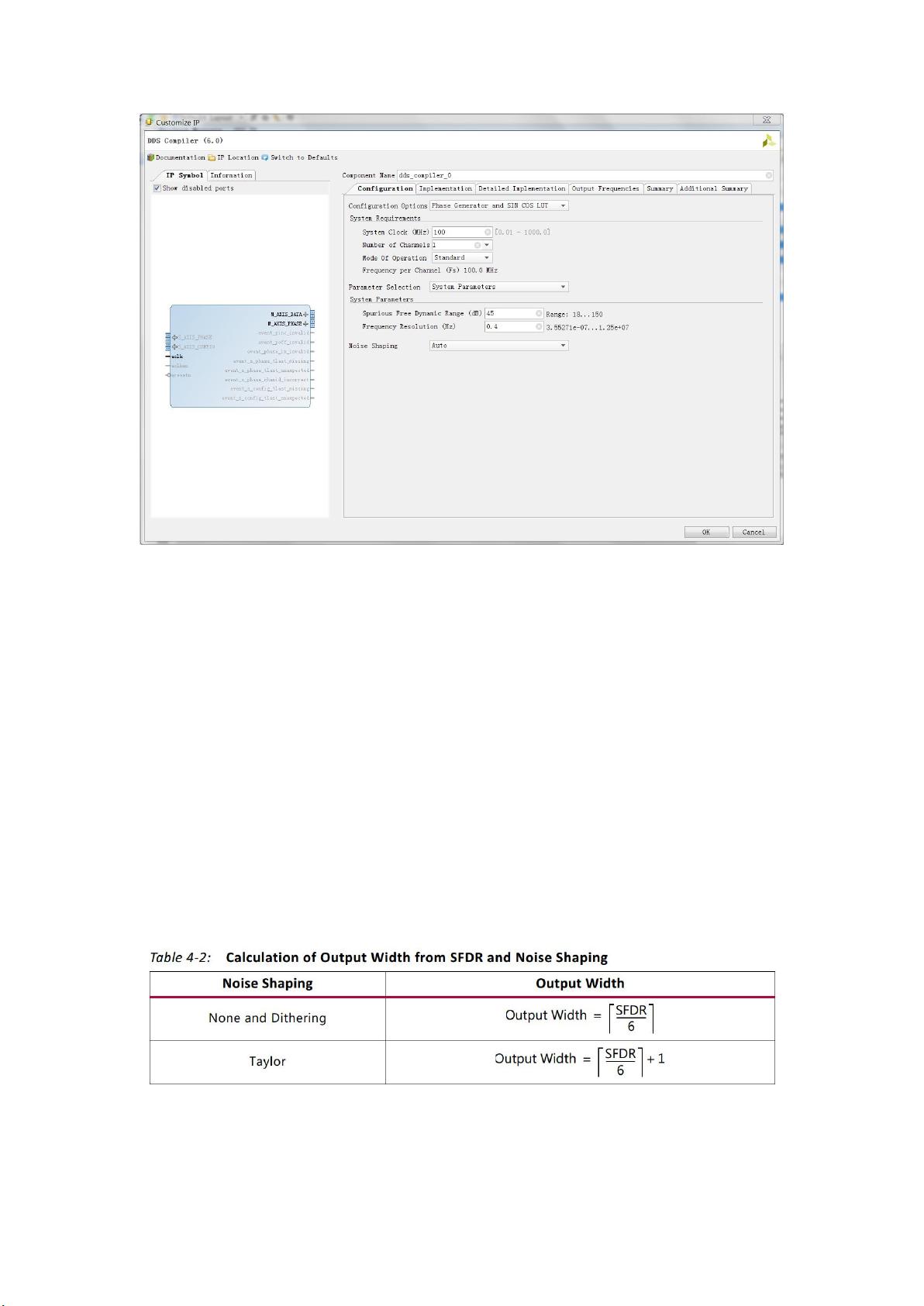

3. FPGA DDS IP 核配置参数介绍

打开 IP Catalog 中的 DDS Compiler,主界面如下图。左边的 Tab 可以切换看

到 DDS 的模块图(管脚信息)等信息,右边的 Tab 是对 DDS 进行设计。在 Component

Name 中输入设计 IP 核的名称。

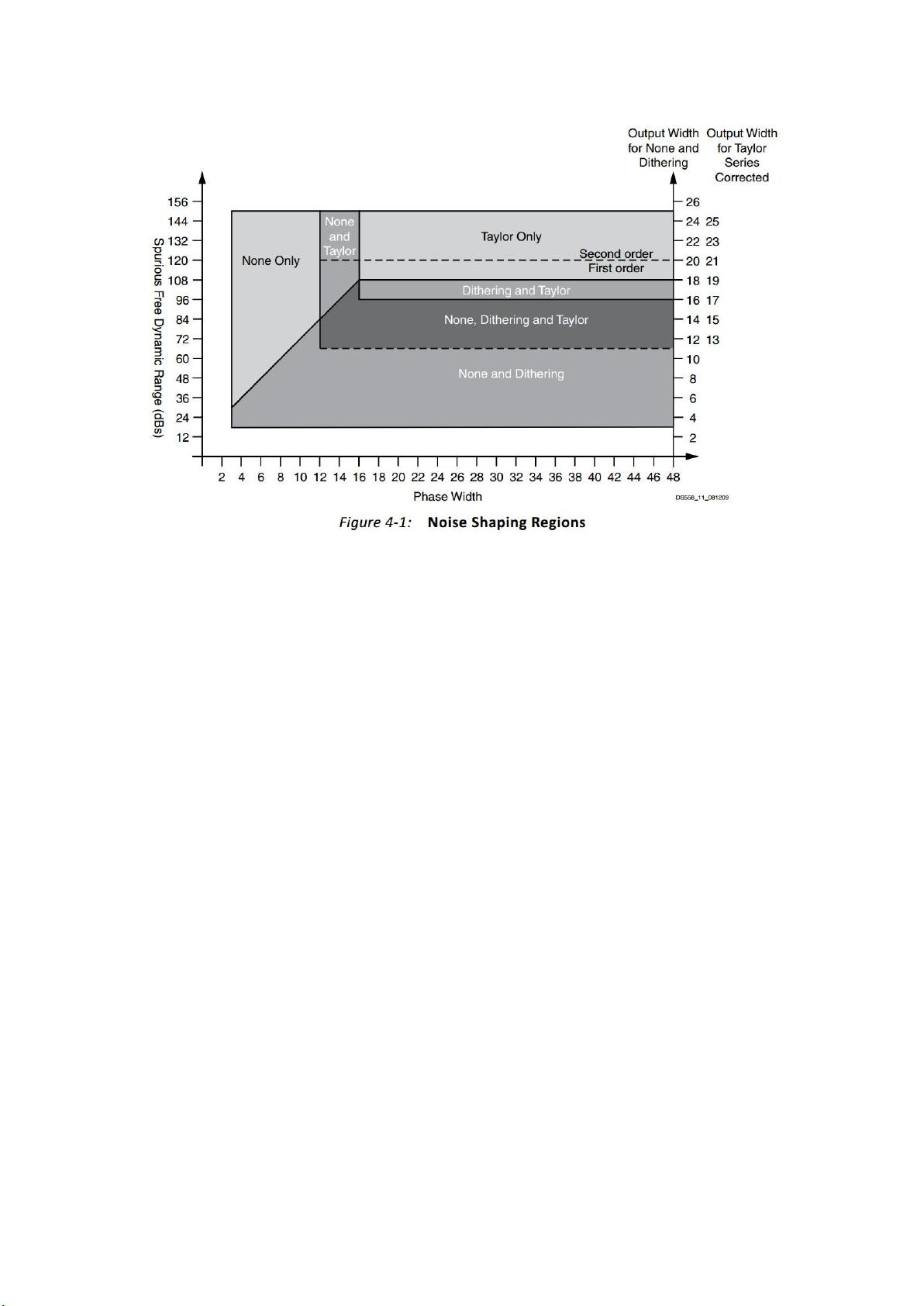

A. Configuration

Configuration 标签下设置配置选项(Configuration Options)、系统时钟(System

Clock)、通道数(Number of Channels)、操作模式(Mode Of Operation)、参数选

择(Parameter Selection)等。其中,Parameter Selection 可以选择系统级参数

( System Parameters ) 或 者 硬 件 级 参 数 ( Hardware Parameters )。 Systerm

Parameters 旨在用于系统架构(频域参数),这种方式可以直接设置无杂散动态

范围(Spurious Free Dynamic Range,SFDR),频率分辨率(Frequency Resolution)、

输出频率(Output Frequencies)等系统级的参数;Hardware Parameters 旨在用

于硬件工程(时域参数),这种方式需要自己设定相位位宽(Phase Width)和输

出数据位宽(Output Width),输出频率、相位偏移等值需要自己计算对应的二

进制数值。

B. Implementation

Impelmentation 标 签 下 可 以 设 置 相 位 增 量 可 编 程 性 ( Phase Increment

Programmability)、相位偏移可编程性(Phase Offset Programmability)、输出信号

形式(Output)和实现选项(Implementation Options)等。

相位增量可编程性和相位偏移可编程性均可选 Fixed、Programmable 或

Streaming。Fixed:相位增量或相位偏移在生成时为固定,不能在运行中更改,

需求的资源最小;Programmable:相位增量或相位偏移在运行中可以是使用

CONFIG 通道进行更改,推荐当 DDS 频率在操作模式之间切换时使用;Streaming:

相位增量或相位偏移由 PHASE 通道输入,推荐当相位增量或者相位偏置值经常

更改或者比如频率调制时使用。此外,相位偏移还可以选择 None,即不产生相

位偏移,节省 FPGA 资源。如果需要生成带有可调初始相位(即相位偏移 Phase

Offset)的信号,可以将“Phase Offset Programmability”设置为“Streaming”,

由 Phase 通道输入,该通道数据总线的有效位宽与设置的频率分辨率(Frequency

Resolution)有关,在 Summary 标签可查看位宽。该数据总线与 360°相位之间

线性对应,比如 Phase Width 为 16Bits,则 0 对应 0°,7FFF 对应 180°,FFFF

对应 360°,以此类推。

剩余19页未读,继续阅读

yunfeishizhe2

- 粉丝: 0

- 资源: 10

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

- 1

- 2

- 3

- 4

- 5

前往页