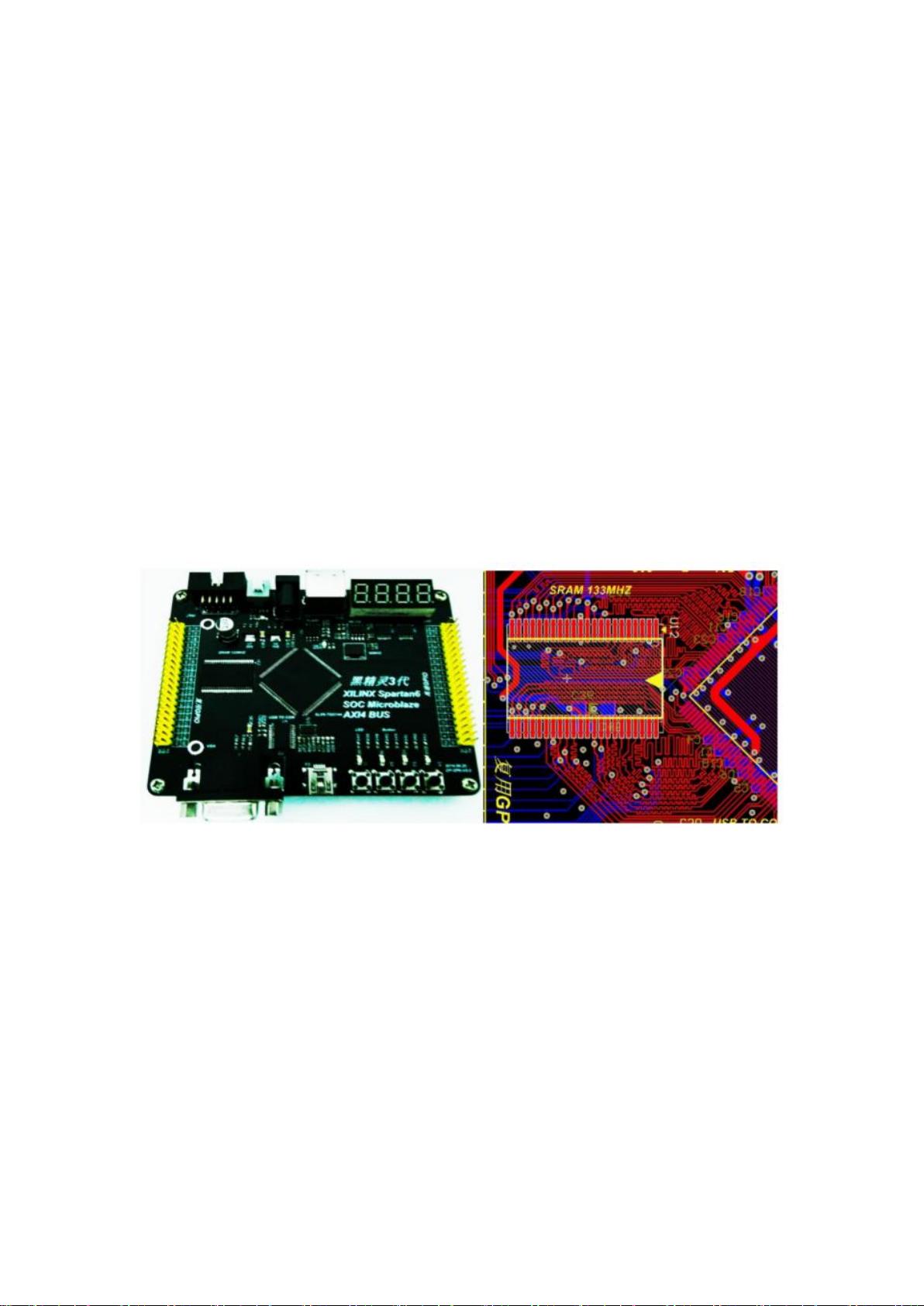

基于FPGA的SRAM、SDRAM、DDR2 内存应用实例,内容包括异步 SRAM-61LV25616 Busrt 读写测试 Verilog、SDR SDRAM 读写测试 Verilog 和DR2 SDRAM 基于 MCB 硬核读写测试 Verilog。每个示例中包括详细的时序分析、仿真示例和代码示例。每个示例的代码均采用Verilog语言编写。简单易懂,适用性强,非常适合刚接触FPGA设计的初学者 ### 基于FPGA的SRAM、SDRAM、DDR2 内存应用实例解析 #### 一、异步 SRAM-61LV25616 Burst 读写测试 Verilog 在介绍异步SRAM的应用实例之前,我们先了解一下SRAM(静态随机存储器)的基本概念和特点。SRAM是一种具有高速读写能力的内存技术,广泛应用于需要快速访问数据的场合。在本例中使用的SRAM型号为61LV25616,它是一种异步SRAM,其特点是无需外部时钟信号就能工作。 **1.1 硬件选型与设计** 本案例选择了Xilinx Spartan6系列的FPGA芯片,具体型号为XC6SLX9-TQG144。由于该芯片无法直接支持DDR/DDR2/DDR3等高速动态内存,故采用了SRAM作为替代方案。为了满足高速数据传输的需求,FPGA与SRAM之间的数据线进行了等长设计,确保信号完整性,以支持高达100MHz的数据通信速率。 **1.2 代码实现** 下面通过一个具体的Verilog代码示例来展示如何实现对61LV25616 SRAM的读写操作: ```verilog module Sram #(parameter BUSRT_LEN = 256)( input Clk, input Rst_n, // SRAM 读写控制模块接口 input [17:0] sram_addr_wr, input [17:0] sram_addr_rd, input [15:0] sram_wr_data, output [15:0] sram_rd_data, input sram_wr_req, input sram_rd_req, output sram_wr_ack, output sram_rd_ack, // SRAM 信号接口 output reg sram_we, output reg sram_ce, output reg sram_oe, output reg sram_ub, output reg sram_lb, output reg [17:0] sram_addr, inout [15:0]sram_data); // 定义状态机状态 parameter IDLE = 6'd0; parameter WRITE = 6'd1; parameter WAIT = 6'd2; parameter READ = 6'd3; parameter READ_D = 6'd4; reg [5:0]state; // 读写地址逻辑 always @(posedge Clk) begin if (~Rst_n) sram_addr <= 18'd0; else if (state == WAIT || state == WRITE) sram_addr <= sram_addr_wr; else if (state == READ || state == IDLE || state == READ_D) sram_addr <= sram_addr_rd; end // 控制信号逻辑 always @(*) begin if (state == WAIT) {sram_we, sram_ce, sram_oe, sram_ub, sram_lb} <= 5'b0; else if (state == READ) {sram_we, sram_ce, sram_oe, sram_ub, sram_lb} <= 5'b1_0000; else {sram_we, sram_ce, sram_oe, sram_ub, sram_lb} <= 5'b1_1111; end // 读写状态机 always @(posedge Clk) begin if (~Rst_n) state <= IDLE; else case (state) IDLE: if (sram_wr_req) state <= WRITE; // 写请求 else if (sram_rd_req) state <= READ; // 读请求 WRITE: state <= WAIT; WAIT: if (wr_bust_cnt == 159) state <= IDLE; else state <= WRITE; READ: if (rd_bust_cnt == BUSRT_LEN - 1) state <= IDLE; else state <= READ; endcase end // Burst 计数器逻辑 reg [9:0] wr_bust_cnt; reg [9:0] rd_bust_cnt; always @(posedge Clk) begin if (~Rst_n) wr_bust_cnt <= 8'd0; else if (state == WAIT) wr_bust_cnt <= wr_bust_cnt + 1'b1; else if (state == IDLE) wr_bust_cnt <= 0; end always @(posedge Clk) begin if (~Rst_n) rd_bust_cnt <= 8'd0; else if (state == READ) rd_bust_cnt <= rd_bust_cnt + 1'b1; else if (state == IDLE) rd_bust_cnt <= 0; end // 读写确认信号 assign sram_wr_ack = (state == WAIT); assign sram_rd_ack = (state == READ); endmodule ``` **1.3 时序分析与仿真** 针对上述Verilog代码,可以通过时序分析工具如ModelSim或Xilinx ISE中的ISE Simulator等来进行仿真验证。例如,设置系统时钟频率为50MHz,并观察不同状态下SRAM的读写行为是否符合预期。 #### 二、SDR SDRAM 读写测试 Verilog SDR SDRAM是一种同步动态随机存取存储器,与SRAM相比,它能够提供更大的存储容量和更高的性价比,但需要外部时钟信号进行同步。 **2.1 硬件设计** 对于SDR SDRAM的设计,需要考虑FPGA与SDRAM之间的连接,包括地址线、数据线、控制信号线等,并确保时序正确性。 **2.2 代码实现** 同样地,可以通过Verilog语言来实现对SDR SDRAM的读写操作。具体实现细节可参考SRAM的读写模块,但需要注意的是SDR SDRAM的操作需要与时钟信号同步。 #### 三、DDR2 SDRAM 基于 MCB 硬核读写测试 Verilog DDR2 SDRAM是双倍数据速率的第二代版本,具有更高的带宽和更低的功耗。在FPGA设计中,通常会利用MCB(Memory Controller Block)硬核来简化DDR2 SDRAM的接口设计。 **3.1 MCB硬核简介** MCB硬核是由FPGA厂商提供的用于管理DDR2 SDRAM的专用硬件模块,可以大大简化设计过程并提高系统性能。 **3.2 硬件设计** 在硬件设计阶段,除了常规的地址线、数据线和控制信号线之外,还需要考虑到电源和接地、时钟信号和命令/地址复用等问题。 **3.3 代码实现** 通过Verilog语言实现对DDR2 SDRAM的读写操作时,需要调用MCB硬核提供的接口,并遵循相应的时序要求。 以上就是关于基于FPGA的SRAM、SDRAM、DDR2 内存应用实例的详细介绍。这些实例不仅提供了具体的代码实现,还涉及了硬件设计和时序分析等方面的知识点,非常适合FPGA设计初学者学习和实践。

剩余46页未读,继续阅读

- 粉丝: 4636

- 资源: 754

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- Qt5.12.6源码 qt-everywhere-src-5.12.6.tar.xz

- 基于jsp的ktv智能点歌系统数据库的设计与实现 .doc

- 基于java的彩票购买系统的设计与实现毕业设计论文.doc

- JQuery前端汇聚loading

- 还在苦恼 postwoman 没法测试上传文件吗,快来吧,这里可以满足你 postwoman 的基础上添加上传文件功能,新增多文件上传功能

- 基于javaweb的超市货物供应系统论文.doc

- 基于javaweb的大学毕业生就业信息管理系统论文.doc

- 基于javaweb的电影院售票系统.doc

- 苹果叶病害图像分类数据集5类别:健康苹果叶、叶斑病、白粉病、疮痂病、褐斑病(7900张图片).rar

- Python绘制圣诞树算法详解及实现

- 圣诞树代码实现及优化-控制台打印与图形界面应用

- 河水预处理系统ug10全套技术开发资料100%好用.zip

- Python编程中绘制圣诞树代码详解与优化

- 如何应对员工突然离职(行政人事系统培训).ppt

- 基于javaweb的房屋租赁管理系统论文.doc

- 【需求调查】-01-培训需求调查问卷.docx

信息提交成功

信息提交成功