DS512 June 22,2011 www.xilinx.com 1

Product Specification

© 2006–2011 Xilinx, Inc. Xilinx, the Xilinx logo, Artix, ISE, Kintex, Spartan, Virtex, Zynq, and other designated brands included herein are trademarks of Xilinx in the

United States and other countries. All other trademarks are the property of their respective owners.

Introduction

The Xilinx LogiCORE™ IP Block Memory Generator

(BMG) core is an advanced memory constructor that

generates area and performance-optimized memories

using embedded block RAM resources in Xilinx

FPGAs. Available through the CORE Generator™

software, users can quickly create optimized memories

to leverage the performance and features of block

RAMs in Xilinx FPGAs.

The BMG core supports both Native and AXI4

interfaces.

The Native interface BMG core configurations support

the same standard BMG functions delivered by

previous versions of the Block Memory Generator (up

to and including version 4.3). Port interface names are

identical.

The AXI4 interface configuration of the BMG core is

derived from the Native interface BMG configuration

and adds an industry-standard bus protocol interface

to the core. Two AXI4 interface styles are available:

AXI4 and AXI4-Lite.

For details on the features of each interface, see

Features.

LogiCORE IP Block

Memory Generator v6.2

DS512 June 22,2011 Product Specification

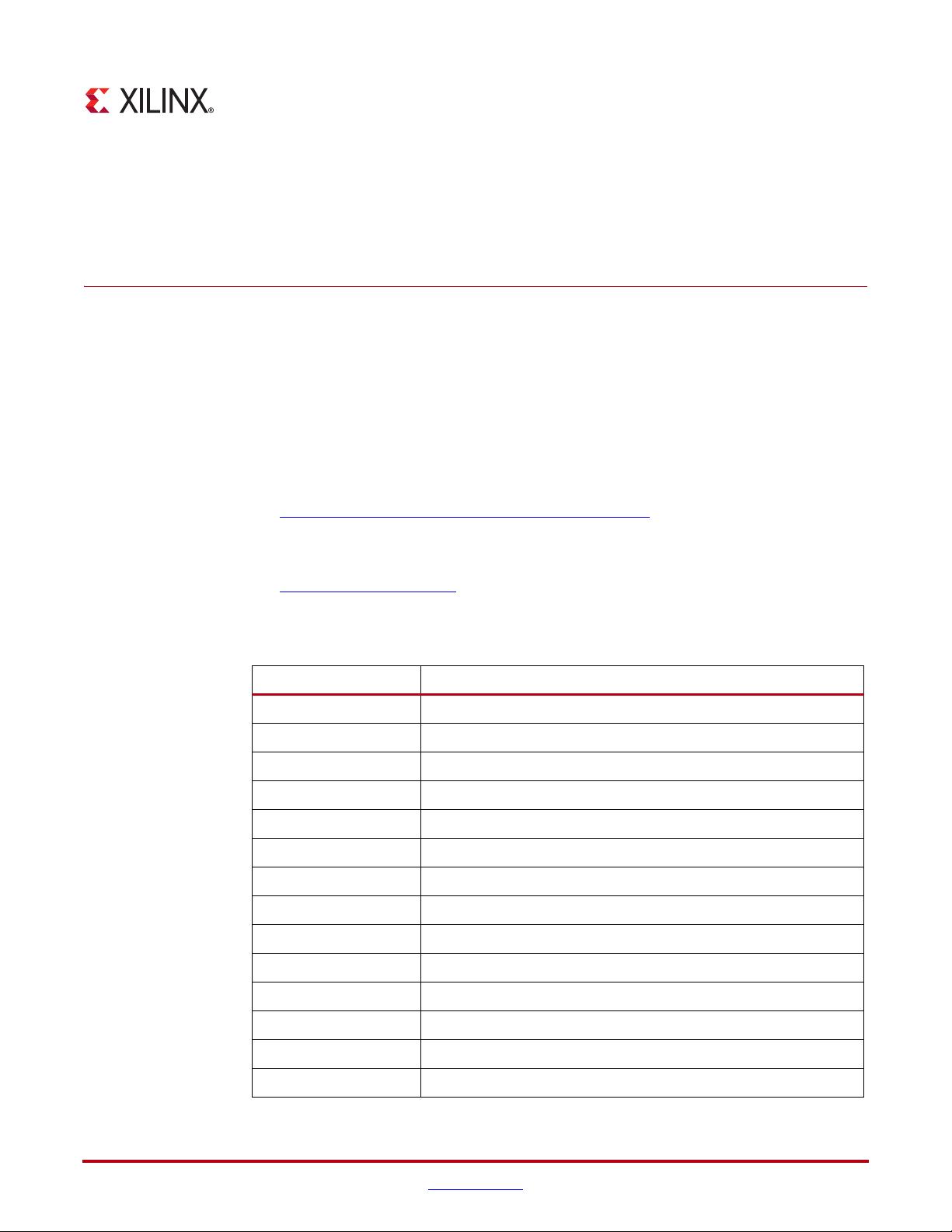

LogiCORE IP Facts

Core Specifics

Supported

Device Family

(1)

1. For the complete list of supported devices, see Table 1, page 3 and

the release notes

for this core.

Zynq-7000, Artix-7, Virtex-7, Kintex-7,

Virtex-6, Virtex-5, Virtex-4, Spartan-6,

Spartan-3E/XA, Spartan-3/XA,

Spartan-3A/3AN/3A DSP

Supported User

Interfaces

AXI4, AXI4-Lite

Block RAM Varied, based on core parameters

DCM None

BUFG None

IOBs/

Transceivers

None

PPC None

IOB-FF/TBUFs None

Provided with Core

Documentation

Product Specification

Migration Guide

(2)

2. The Migration Guide provides instructions for converting designs

that contain instances of either Legacy LogiCORE IP 6.x Single or

Dual Port Block Memory, or older versions of the Block Memory

Generator to the latest version of the Block Memory Generator.

Design File

Formats

NGC Netlist

Design Tool Requirements

Xilinx

Implementation

Tools

ISE v13.2

Simulation

(3)

3. For the supported versions of the tools, see the ISE Design Suite

13: Release Notes Guide.

Mentor Graphics ModelSim

VHDL Structural

Verilog Structural

VHDL Behavioral

(4)

Verilog Behavioral

(4)

4. Behavioral models do not precisely model collision behavior. See

Simulation Models, page 56 for details.

Synthesis XST

Support

Provided by Xilinx, Inc.