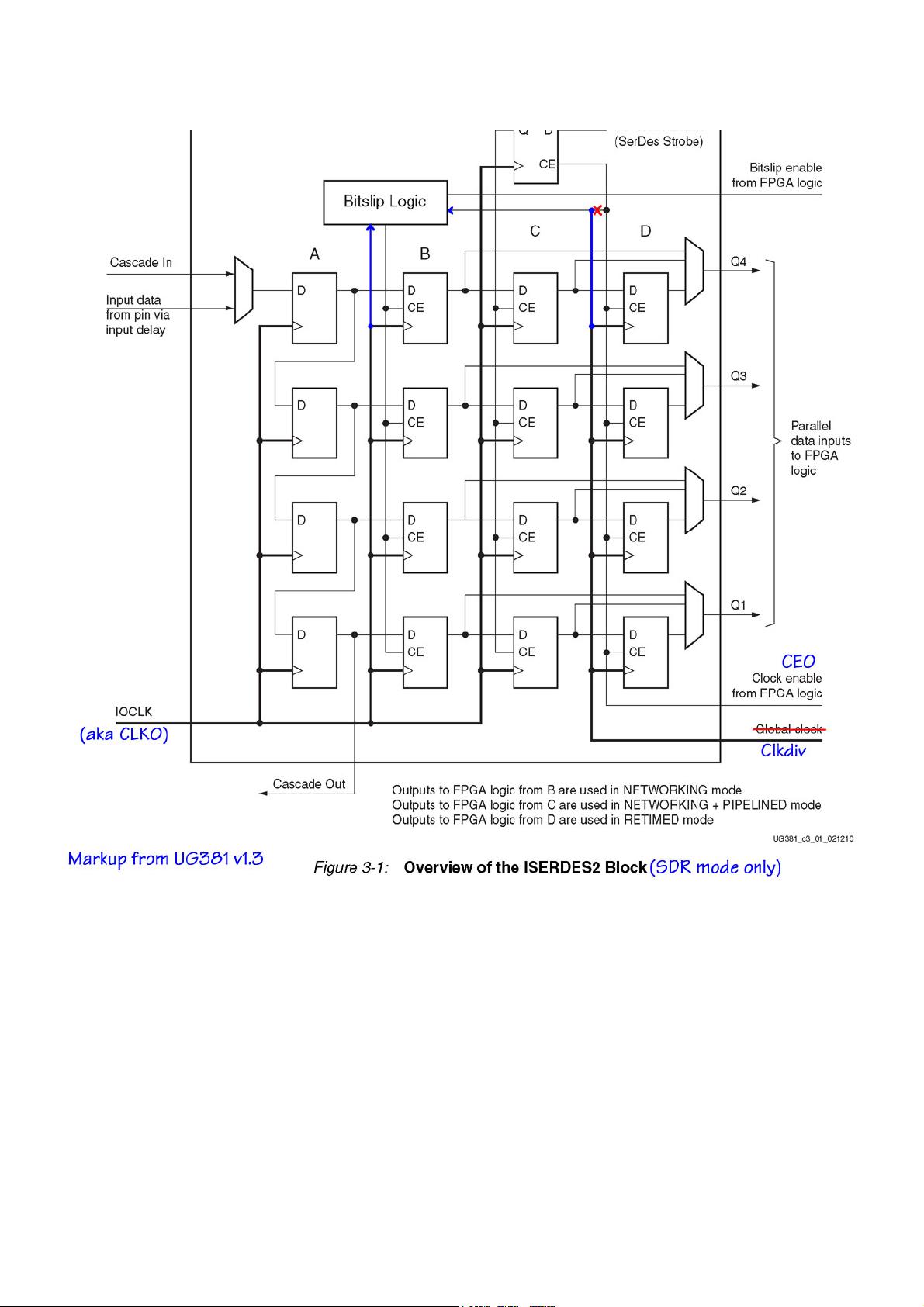

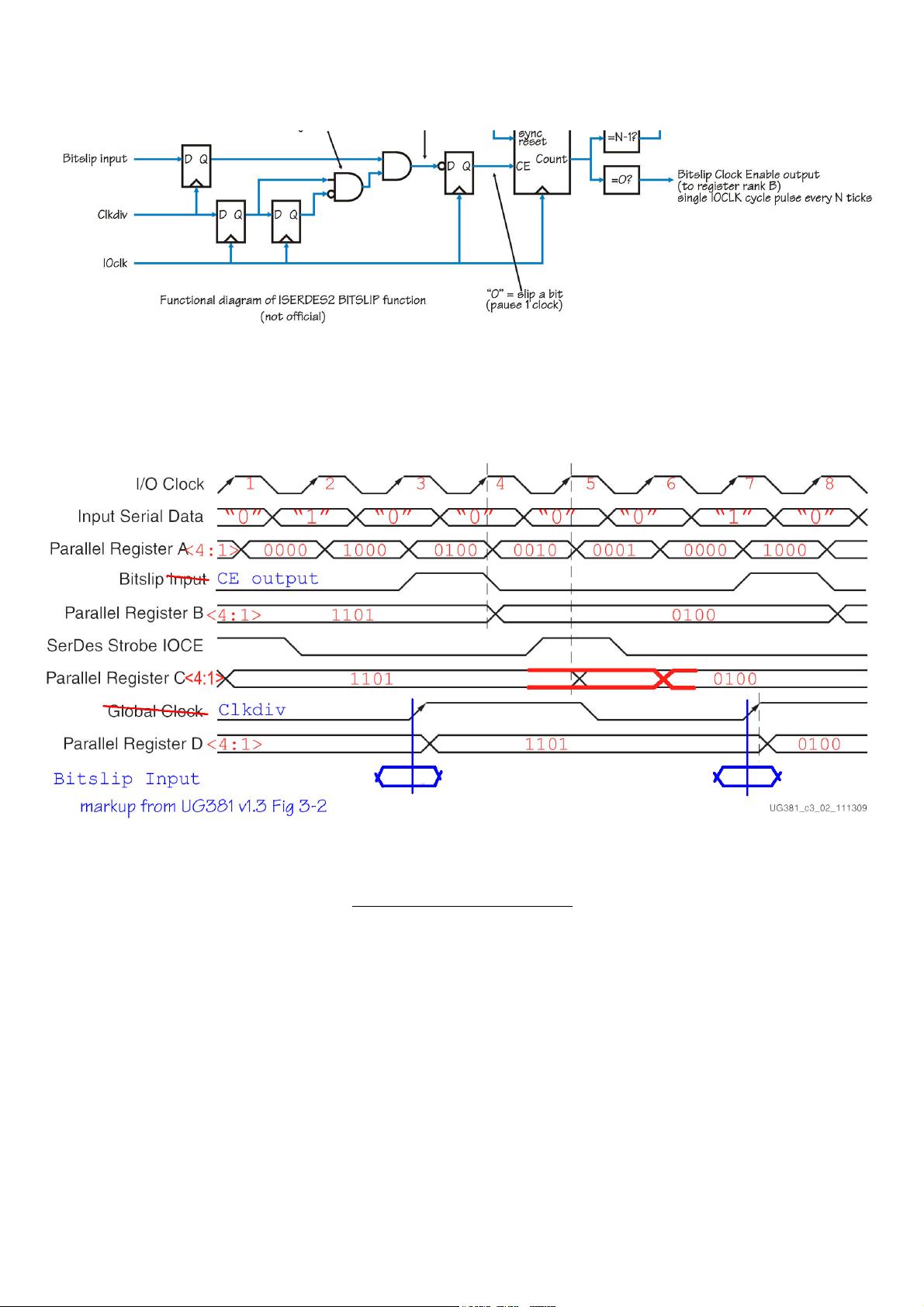

Spartan6 FPGA的serdes模块里有一个BITSLIP功能,用于对齐串行数据,但官方手册里对这个功能介绍很少,大多数人都不知道怎么用。这个文档是国外论坛一个大牛的分析介绍,配合时序图详细介绍了BITSLIP的用法,看完茅塞顿开!! 在Xilinx Spartan6 FPGA系列中,Serdes(Serializer/Demerializer)模块是一个关键的组成部分,它用于高速数据传输。在Serdes中,BITSLIP功能是设计者在处理同步问题时的一个重要工具。BITSLIP功能的主要作用是在接收端调整数据流,确保数据正确对齐,即便在系统时钟不稳定或数据包对齐不准确的情况下也能保持通信的可靠性。 BITSLIP功能的工作原理是通过在接收序列中向前或向后滑动一位数据,以此来补偿时序误差。当检测到数据对齐出现问题时,可以利用BITSLIP控制信号来调整接收的数据位位置,实现数据流的微调。这在系统中有两个主要应用场景: 1. **时钟偏移补偿**:由于实际系统中的时钟源可能存在频率偏差,导致发送和接收端的时钟速度不完全一致。BITSLIP可以补偿这种时钟漂移,确保数据的正确接收。 2. **数据对齐纠正**:在高速通信中,特别是在长距离传输或经过多个接口转换后,数据包可能会出现轻微的位移。BITSLIP能够帮助重新对齐这些数据,避免因位对齐错误导致的解码错误。 理解BITSLIP功能需要结合时序图来分析。在时序图中,你可以看到BITSLIP如何影响数据流的时间关系。例如,如果接收端的时钟比发送端慢,BITSLIP会向后滑动一位数据,相当于为接收端赢得了额外的时间来正确采样数据。相反,如果接收端的时钟快于发送端,BITSLIP则会向前滑动一位数据,以防止过早采样导致的数据丢失。 在使用BITSLIP时,有几个关键点需要注意: - **配置与控制**:BITSLIP通常通过一个控制信号来激活,该信号可以由硬件或者软件控制。在设计中,需要根据系统需求设置合适的BITSLIP触发条件,如基于错误检测或周期性调整。 - **时序分析**:在实现BITSLIP功能时,必须进行详细的时序分析,以确保BITSLIP操作不会引入新的时序违规。这包括检查BITSLIP操作后的采样时刻是否满足接收器的建立和保持时间要求。 - **错误检测与恢复**:BITSLIP通常与错误检测机制(如CRC校验)一起使用,以确定何时需要应用BITSLIP。一旦检测到错误,可以通过BITSLIP调整数据对齐,然后重试传输。 - **系统级影响**:在系统设计中,考虑BITSLIP可能对整个链路的影响,包括上游和下游设备。确保所有组件都能适当地处理BITSLIP信号,并且能够恢复从BITSLIP操作引起的任何临时中断。 BITSLIP是Spartan6 FPGA Serdes模块中一个非常实用的特性,它提高了系统在时序不稳定情况下的鲁棒性。通过深入理解和巧妙应用BITSLIP,设计者可以有效地解决高速通信中的同步问题,确保数据传输的准确性和可靠性。在实际项目中,结合官方文档、社区资源和实践经验,能更好地掌握BITSLIP的使用技巧。

剩余25页未读,继续阅读

- 粉丝: 1

- 资源: 6

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功