实 验 报 告

课 程 名 称 系 统 硬 件 综 合 设 计

专 业 班 级 计算机科学与技术 18-4 班

学 生 学 号

学 生 姓 名

安鑫 李建华 陈田 阙夏 丁贤庆指 导 教 师

一、 课程设计题目

基于 MIPS32 的 5 级流水 CPU 设计

二、 开发环境描述

操作系统:Windows 10 家庭版

开发平台:Modelsim SE 10

开发语言:Verilog

三、 组员信息

四、 课程设计内容

1)

课程设计目的:

⚫

设计一个 MIPS32 五段流水 CPU

⚫

CPU 各主要功能部件的实现 CPU 的封装

⚫

了解提高 CPU 性能的方法

⚫

掌握五段流水线 MIPS32 微处理器的工作原理

⚫

理解并掌握数据冒险、控制冒险的概念以及流水线冲突的解决方法

⚫

掌握流水线 MIPS32 微处理器的测试仿真方法

2)

课程设计要求:

⚫

设计并实现一个多周期和流水 CPU

⚫

可以处理冲突

⚫

三种类型的指令若干条

五、 指令设计

1)

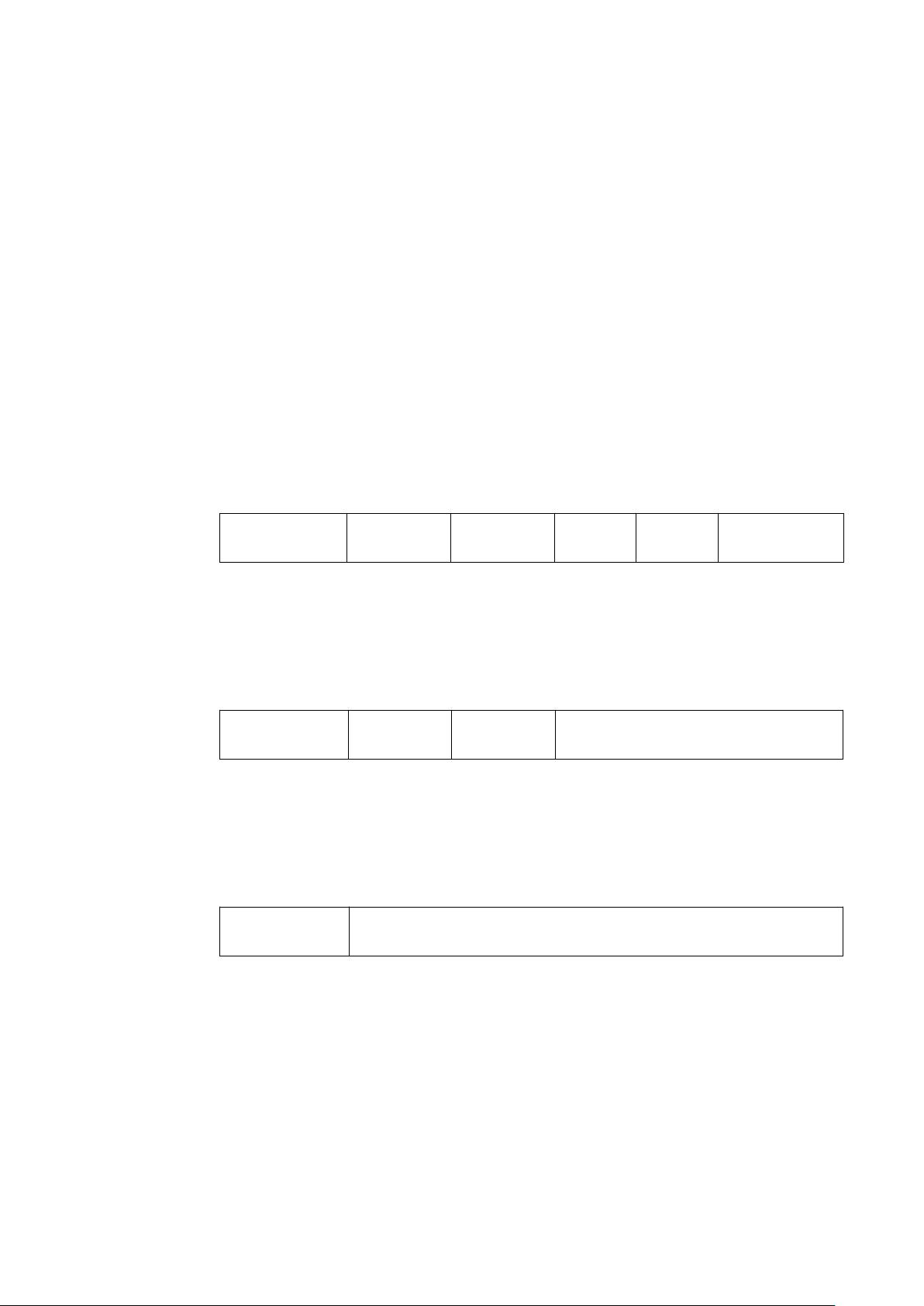

指令格式

MIPS32 架构中的所有指令都是 32 位,并且有三类 32 位指令,分

别为 R 型、I 型、J 型指令,指令格式如下所示:其中 Op 是指令码、

Func 是功能码。具体操作由 Op、Func 结合指定,Rs 和 St 是源寄存

器的编号,Rd 是目的寄存器的编号。

⚫

R 型指令:

具体操作由 Op、Func 结合指定,Rs 和 St 是源寄存器的编号,Rd

是目的寄存器的编号。指令格式如下:

Op(6bit)

Rs(5bit)

Rt(5bit)

Rd 5

Sa 5

Func(6bit)

⚫

I 型指令:

具体操作由 Op 指定,指令的低 16 位是立即数,运算时要将其

扩展至 32 位,然后作为其中一个源操作数参与运算。指令格式如下:

Op(6bit)

Rs(5bit)

Rt(5bit)

Immediate(16bit)

⚫

J 型指令:

具体操作由 op 指定,一般是跳转指令,低 26 位是字地址,用于

产生跳转。指令格式如下:

Op(6bit)

Address(26bit)

图 1 MIPS32 架构中的三种指令

2)

MIPS 指令格式

本次设计实现了 R 型指令、J 型指令、I 型指令共计 14 条,具体指令

表如下所示:

⚫

R 型指令表:

指令

[31:26]

[25:21] [20:16] [15:11] [10:6]

[5:0]

功能

Add 000000 Rs Rt Rd 000000 100000 加法

Sub 000000 Rs Rt Rd 000000 100010 减法

And 000000 Rs Rt Rd 000000 100100 逻辑与

Or 000000 Rs Rt Rd 000000 100101 逻辑或

Xor 000000 Rs Rt Rd 000000 100110 逻辑异或

⚫

I 型指令表:

指令 [31:26] [25:21] [20:16] [15:0] 功能

Addi 001000 Rs Rt Immediate 立即数加

Andi 001100 Rs Rt Immediate 立即数与

Ori 001101 Rs Rt Immediate 立即数或

Lw 100011 Rs Rt Immediate 取数据

Sw 101011 Rs Rt Immediate 存数据

Beq 000100 Rs Rt Immediate 相等转移

Bne 000101 Rs Rt Immediate 不等转移

⚫

J 型指令表:

指令 [31:26] [25:0] 功能

Add 000010 Immediate 产生跳转

六、 总体设计

总体设计部分主要由我们组两人共同完成,分工大致分为:

:取指阶段、译码阶段、暂停控制模块以及封装、测试文件

:执行阶段、访存阶段、回写阶段以及测试完整程序

共同分工:关于数据相关、控制相关的解决

具体设计如下:

1)

MIPS 流水线 CPU 实现原理:

根据 MIPS 微处理器的特点,将整体的处理过程分为取指令(IF)、指

令译码(ID)、指令执行(EX)、存储器访问(MEM)和寄存器写回(WB)

五个阶段,对应着流水线的五级,执行一条指令需要 5 个时钟周期,每个时

钟周期的上升沿到来时,此指令的一系列数据和控制信息将转移到下一级处理。

图 2 五段指令流水执行过程

⚫

IF 级:取指令部分

(1) 根据 PC 值在指令存储器(insMem)中取指令,给出指令地址,将取

得指令放在流水寄存器中,这块由 IF/ID 模块处理。

(2) 对 PC 寄存器的更新,有两种方法,第一种是 PC + 4 ,取下一相

邻地址的 32 位指令;第二种是更新 PC 值为目的跳转地址,该地址来自

于 ID 段算出的分支地址或者跳转地址等。更新的选择取决于来自 ID 段

的一个判断信号,将更新后的 PC 值放在流水线寄存器中,并在下一个

时钟传递到译码阶段。

(3) 涉及模块:PC 模块、IF/ID 模块、insMem 模块

⚫

ID 级:指令译码部分

(1) 进行指令译码,译码结果包括运算类型、运算所需的源操作数、

要写入的目的寄存器地址等等,同时可以进行两个寄存器的读操作和一

个寄存器的写操作。

(2) 关于数据冒险和控制冒险的检测以及处理,采用了暂停机制、数

据前推以及延迟槽,均会在 ID 模块实现并处理解决,同时会将本阶段

译码的结果,在下一个时钟周期传递到执行阶段。

(3) 可以同时进行两个寄存器的读操作和一个寄存器的写操作,对立

即值保存在临时寄存器中,可将指令的低 16 位进行符号位的扩展,并

存放在流水寄存器中。

(4) 涉及模块:ID 模块、Regfiles 模块、ID/EX 模块、stall 模块

- 1

- 2

前往页