电子设计规范.docx

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

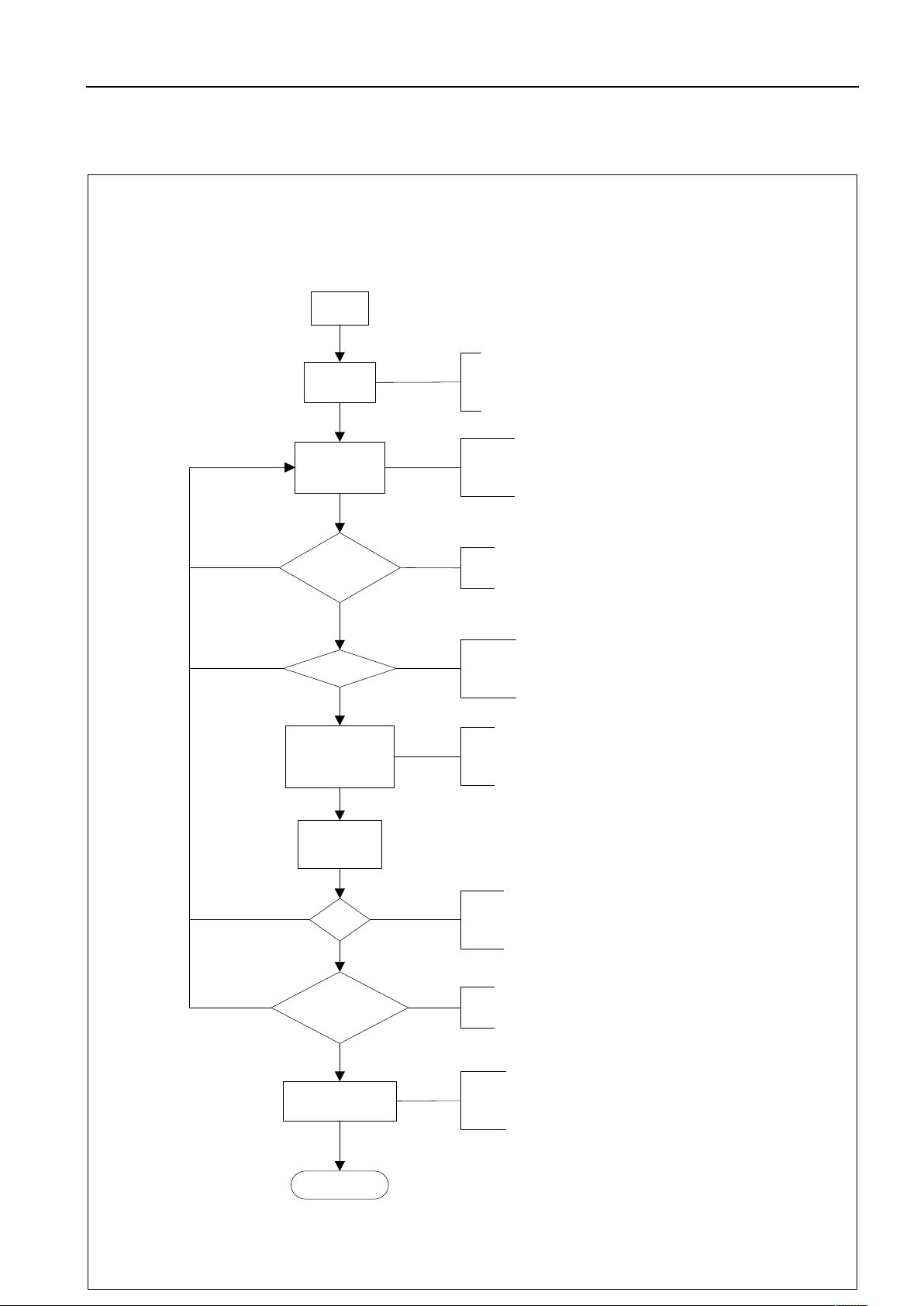

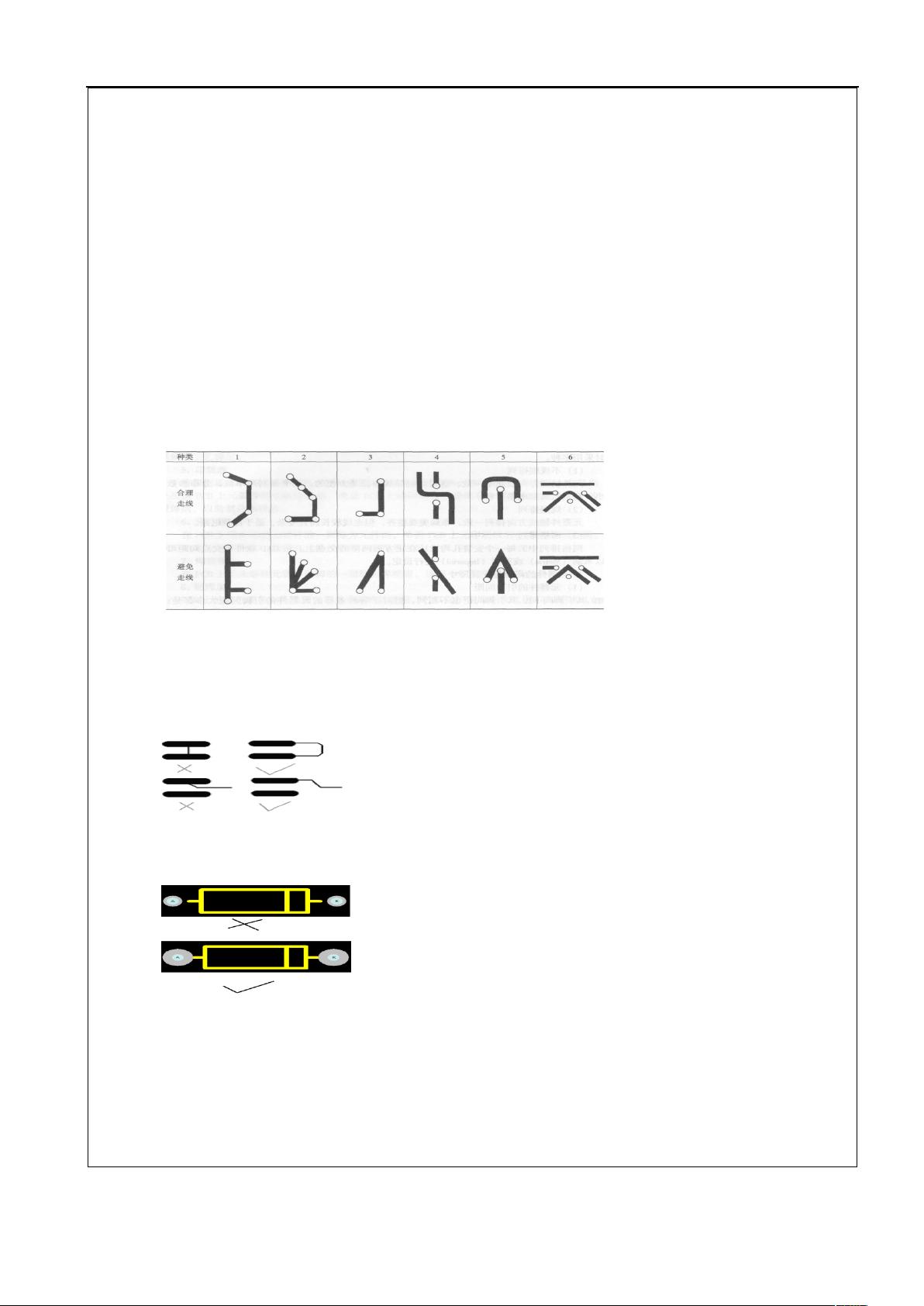

电子设计规范 修订日期 修订内容 版 本 修订者 2018年10月16日 新版拟定 V1.0 高振龙 文件发行类别: 文 件 发 行 印 章 受控文件 非受控文件 极机密 机密 一般 无 保管单位:文管中心 电子设计规范全文共11页,当前为第1页。核 准 电子设计规范全文共11页,当前为第1页。 制 定 一、目 的:制定电子工程师设计工作流程;规范电子图纸设计与发行标准; 二、开发流程:开发流程依据瓴泰科技研发部研发流程中《产品设计开发流程图》而来,提取了电子工程师的研发工作内容,并加以补充说明。 电子设计规范全文共11页,当前为第2页。三、绘图工具:为保持公司文件的易交流、易管理、一致性,避免出现兼容性等问 ,约定电子工程师统一使用Altium Designer软件,未经允许,不得安装或使用其它设计软件,例如Protel/Power PCB/Pads/Orcad等。 电子设计规范全文共11页,当前为第2页。 四、芯片选型: 1、在设计新产品,芯片选型应遵循两个原则: a、查询现有芯片是否可用,此过程可寻求职能工程师帮助,如果有,则不再选用新的芯片; b、选用新的芯片,需确保新元件为市场上常规且易于购买的型号,不得采用冷门芯片。 2、不得在现有库存种类基础上,选用其它品牌或型号的单片机,除非向电子评审团说明原因,并获得通过。 五、PCB设计规范: 1、走线: a、走线应避免锐角、直角,如下图: b、相邻层信号线为正交方向,以减小相互干扰; c、高频信号尽量短; d、输入、输出信号尽量避免相邻平行走线,最好在线间加地线,以防反馈耦合; e、焊盘引线方法: f、插件元件的焊盘,外径尺寸应 内径尺寸2倍,否则可能会导致焊盘易脱落的问题,小的贴片元件,如SOT-23封装,可通过铺铜,加大焊盘,防止焊盘脱落。 2:焊盘和铜箔 SMT焊盘铜箔要求: 电子设计规范全文共11页,当前为第3页。 1.1)SMD 零件两端焊点铺铜需平均分布,以防止墓碑效应(针对锡膏作业) 电子设计规范全文共11页,当前为第3页。 OK NG 1.2)焊盘与印制导线的连接部宽度要相等,保证两端焊盘散热性一致; OK NG MI要求焊盘铜箔要求: 1)相邻焊盘处理(只针对插件焊盘) 不同线路之焊盘间,若相邻焊盘边缘距离 0.8mm时,应加防焊漆隔离,以防连锡或锡薄等,上漆处不可压到吃锡焊盘,如图: 2)相连焊盘处理: 焊盘与焊盘相连尽可能以防焊漆隔开,以防锡薄。 加阻焊漆 加阻焊漆 3)大铜箔处理:(推荐) 面积较宽大之露铜,其铜箔面必需以条形状以防锡薄,焊盘DIP后方有裸露铜箔时,焊盘周边必须加阻焊漆,阻焊漆宽度0.2-0.5mm(一定厚度)。 4)对于晶体管铺铜及焊线,为防止PIN 脚之间连焊,推荐如下处理方式: 如图,增加PIN 脚露铜(按实际过锡方向)PIN 脚前后过锡,将露铜从小到大设置(优先使用),PIN 脚一起过锡则就增加泪滴状。 电子设计规范全文共11页,当前为第4页。 电子设计规范全文共11页,当前为第4页。 5)SMT元件焊盘布局(红胶工艺) SMD零件脚方向与过锡方向垂直(IC和类似M7较高高度高的元件的方向必须遵守,其他元件可参考)。 OK OK 6)拖锡焊盘处理: IC或者连接座(排PIN):最后一个引脚加上一个空的焊盘,或在易短路处相邻引脚上加拖锡焊盘,可避免波峰焊接是短路,如果设计空间足够,最好能再设一个引脚焊盘上加上拖锡焊盘。 如果过炉方向两边均可或采用中心对称拼板方式时,则前后最后四个脚都需加入拖锡焊盘.) 元件轴与过板方向平行时,需要增加偷锡焊盘; 元件轴与过板方向垂直时焊盘需要椭圆处理。 四个脚都加入拖锡焊盘 四个脚都加 入拖锡焊盘 7)PCB铺铜处理: PCB LAYOUT 时遇到面积大于2x2cm 之铺铜时,其铺铜内部需部分开孔/网格铺铜。为避免过锡炉时外围温度过低造成焊盘点有空焊或包焊现象。 8)大焊盘尺寸: 焊盘直径超过3.0mm的焊盘应设计为星形或梅花焊盘;焊盘直径 5mm(方形焊盘长边 5mm)时,焊盘周边必须加阻焊漆,阻焊漆宽度0.2-0.5mm。 电子设计规范全文共11页,当前为第5页。 电子设计规范全文共11页,当前为第5页。 9) 排PIN处理 单排的PIN 焊盘间要增加0.5mm宽度阻焊漆,双排PIN间要加菱形0.5mm宽度阻焊漆,以防过波峰焊连锡。 10)大铜箔上元件焊盘: 为了保证透锡良好,在大面积铜箔上的元件的焊盘要求用隔热带与焊盘相连; 通用要求: 对于有散热要求的焊盘,可采用焊盘包裹的方式进行铺铜,否则应采用十字花焊盘的方式,以便元件焊接; 单片机电路必须进行铺地,单片机所在层需铺地,如果是双面板,背面也需要铺地,并且要打过孔,保证两个地之间最短路径连接。 3、元件封装: a、PCB设计完成后, 【电子设计规范】 电子设计规范是一份详细指导电子工程师进行设计工作的文档,旨在标准化设计流程、选择合适的元器件以及优化PCB(印制电路板)设计,以提高产品质量和生产效率。以下是对这份规范的详细解读: **一、设计目的** 规范的目的是设定电子工程师的设计流程,统一电子图纸设计与发行标准,确保设计的一致性和可维护性。 **二、开发流程** 开发流程参照瓴泰科技研发部的《产品设计开发流程图》,涵盖了从需求明确到产品完成的全过程。设计前需要查阅相关设计目标和技术协议,设计完成后需经过内部评审,最终形成完整的设计文档。 **三、绘图工具** 所有电子工程师必须使用Altium Designer软件进行设计,禁止使用其他如Protel、Power PCB、Pads、Orcad等软件,以确保设计文件的兼容性和管理便利性。 **四、芯片选型** 1. 新产品设计时,首选现有芯片,如有必要选用新芯片,需确保其在市场上常见且易采购,避免使用冷门芯片。 2. 单片机选型不得随意变更品牌或型号,如有特殊需求,需先向电子评审团申请并得到批准。 **五、PCB设计规范** 1. **走线设计** - 避免锐角和直角走线,减少信号干扰。 - 相邻层信号线保持正交,降低串扰。 - 高频信号要尽量短,以减小辐射。 - 输入、输出信号避免平行,加地线防止耦合。 - 插件元件焊盘外径至少是内径的2倍,小贴片元件可以通过铺铜加大焊盘。 2. **焊盘和铜箔** - SMD焊盘铜箔要求两端均匀铺铜,防止墓碑效应。 - 焊盘与导线连接宽度一致,保证散热均匀。 - 相邻焊盘间距小于0.8mm时,应用防焊漆隔离。 - 大铜箔区域建议使用条形防锡薄处理。 - 晶体管铺铜和焊线处理,防止PIN脚连焊,可使用PIN脚露铜和泪滴状设计。 - SMT元件焊盘布局,SMD脚方向与过锡方向垂直,避免连锡。 - 拖锡焊盘处理,防止短路,如IC或连接器的拖锡焊盘设计。 - PCB铺铜处理,大面积铺铜内部分开孔或网格,以改善焊接效果。 - 大焊盘尺寸设计,大于3.0mm的焊盘设计为星形或梅花形,大于5mm的焊盘周围加防焊漆。 - 排PIN处理,增加阻焊漆隔离,防止波峰焊连锡。 - 大铜箔上元件焊盘,采用隔热带或十字花焊盘,确保透锡良好。 **六、元件封装** 元件封装需在完成PCB设计后进行,确保封装正确无误,便于后续生产。 这份电子设计规范详细规定了从设计工具的选择到具体PCB设计细节,旨在保证设计的质量、兼容性和可制造性,降低潜在问题,提高整体设计效率。在实际操作中,工程师应严格遵守这些规则,以确保设计的一致性和可靠性。

剩余10页未读,继续阅读

陆芙欣2024-05-17资源内容详细,总结地很全面,与描述的内容一致,对我启发很大,学习了。

陆芙欣2024-05-17资源内容详细,总结地很全面,与描述的内容一致,对我启发很大,学习了。 timecatxde2023-05-18资源很实用,对我启发很大,有很好的参考价值,内容详细。

timecatxde2023-05-18资源很实用,对我启发很大,有很好的参考价值,内容详细。 mazhuren2024-08-09资源内容详实,描述详尽,解决了我的问题,受益匪浅,学到了。

mazhuren2024-08-09资源内容详实,描述详尽,解决了我的问题,受益匪浅,学到了。

- 粉丝: 198

- 资源: 3万+

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 海康威视7832N-K2 最新解绑固件

- HDMI射频测试设备sw19可编辑全套技术资料100%好用.zip

- SpringBoot 集成 Elasticsearch 实现增删改查功能的代码示例

- ELEQ非标自动化组装设备sw16全套技术资料100%好用.zip

- 基于python 3 编程实现常用的排序算法,包括:冒泡排序、直接插入排序、直接选择排序、希尔排序、归并排序、快速排序、堆排序

- 基于javascript实现插入排序,希尔排序,简单选择排序,冒泡排序,快速排序

- FAT AP, 云AP V200R019C00SPC926 版本说明书(word)

- 一个C语言实现希尔排序

- 达梦8 windows安装包

- 大二篇-离散数学学习笔记

- 钣金压平卷弯机器sw18可编辑全套技术资料100%好用.zip

- VI手机测试设备sw18可编辑全套技术资料100%好用.zip

- IMG_1734484801803.png

- 钣金输送机sw18可编辑全套技术资料100%好用.zip

- mongodb-windows-x86-64-5.0.9-signed windows安装包

- python冒泡排序.md

信息提交成功

信息提交成功