VCS+Verdi联合仿真教程

最近由于在⼀家FPGA公司实习,公司的FPGA仿真和看波形⼯具是VCS+Verdi,由于这两样⼯具结合在⼀起有着极⾼的效率,也因

此真切地感受到,与在学校仅仅使⽤vivado软件跑整个流程相⽐,真的是⼩巫见⼤巫。

因此便在⾃⼰电脑的虚拟机中试着建⽴VCS+Verdi的仿真环境,写下这篇⽂章记录⾃⼰的使⽤过程。

参考⽂章:

⽂章内容主要分两部分:

1. VCS、Verdi介绍

2. Linux下VCS+Verdi仿真demo演⽰

1. VCS、、Verdi介绍介绍

VCS是编译型Verilog模拟器,它完全⽀持OVI标准的Verilog HDL语⾔、PLI和SDF。VCS具有⽬前⾏业中最⾼的模拟性能,其出⾊的内

存管理能⼒⾜以⽀持千万门级的ASIC设计,⽽其模拟精度也完全满⾜深亚微⽶ASIC Sign-Off的要求。 VCS结合了节拍式算法和事件

驱动算法,具有⾼性能、⼤规模和⾼精度的特点,适⽤于从⾏为级、RTL到Sign-Off等各个阶段。VCS已经将CoverMeter中所有的覆盖率

测试功能集成,并提供VeraLite、CycleC等智能验证⽅法。VCS和Scirocco也⽀持混合语⾔仿真。VCS和Scirocco都集成了Virsim图形

⽤户界⾯,它提供了对模拟结果的交互和后处理分析。

Verdi最初是由Novas Softwave公司设计的,后属于了SpringSoft公司,最终SpringSoft被Synopsys公司收购,Verdi正式属于

Synopsys。可以调⽤第三⽅⼯具进⾏编译仿真产⽣波形⽂件并可以查看、可查看源代码对应的电路图,最强⼤之处在于可以在源代码、原

理图、波形图和状态图之间进⾏即时跟踪,协助⼯程师debug。

相信⼤家都⽤过Vivado,Quartus等,这⾥以Vivado为例,他包含了RTL,编译,仿真,综合,看波形,烧板⼦等,集⼤成为⼀体。相⽐

之下,VCS和Verdi就很专⼀了,VCS专注于编译及仿真,Verdi专注于看波形,仅此⽽已,安分守⼰。那Vivado这种功能这么全,⼯业界

直接全⽤⼀个Vivado⾛天下不就⾏了,为何要⼤费周折⽤VCS和Verdi呢?

按我公司⽼板的话来讲,Vivado其实只能算个写Verilog的(⽽且还很慢),只不过集成了综合,仿真,看波形等功能,如果要真正做Asic

设计,还是得在各个步骤⽤上⽤更加专业的软件,⽤那些在领域中做到顶峰的EDA,对,那就是Synopsys的VCS,Verdi这种(毕竟

Vivado的优化⼤多也只针对于⾃家FPGA)。⾸先VCS编译仿真速度极快,效率极⾼,为⼤家节约时间,Verdi看波形也⼗分⽅便debug,

它⽀持信号追溯,⽆缝增加信号波形等功能。虽然上⼿⽐Vivado难,但学习之后能感受到其美丽之处的。

2. Linux下下VCS+Verdi仿真仿真 demo演⽰演⽰

环境:Linux

编写Verilog:gvim

编译仿真:VCS

波形查看:Verdi

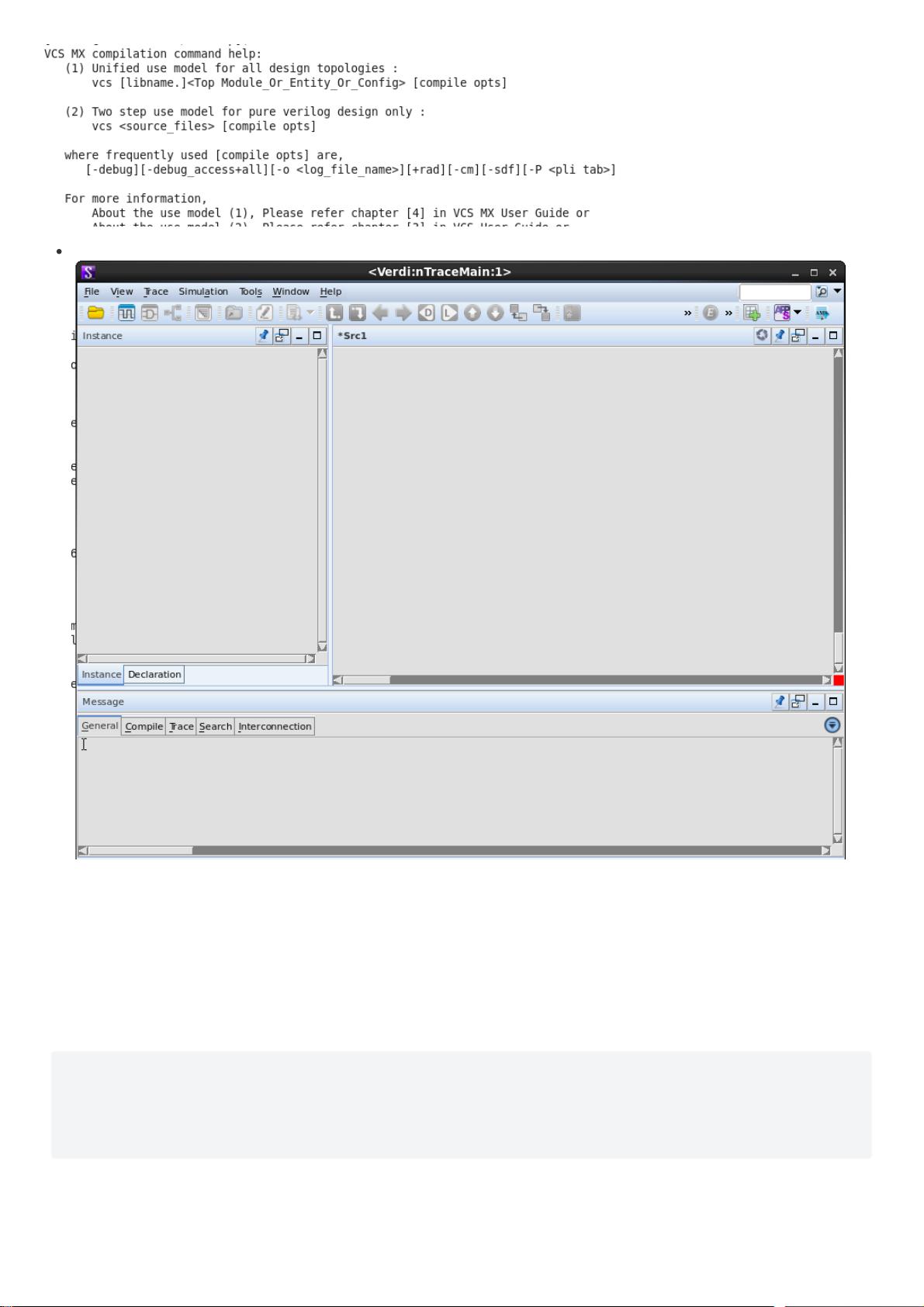

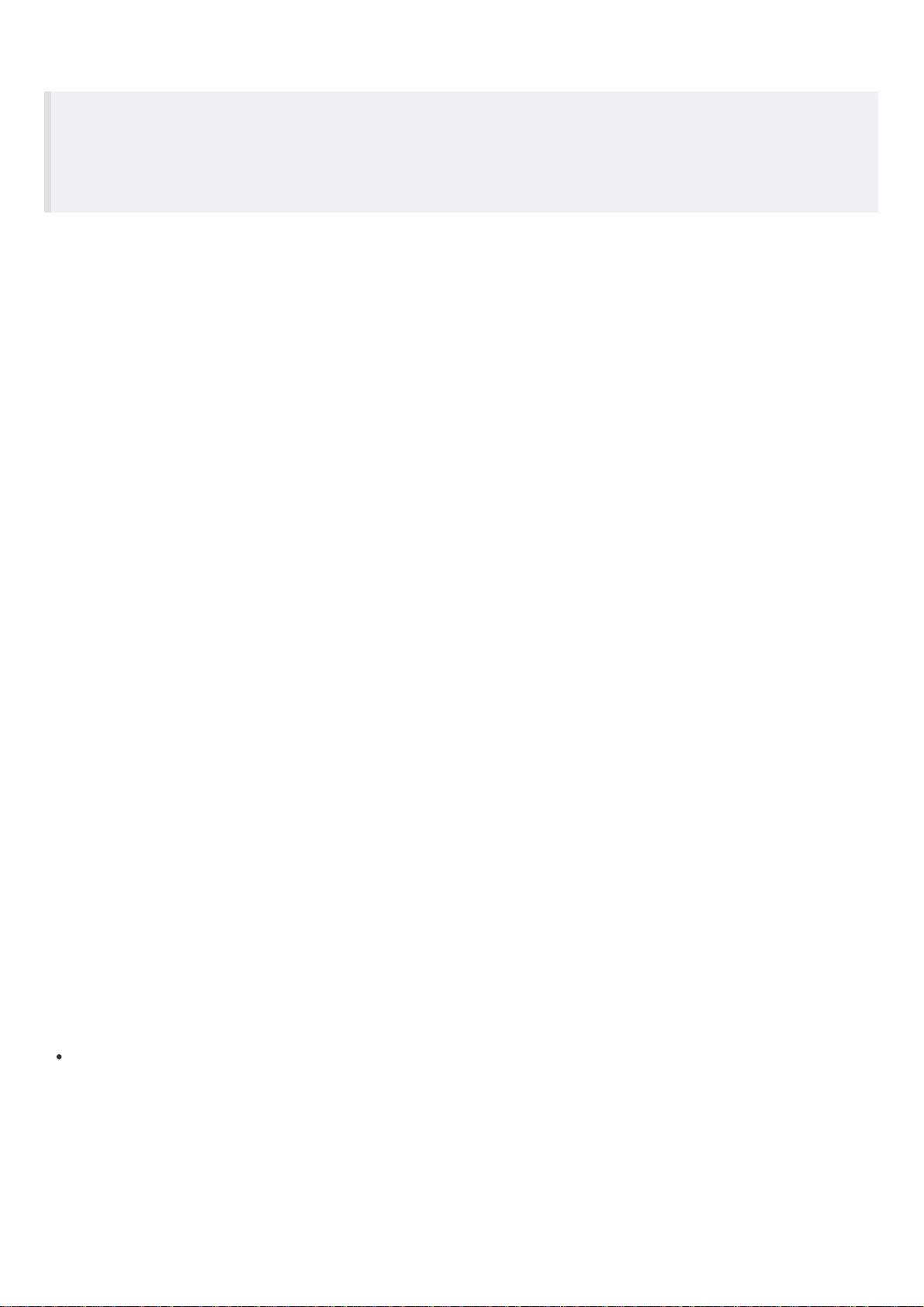

1. ⾸先得在下配置好VCS和Verdi的环境,这个⽅⾯我就不再这⾥赘述了,默认⼤家VCS和Verdi环境都已经配好,你可以在命令⾏输下

vcs和verdi看有没有信息,有信息的话就说明已经安装。

终端输⼊vcs显⽰如下: