VCS利用makefile仿真详细介绍

在电子设计自动化(EDA)领域,Verilog是广泛使用的硬件描述语言之一,而VCS(Verilog Compiler for SystemVerilog)是由Synopsys公司提供的一个强大的Verilog仿真器。本篇将详细介绍如何利用Makefile在VCS环境中进行仿真,以及在`module_tb.v`测试基准中的关键设置。 `VCS`不仅支持Verilog,还支持SystemVerilog扩展,它允许用户进行高层次的验证和复杂的并发行为建模。`Makefile`在软件开发中用于自动化编译过程,同样适用于VCS环境,它可以简化编译、链接和执行仿真的步骤,提高工作效率。 在`module_tb.v`这个测试基准文件中,有三个重要的组成部分: 1. **声明timescale**:`timescale`声明定义了时间和频率单位的精度,例如`timescale 1ns / 1ps`表示时间单位为纳秒,精度为皮秒。这有助于确保仿真结果的精确性和一致性。 2. **初始化信号输入**:测试基准通常会创建并初始化一些激励信号,用于驱动被测模块(DUT,Design Under Test)。这些信号可以是常量、随机数或者通过高级验证库(如UVM)生成的序列。 3. **例化module**:在`module_tb.v`中,你需要实例化被测模块,连接初始化的信号到DUT的输入端,并将DUT的输出连接到观察变量,以便在仿真过程中检查其行为。 4. **波形输出函数$vcdpluson()`**:VCD(Value Change Dump)文件记录了仿真过程中信号的变化,方便后处理分析。`vcdpluson()`函数开启VCD+扩展,它提供了更丰富的信息,如数据类型、层次结构等,便于使用图形工具(如GTKWave)进行波形查看。 5. **仿真时间控制函数$finish()**:`$finish()`在达到特定条件或仿真时间时终止仿真。在测试基准中,通常会在预期的测试结束点或出现错误时调用此函数。 在Makefile中,我们需要定义一些规则来执行VCS编译和仿真任务。常见的字段包括: - `SIM`: 指定仿真器(这里是VCS) - `SOURCES`: 需要编译的所有源文件列表 - `TOP_MODULE`: 被测模块的名称 - `TB_MODULE`: 测试基准模块的名称(通常是`TOP_MODULE_tb`) - `CMD_ARGS`: VCS的命令行参数,如开启优化、设置运行时间等 - `COMPILE_CMD`: 编译源文件的命令 - `SIMULATION_CMD`: 运行仿真的命令 一个简单的Makefile示例可能如下: ```makefile SIM = vcs SOURCES = $(wildcard *.v) TOP_MODULE = my_design TB_MODULE = $(TOP_MODULE)_tb all: compile simulate compile: $(SIM) +vcs+incdir+$(INC_DIR) -o my_sim $(SOURCES) simulate: ./my_sim -l my.log $(CMD_ARGS) -Mdir=waves -vcd +vcdplusmif=my_mif.vpd $(TB_MODULE) clean: rm -rf *.o my_sim simv* csrc* *.log *.vcd my_mif.vpd ``` 在这个Makefile中,`compile`目标用于编译所有Verilog源文件,`simulate`目标则执行仿真,并指定输出日志、波形文件和中间数据文件的位置。`clean`目标用于清理仿真产生的临时文件。 在进行VCS仿真时,我们还需要注意以下几点: - **编译选项**:如`+vcs+incdir+$(INC_DIR)`用于指定包含路径,`-Mdir`指定VCD文件和中间文件的目录。 - **命令行参数**:可以通过`CMD_ARGS`传递其他参数,如`+define+DEBUG`来启用或禁用特定功能。 - **波形视图**:`-vcd`开启VCD输出,`+vcdplusmif`则用于生成VCD+文件,便于使用VCS自带的`dve`工具进行波形查看。 通过VCS和Makefile,我们可以高效地管理和执行Verilog仿真,同时利用`module_tb.v`中的关键元素实现有效的测试和验证。熟练掌握这些技能对于硬件设计和验证工程师来说至关重要。

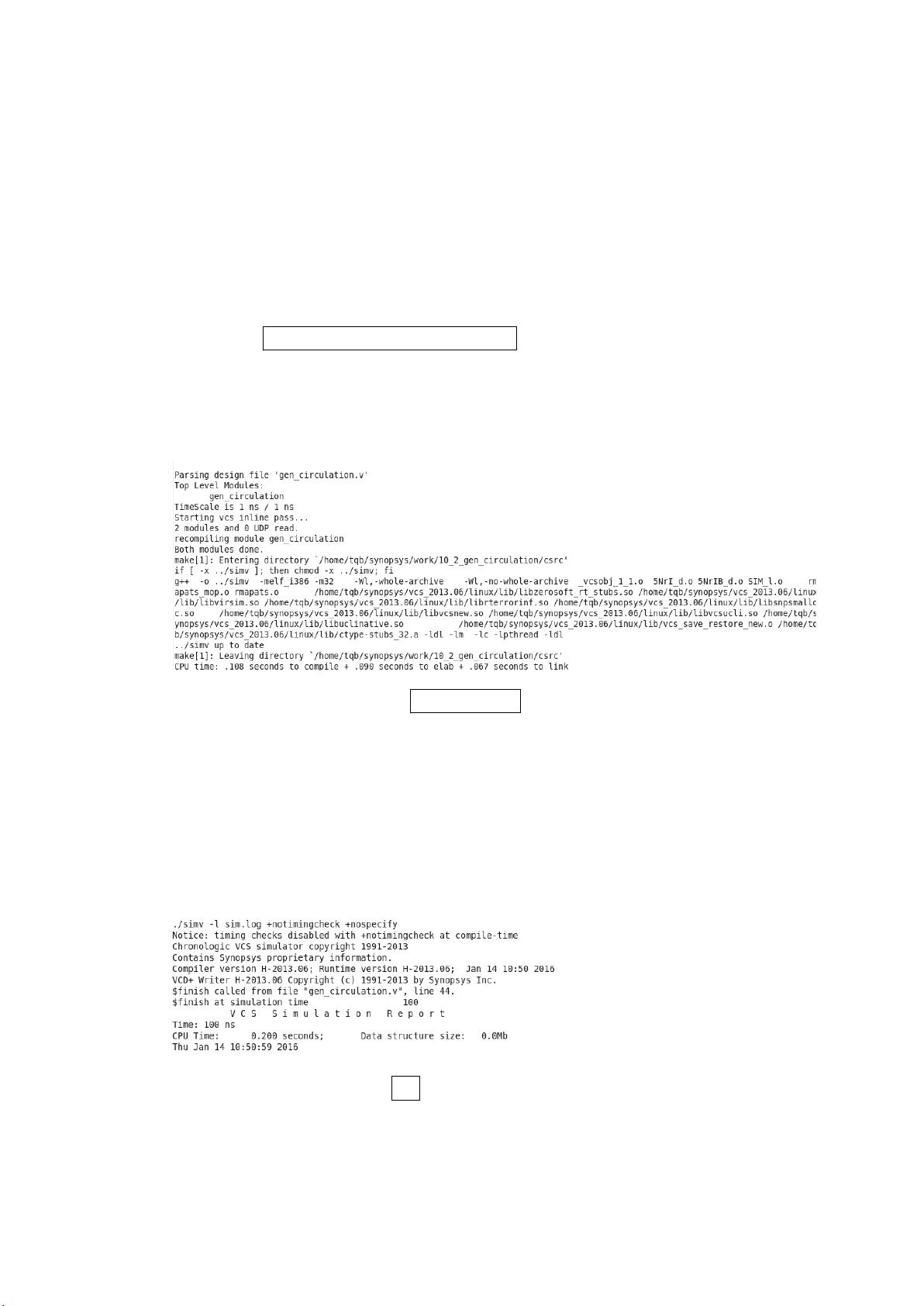

ictown.com_VCS中利用Makefile脚本仿真详细图解(附脚本和源代码).rar (6个子文件)

ictown.com_VCS中利用Makefile脚本仿真详细图解(附脚本和源代码).rar (6个子文件)  ictown.com_VCS中利用Makefile脚本仿真详细图解(附脚本和源代码)

ictown.com_VCS中利用Makefile脚本仿真详细图解(附脚本和源代码)  gen_circulation

gen_circulation  gen_circulation.v 599B

gen_circulation.v 599B Makefile 359B

Makefile 359B VCS中利用Makefile脚本仿真详细图解(附脚本和源代码).docx 359KB

VCS中利用Makefile脚本仿真详细图解(附脚本和源代码).docx 359KB half_adder

half_adder  half_adder_tb.v 707B

half_adder_tb.v 707B half_adder.v 155B

half_adder.v 155B Makefile 359B

Makefile 359B- 1

SeaNico2023-07-27描述准确,对VCS和makefile的原理和应用进行了全面介绍,让读者对其有了更深入的了解。

SeaNico2023-07-27描述准确,对VCS和makefile的原理和应用进行了全面介绍,让读者对其有了更深入的了解。 赵小杏儿2023-07-27该文件详细介绍了VCS如何利用makefile进行仿真,对于初学者来说非常容易理解。

赵小杏儿2023-07-27该文件详细介绍了VCS如何利用makefile进行仿真,对于初学者来说非常容易理解。 独角兽邹教授2023-07-27数据丰富,提供了大量示例代码和实际应用,帮助读者更好地理解和应用VCS。

独角兽邹教授2023-07-27数据丰富,提供了大量示例代码和实际应用,帮助读者更好地理解和应用VCS。 ai2023-07-27作者通过简洁而明确的语言,为读者提供了一份优秀的指南,可以帮助他们更好地运用VCS进行项目管理。

ai2023-07-27作者通过简洁而明确的语言,为读者提供了一份优秀的指南,可以帮助他们更好地运用VCS进行项目管理。 华亿2023-07-27文章结构清晰,逐步引导读者从基础理论到实际操作,非常实用。

华亿2023-07-27文章结构清晰,逐步引导读者从基础理论到实际操作,非常实用。

- 粉丝: 1

- 资源: 4

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 爱依克签批屏KY系列BS架构二次开发包,采用Websocket通信协议,内含驱动服务与开发文档,支持H5页面签名,PDF文件签名、指纹采集捺印以及摄像头拍摄和二代证身份身份信息读取

- Aspera高效文件传输产品技术解析与应用

- STM32DS3231硬件I2C读写,基于HAL库

- double数据做乘法保留两位小数的处理办法.txt

- 详细解读:毕业设计项目及写作技巧全程指南

- 学生成绩管理系统软件界面

- js判断时间多久之前.txt

- Temporal注解的作用.txt

- 五行与商业:古代智慧的探索与传承.docx

- 04747《Java语言程序设计(一)》真题试题 2019 -2021

- 处理苹果手机倒计时功能异常.txt

- HarmonyOS-ArkTS语言-购物商城的实现

- 导出表格报错net.sf.excelutils.ExcelException.txt

- 判断对象不为空的方法参考.txt

- Python爬虫技术入门与实战指南

- C++程序设计 课件PPT

信息提交成功

信息提交成功