没有合适的资源?快使用搜索试试~ 我知道了~

Lab2 FPGA数字钟设计实验_Q17_V2.docx

需积分: 9 0 下载量 115 浏览量

2019-06-13

09:12:09

上传

评论

收藏 1.16MB DOCX 举报

温馨提示

试读

22页

FPGA实验讲义,实验旨为训练使用FPGA开发数字钟设计实验。

资源推荐

资源详情

资源评论

实验 2 多功能数字钟设计与实现

2.1 数字钟的功能要求

设计一个具有时、分、秒计时的数字钟电路,按 24 小时制计时。要求:

(1)准确计时,以数字形式显示时、分、秒的时间;

(2)具有分、时校正功能,校正电路输入脉冲频率为 1Hz;

(3)具有仿广播电台整点报时的功能。即每逢 59 分 51 秒、53 秒、55 秒及 57 秒时,

发出 4 声 500Hz 低音,在 59 分 59 秒时发出一声 1kHz 高音,它们的持续时间均为 1 秒。

最后一声高音结束的时刻恰好为正点时刻。

(4)具有闹钟功能,且最长闹铃时间为 1 分钟。要求可以任意设置闹钟的小时、分

钟;闹铃信号为 500Hz 和 1kHz 的方波信号,两种频率的信号交替输出,且均持续 1 s。

设置一个停止闹铃控制键,可以停止输出闹铃信号。

(5)用 DE2 开发板实现设计。用板上的 50 MHz 晶振源 CLOCK_50 作为时钟,用共

阳极数码管 HEX7、HEX6 显示小时,用 HEX5、HEX4 显示分钟,用 HEX3、HEX2 显示秒

钟。使用拨动开关或者按键作为控制信号输入,外接扬声器及其驱动电路,以便能听到仿

广播电台整点报时的声音或者闹铃声。

2.2 设计过程

数字钟的组成框图如图 2.1.1 所示。

图 2.1.1 数字钟组成框图

数字钟电路的工作原理是:振荡器产生稳定的高频脉冲信号,作为数字钟的时间基准,

再经分频器输出标准秒脉冲(即每秒一个脉冲)。数字钟所有计数器均按照 BCD 码进行计

数。秒计数器对秒脉冲进行计数,从 0 开始计数到 59(模为 60)时,即为 1 分钟,此时,

秒计数器向分计数器进位,分计数器增 1 计数,当分计数器计满 60 后向小时计数器进位,

小时计数器增 1 计数,…,在秒脉冲作用下,计数器不断循环计数,然后将计数器的输出

1 / 22

送译码显示电路,即可显示出一天中的时、分、秒(即时间)。计时出现误差时可以用校

时电路进行小时和分钟的校正。仿电台报时和定时闹钟为扩展电路,在计时主体电路正常

运行的情况下可以进行功能扩展。

数字钟电路实现方法较多,可以用中规模集成电路、ASIC 和 FPGA/CPLD 等方法实现。

对于计时精度要求不高的实验电路,振荡器可以由集成电路定时器 555 与 RC 电路组成

1kHz 的多谐振荡器,然后分频得到 1Hz 的计时秒脉冲。对于计时精度要求高的产品,振

荡器通常由石英晶体构成(例如电子手表的振荡器由频率为 32768Hz 石英晶体构成,将

其进行 2

15

分频,得到 1Hz 的标准计时脉冲)。

在本实验中,将图 2.1.1 中虚线框内部的电路用 Verilog HDL 进行描述,然后用

FPGA 开发板实现。开发板提供的时钟信号由 50MHz 的石英晶体组成。

2.3 数字钟主体电路逻辑设计

这里采用自下向上的设计方法,首先定义数字钟下层的各个模块,再调用这些模块组

合成顶层的数字钟电路。

1. 模 24(小时)计数器设计

小时计数器的计数规律为 00—01—…—09—10—11—…—22—23—00…,即在设计时要求小

时计数器的个位和十位均按 8421 BCD 码计数。

//**********文件名:counter24.v (BCD 计数: 0~23)*************

module counter24 (CntH, CntL, nCR, EN, CP);

input CP, nCR, EN; //计时脉冲 CP、清零信号 nCR 和使能信号 EN

output reg [3:0] CntH, CntL; //小时的十位和个位输出(8421 BCD 码)

always @(posedge CP or negedge nCR)

begin

if(~nCR)

{CntH, CntL} <= 8'h00; //异步清零

else if(~EN)

{CntH, CntL} <= {CntH, CntL}; //保持计数值不变

else if ((CntH>2)||(CntL>9)||((CntH==2)&&(CntL>=3)))

{CntH, CntL} <= 8'h00; //对小时计数器出错的处理

else if ((CntH==2)&&(CntL<3)) //进行 20~23 计数

begin CntH <= CntH; CntL <= CntL + 1'b1; end

else if (CntL==9) //小时十位的计数

begin CntH <= CntH + 1'b1; CntL <= 4'b0000; end

else //小时个位的计数

begin CntH <= CntH; CntL <= CntL + 1'b1; end

end

endmodule

2. 模 60(分钟、秒钟)计数器设计

分和秒计数器的计数规律为 00—01—…—09—10—11—…—58—59—00… ,可见个位计数

器从 0~9 计数,是一个十进制计数器,十位计数器则从 0~5 计数,是一个六进制计数器。

2 / 22

设计时,可以先分别设计一个十进制计数器模块(counter10.v)和一个六进制计数器

(counter6.v),然后将这两个模块组合起来,构成六十进制计数器。其设计的层次结

构如图 2.1.2 所示。

图 2.1.2 六十进制计数器的层次结构

//***** counter10.v ( BCD: 0~9 ) ***

module counter10(Q, nCR, EN, CP);

input CP, nCR, EN;

output [3:0] Q;

reg [3:0] Q;

always @(posedge CP or negedge nCR)

begin

if(~nCR) Q <= 4'b0000; //异步清零

else if(~EN) Q <= Q; //保持计数值不变

else if(Q == 4'b1001) Q <= 4'b0000;

else Q <= Q + 1'b1; //计数器增 1 计数

end

endmodule

//***** counter6.v (BCD: 0~5)******

module counter6(Q, nCR, EN, CP);

input CP, nCR, EN;

output [3:0] Q;

reg [3:0] Q;

always @(posedge CP or negedge nCR)

begin

if(~nCR) Q <= 4'b0000; //异步清零

else if(~EN) Q <= Q; //保持计数值不变

else if(Q == 4'b0101) Q <= 4'b0000;

else Q <= Q + 1'b1; //计数器增 1 计数

end

endmodule

//********ounter60.v (BCD: 00~59)*********

//60 进制计数器:调用 10 进制和 6 进制底层模块构成

module counter60(Cnt, nCR, EN, CP);

input CP, nCR, EN;

output [7:0] Cnt; //模 60 计数器的输出信号,

wire [7:0] Cnt; //输出为 8421 BCD 码

wire ENP; //计数器十位的使能信号(中间变量)

counter10 UC0 (Cnt[3:0], nCR, EN, CP); //计数器的个位

counter6 UC1 (Cnt[7:4], nCR, ENP, CP); //计数器的十位

3 / 22

assign ENP = (Cnt[3:0]==4'h9); //产生计数器十位的使能信号

endmodule

3.数字钟主体电路设计与仿真

数字钟主体电路包括正常计时和对时间进行校正两部分电路,其 Verilog HDL 程序

如 top_clock.v 所示。整个程序分为两个层次三个模块,底层有两个 60 进制计数器模

块(counter60.v)和一个 24 进制计数器模块(counter24.v),这三个模块组成一

个顶层模块(top_clock.v)完成数字钟的主要功能。又由于 60 进制计数器模块由两个

下层模块组成,所以整个程序实际上形成三个层次,其层次结构如图 2.1.3 所示。

正常计时时,秒计数器接收_1Hz 送来的标准秒脉冲信号,每隔 1 秒钟,计数器的值

增 1,当秒计数器计到 59 秒时,产生的输出信号作为分计数器的时钟信号,使分计数器加

1,分、秒计数器同时计到最大值(59 分 59 秒)时,产生的输出信号作为小时计数器的

时钟信号,使小时计数器加 1,从而实现计时功能。对时间进行调整时,使用 AdjHrKey

调整小时,当 AdjHrKey =1 时,将 1Hz 信号直接输入到小时计数器,每秒钟来 1 个时钟

信号,小时计数器加 1 计数,就可以实现对小时的校正。同理,使用 AdjMinKey 可以对

分钟进行校正。

图 2.1.3 数字钟主体电路的程序层次结构图

程序中, MinCP 和 HrCP 分 别 为分 钟计 数器 和小 时计 数器的时 钟 信 号, 将程 序

“assign MinCP = AdjMinKey ? _1Hz : (Second==8'h59);”综合后,会得到一

个 2 选 1 数据选择器电路。当 AdjMinKey=1 时,选择_1Hz 作为分钟计数器的时钟信号

MinCP , 实 现 分 钟 校 正 ; 当 AdjMinKey=0 时 , 选 择 秒 计 数 器 进 位 信 号

(Second==8'h59)作为分钟计数器的时钟信号 MinCP,实现分钟正常计时。小时计数器

时钟信号 HrCP 的选择原理类似。

// ******** top_clock.v *********

module top_clock (Hour, Minute, Second, _1Hz, nCR, AdjMinKey, AdjHrKey);

input _1Hz, nCR, AdjMinKey, AdjHrKey; //输入端口

output [7:0] Hour, Minute, Second; //输出端口

supply1 Vdd; //声明 Vdd 为高电平

wire MinCP, HrCP; //分别为分钟、小时计数器时钟信号(中间变量)

//============= Hour:Minute:Second counter =============

counter60 UT1(Second, nCR, Vdd, _1Hz); //秒计数器

counter60 UT2 (Minute, nCR, Vdd, ~MinCP); //分计数器

counter24 UT3(Hour[7:4], Hour[3:0], nCR, Vdd, ~HrCP); //小时计数器

//产生分钟计数器时钟。AdjMinKey=1,校正分钟;AdjMinKey=0,分钟正常计时

assign MinCP = AdjMinKey ? _1Hz : (Second==8'h59);

4 / 22

//产生小时计数器时钟。AdjHrKey =1,校正小时;AdjHrKey =0,小时正常计时

assign HrCP = AdjHrKey ? _1Hz: ({Minute, Second }==16'h5959);

endmodule

将以上所有文件输入到 Quartus II 软件中,将 top_clock.v 文件设为当前工程的

顶层文件,对设计项目进行编译。

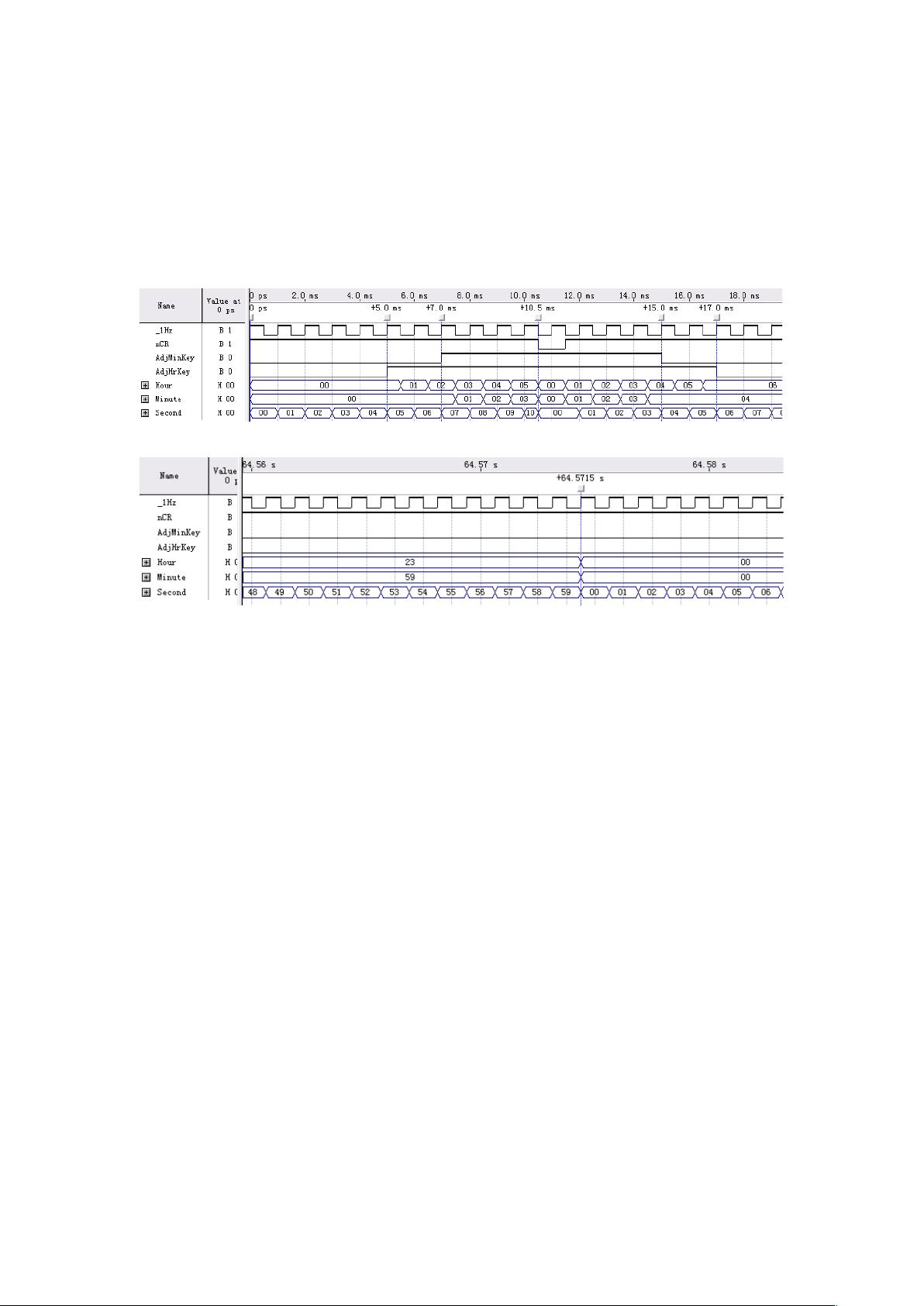

接着,新建一个测试文件,进行功能仿真,得到如图 2.1.4 所示的波形图。分析波形

图得知,仿真结果符合设计要求。

(a)对计时、校时、校分和清零功能的仿真

(b)对计时器进位情况的仿真

图 2.1.4 数字钟主体电路仿真波形图

4.分频模块的设计

(1)输出频率为 1Hz 的分频器设计

该模块的任务是对 50 MHz 的时钟信号进行分频,以产生 1Hz 的秒脉冲输出信号,并

且输出信号的占空比为 50%。

设计一个模数为 25*10

6

的二进制递增计数器,其计数范围是 0~24999999,每当计

数器计到最大值时,输出信号翻转一次,即可产生 1Hz 的秒脉冲,且占空比为 50%。其代

码如下。

//***********文件名:Divider50MHz.v ************

module Divider50MHz(CLK_50M, nCLR, CLK_1HzOut);

parameter N = 25; // 位宽:根据计数器的模来确定

parameter CLK_Freq = 50000000; // 50 MHz 时钟输入

parameter OUT_Freq = 1; // 1 Hz 时钟输出

input nCLR,CLK_50M; //输入端口声明

output reg CLK_1HzOut; //输出端口及变量的数据类型声明

reg [N-1:0] Count_DIV; //内部节点,存放计数器的输出值

always@(posedge CLK_50M or negedge nCLR)

begin

if(!nCLR) begin

CLK_1HzOut <= 0;//输出信号被异步清零

Count_DIV <= 0;//分频器的输出被异步清零

end

5 / 22

剩余21页未读,继续阅读

资源评论

qq_40389306

- 粉丝: 0

- 资源: 1

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 基于C和C++的二维绘制工具设计源码 - DrawPro

- Object.defineProperty 的 IE 补丁object-defineproperty-ie-master.zip

- 整卷预览.mhtml

- MySQL是一种广泛使用的开源关系型数据库管理系统,它提供了丰富的SQL语句用于数据库的创建、查询、更新和管理 以下是一些常见的

- MySQL是一种广泛使用的开源关系型数据库管理系统,它提供了丰富的SQL语句用于数据库的创建、查询、更新和管理 以下是一些常见

- MySQL是一种广泛使用的开源关系型数据库管理系统,它提供了丰富的SQL语句用于数据库的创建、查询、更新和管理 以下是一些常见的

- 基于Javascript的结婚请帖设计源码 - Invitation

- mysql语句大全及用法

- mysql语句大全及用法

- mysql语句大全及用法

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功