AXI DataMover v5.1

LogiCORE IP Product Guide

Vivado Design Suite

PG022 November 18, 2015

AXI DataMover v5.1 www.xilinx.com 2

PG022 November 18, 2015

Table of Contents

IP Facts

Chapter 1: Overview

Feature Summary. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Unsupported Features. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Licensing and Ordering Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Chapter 2: Product Specification

Performance. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Resource Utilization. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Port Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Design Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Chapter 3: Designing with the Core

Clocking. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Resets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Chapter 4: Design Flow Steps

Customizing and Generating the Core . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Constraining the Core . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

Simulation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

Synthesis and Implementation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

Chapter 5: Example Design

Implementing the Example Design. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

Simulating the Example Design. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

Test Bench for the Example Design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

Appendix A: Migrating and Upgrading

Migrating to the Vivado Design Suite. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

Upgrading in the Vivado Design Suite . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

Send Feedback

AXI DataMover v5.1 www.xilinx.com 3

PG022 November 18, 2015

Appendix B: Debugging

Finding Help on Xilinx.com . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

Vivado Design Suite Debug Feature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

Hardware Debug . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

Appendix C: Additional Resources and Legal Notices

Xilinx Resources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

References . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

Please Read: Important Legal Notices . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

Send Feedback

AXI DataMover v5.1 www.xilinx.com 4

PG022 November 18, 2015 Product Specification

Introduction

The Xilinx LogiCORE™ IP AXI DataMover core is

a soft core that provides the basic AXI4 Read to

AXI4-Stream and AXI4-Stream to AXI4 Write

data transport and protocol conversion. The

function is intended to be a standalone core for

custom designs.

Features

• AXI4 Compliant

• Primary AXI4 data width support of 32, 64,

128, 256, 512, and 1,024 bits

• Primary AXI4-Stream data width support of

8, 16, 32, 64, 128, 256, 512 and 1,024 bits

• Parameterized Memory Map Burst Lengths

of 2, 4, 8, 16, 32, 64, 128, and 256 data

beats

• Optional Unaligned Address access;

Up to 64 bit address support.

• Optional General Purpose

Store-And-Forward in both Memory Map to

Stream (MM2S) and Stream to Memory

Map (S2MM)

• Optional Indeterminate Bytes to Transfer

(BTT) mode in S2MM

• Supports synchronous/asynchronous

clocking for Command/Status interface

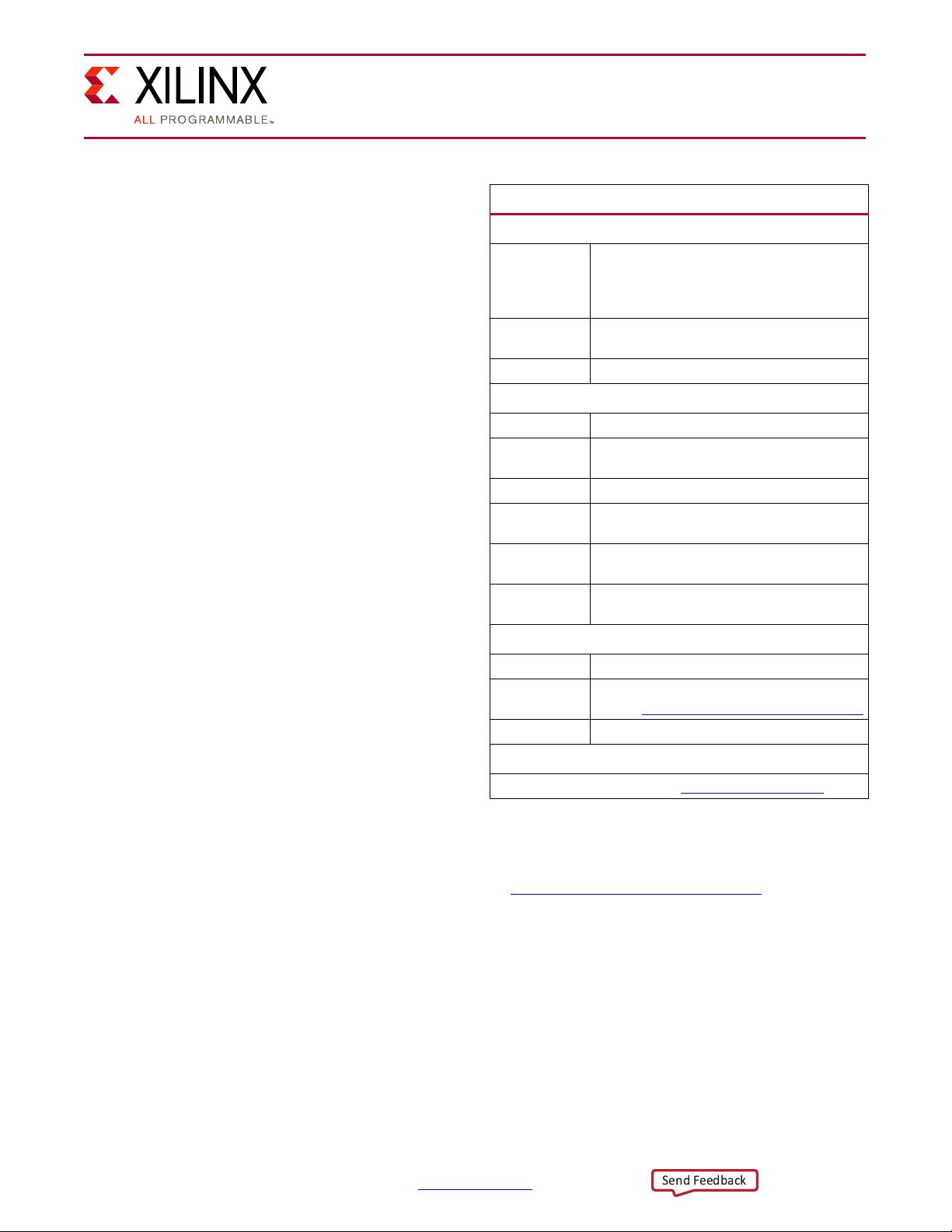

IP Facts

LogiCORE IP Facts Table

Core Specifics

Supported

Device

Family

(1)

UltraScale+™ Families,

UltraScale™ Architecture,

Zynq®-7000 All Programmable SoC,

7 Series FPGAs

Supported

User Interfaces

AXI4, AXI4-Stream

Resources See Table 2-4 and Ta bl e 2- 5.

Provided with Core

Design Files VHDL

Example

Design

VHDL

Tes t Benc h VHDL

Constraints

File

Delivered during IP generation

Simulation

Model

Not Provided

Supported

S/W Driver

N/A

Tested Design Flows

(2)

Design Entry Vivado® Design Suite

Simulation

For supported simulators, see the

Xilinx Design Tools: Release Notes Guide

Synthesis

Support

Provided by Xilinx at the Xilinx Support web page

Notes:

1. For a complete list of supported devices, see the Vivado IP

catalog.

2. For the supported versions of the tools, see the

X

ilinx Design Tools: Release Notes Guide.

Send Feedback

AXI DataMover v5.1 www.xilinx.com 5

PG022 November 18, 2015

Chapter 1

Overview

The AXI DataMover is a key interconnect infrastructure IP that enables high throughput

transfer of data between the AXI4 memory-mapped and AXI4-Stream domains. The AXI

DataMover provides the MM2S and S2MM AXI4-Stream channels that operate

independently in a full-duplex like method. The AXI DataMover IP core is a key building

block with 4 KB address boundary protection, automatic burst partitioning, and provides

the ability to queue multiple transfer requests using nearly the full bandwidth capabilities of

the AXI4-Stream protocol. Furthermore, the AXI DataMover provides byte-level data

realignment allowing memory reads and writes to any byte offset location. Based on the

requirement of the channels, they can be configured as Basic or Full.

Figure 1-1 and Figure 1-2 show block diagrams of the AXI DataMover core. There are two

sub blocks:

• MM2S: This block handles transactions from the AXI4 to the AXI4-Stream domain. It

has its dedicated AXI4-Stream compliant command and status queues, reset block, and

error signals. Based on command inputs, the MM2S block issues a read request on the

AXI4 interface. Read data can be optionally stored inside the MM2S block. Datapath

interfaces (AXI4-Read and AXI4-Stream Master) can optionally be made asynchronous

to command and status interfaces (AXI4-Stream Command and AXI4-Stream Status).

• S2MM: This block handles transactions from the AXI4-Stream to AXI4 domain. It has its

dedicated AXI4-Stream compliant command and status queues, reset block, and error

signals. Based on command inputs and input data from the AXI4-Stream interface, the

S2MM block issues a write request on the AXI4 interface. Input stream data can be

optionally stored inside a S2MM block. Datapath interfaces (AXI4-Read and

AXI4-Stream Master) can optionally be made asynchronous to command and status

interfaces (AXI4-Stream Command and AXI4-Stream Status).

Send Feedback