2 PL 端 AXI Master

AXI4 相对复杂,但 SOC 开发者必须掌握,对于 zynq 的开发者,笔者建议能够在一些

已

有的模板代码基础上修改。AXI 协议的具体内容可参考 Xilinx UG761 AXI Reference

Guide。

在这里我们简单了解一下。

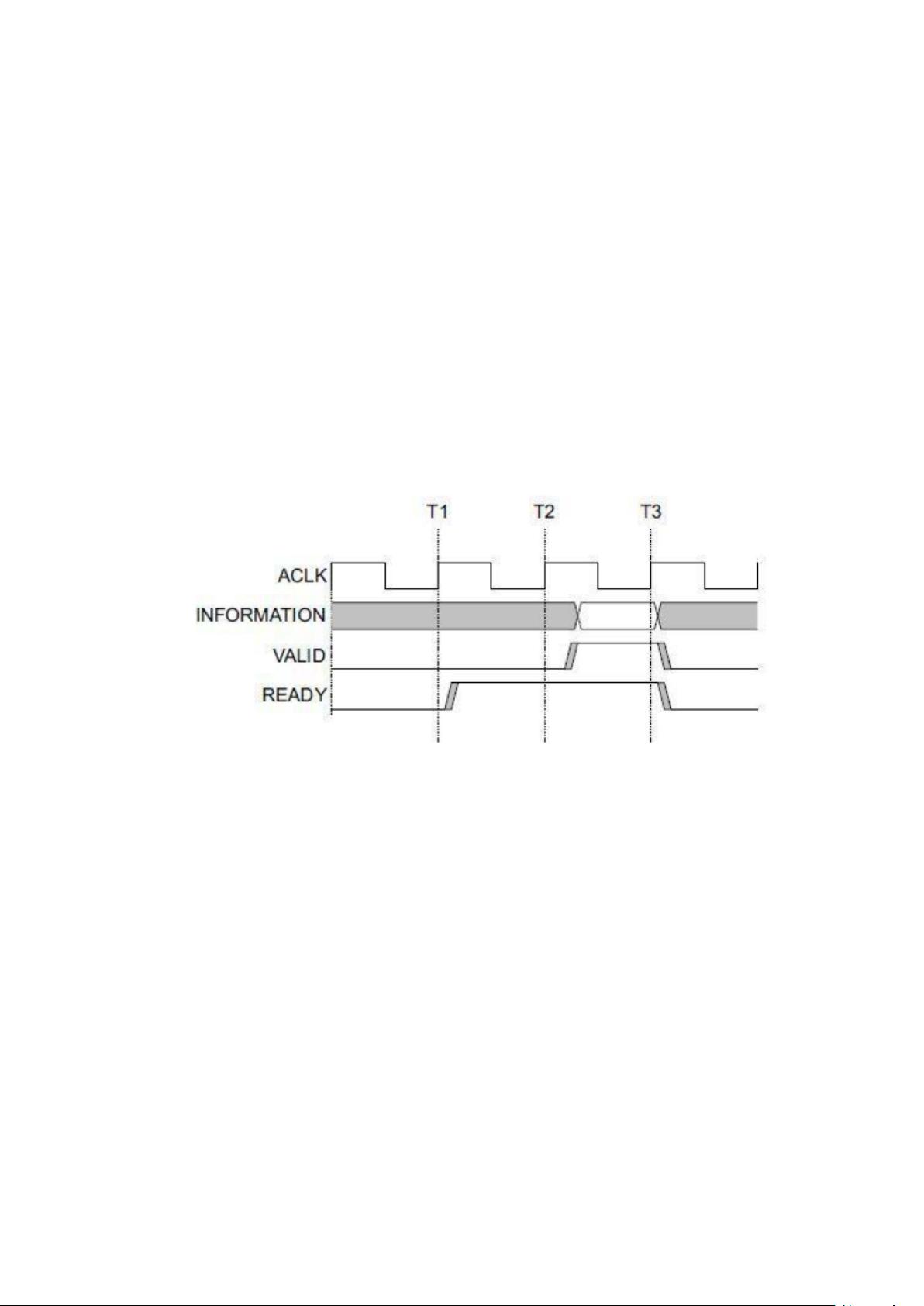

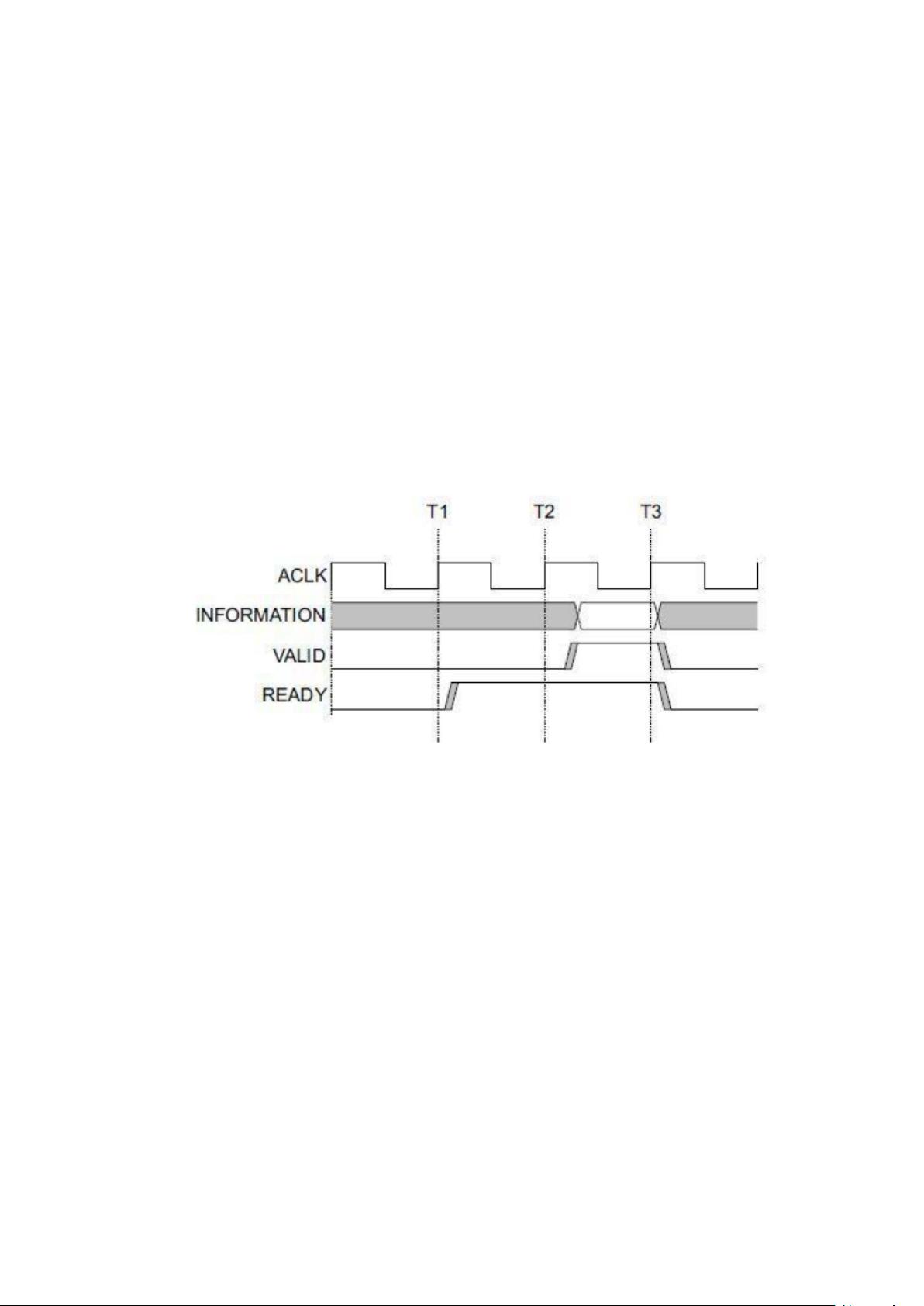

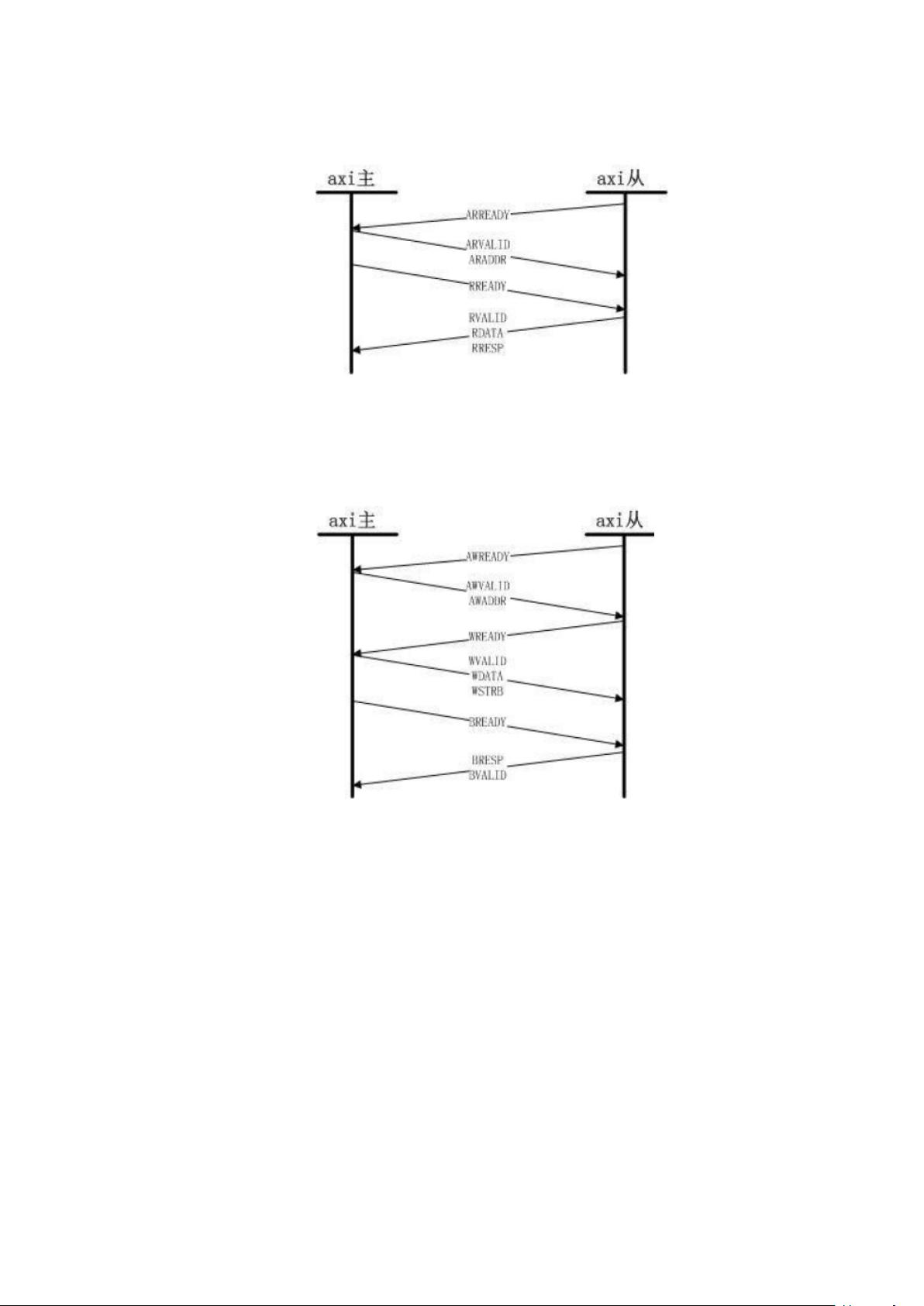

AXI4 所采用的是一种 READY,VALID 握手通信机制,即主从模块进行数据通信前,先

根

据操作对各所用到的数据、地址通道进行握手。主要操作包括传输发送者 A 等到传输

接受者 B

的 READY 信号后,A 将数据与 VALID 信号同时发送给 B,这是一种典型的握手机制。

AXI 总线分为五个通道:

� 读地址通道,包含 ARVALID, ARADDR, ARREADY 信号;

� 写地址通道,包含 AWVALID,AWADDR, AWREADY 信号;

� 读数据通道,包含 RVALID, RDATA, RREADY, RRESP 信号;

� 写数据通道,包含 WVALID, WDATA,WSTRB, WREADY 信号;

� 写应答通道,包含 BVALID, BRESP, BREADY 信号;

� 系统通道,包含:ACLK,ARESETN 信号;

其中 ACLK 为 axi 总线时钟,ARESETN 是 axi 总线复位信号,低电平有效;读写数据

与读

写地址类信号宽度都为 32bit;READY 与 VALID 是对应的通道握手信号;WSTRB 信号

为 1 的

bit 对应 WDATA 有效数据字节,WSTRB 宽度是 32bit/8=4bit;BRESP 与 RRESP 分别

为写回

应信号,读回应信号,宽度都为 2bit,‘h0 代表成功,其他为错误。

读操作顺序为主与从进行读地址通道握手并传输地址内容,然后在读数据通道握手并传

输

- 1

- 2

前往页