没有合适的资源?快使用搜索试试~ 我知道了~

zynq7020芯片手册Xilinx-XCR3064XL

温馨提示

试读

10页

zynq7020芯片手册Xilinx-XCR3064XL

资源推荐

资源详情

资源评论

DS017 (v2.4) September 15, 2008 www.xilinx.com 1

Product Specification

© 2000–2008 Xilinx, Inc. All Xilinx trademarks, registered trademarks, patents, and disclaimers are as listed at http://www.xilinx.com/legal.htm.

All other trademarks and registered trademarks are the property of their respective owners. All specifications are subject to change without notice.

Features

• Low power 3.3V 64 macrocell CPLD

• 5.5 ns pin-to-pin logic delays

• System frequencies up to 192 MHz

• 64 macrocells with 1,500 usable gates

• Available in small footprint packages

- 44-pin VQFP (36 user I/O pins)

- 48-ball CS BGA (40 user I/O pins)

- 56-ball CP BGA (48 user I/O pins)

- 100-pin VQFP (68 user I/O pins)

• Optimized for 3.3V systems

- Ultra-low power operation

- Typical Standby Current of 17 μA at 25°C

- 5V tolerant I/O pins with 3.3V core supply

- Advanced 0.35 micron five layer metal EEPROM

process

- Fast Zero Power CMOS design technology

- 3.3V PCI electrical specification compatible

outputs (no internal clamp diode on any input or

I/O, no minimum clock input capacitance)

• Advanced system features

- In-system programming

- Input registers

- Predictable timing model

- Up to 23 available clocks per function block

- Excellent pin retention during design changes

- Full IEEE Standard 1149.1 boundary-scan (JTAG)

- Four global clocks

- Eight product term control terms per function block

• Fast ISP programming times

• Port Enable pin for dual function of JTAG ISP pins

• 2.7V to 3.6V supply voltage at industrial temperature

range

• Programmable slew rate control per macrocell

• Security bit prevents unauthorized access

• Refer to XPLA3 family data sheet (DS012

) for

architecture description

Description

The CoolRunner™ XPLA3 XCR3064XL device is a 3.3V,

64-macrocell CPLD targeted at power sensitive designs

that require leading edge programmable logic solutions. A

total of four function blocks provide 1,500 usable gates.

Pin-to-pin propagation delays are as fast as 5.5 ns with a

maximum system frequency of 192 MHz.

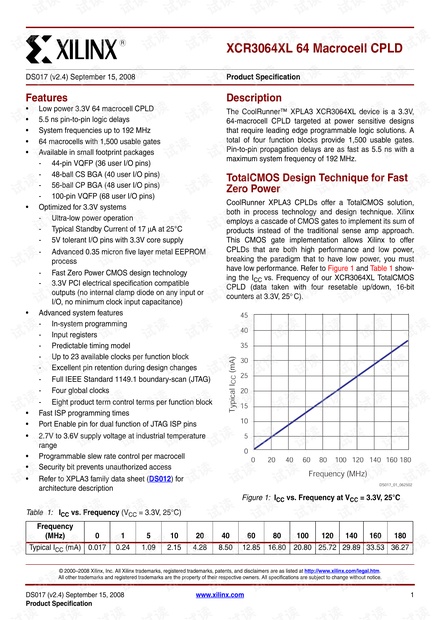

TotalCMOS Design Technique for Fast

Zero Power

CoolRunner XPLA3 CPLDs offer a TotalCMOS solution,

both in process technology and design technique. Xilinx

employs a cascade of CMOS gates to implement its sum of

products instead of the traditional sense amp approach.

This CMOS gate implementation allows Xilinx to offer

CPLDs that are both high performance and low power,

breaking the paradigm that to have low power, you must

have low performance. Refer to Figure 1 and Table 1 show-

ing the I

CC

vs. Frequency of our XCR3064XL TotalCMOS

CPLD (data taken with four resetable up/down, 16-bit

counters at 3.3V, 25° C).

0

XCR3064XL 64 Macrocell CPLD

DS017 (v2.4) September 15, 2008

014

Product Specification

R

Figure 1: I

CC

vs. Frequency at V

CC

= 3.3V, 25°C

0

5

1

0

1

5

2

0

2

5

30

35

4

0

4

5

0

2

0

4

0

6

0

8

0

1

00

12

0

18

0

14

0

16

0

Frequenc

y

(MHz)

D

S017

_

01

_

06250

2

Ty

pical

I

CC

(

mA

)

Tabl e 1: I

CC

vs. Frequency (V

CC

= 3.3V, 25°C)

Frequency

(MHz) 0 1 5 10 20 40 60 80 100 120 140 160 180

Typical I

CC

(mA) 0.017 0.24 1.09 2.15 4.28 8.50 12.85 16.80 20.80 25.72 29.89 33.53 36.27

资源评论

yxldr2023-07-28虽然有部分章节较为复杂,但手册中提供了大量的示例代码和实际应用案例,帮助读者更好地理解和应用芯片。

yxldr2023-07-28虽然有部分章节较为复杂,但手册中提供了大量的示例代码和实际应用案例,帮助读者更好地理解和应用芯片。 73232023-07-28这份手册的编写风格简洁明了,条理清晰,对于熟悉硬件设计的人来说非常友好。

73232023-07-28这份手册的编写风格简洁明了,条理清晰,对于熟悉硬件设计的人来说非常友好。 明儿去打球2023-07-28该手册的内容丰富,涵盖了芯片的架构、引脚定义、时钟控制等重要内容,对于开发人员来说十分方便。

明儿去打球2023-07-28该手册的内容丰富,涵盖了芯片的架构、引脚定义、时钟控制等重要内容,对于开发人员来说十分方便。 我只匆匆而过2023-07-28手册中清晰地介绍了Xilinx-XCR3064XL芯片的功能和特点,对于工程师来说非常实用。

我只匆匆而过2023-07-28手册中清晰地介绍了Xilinx-XCR3064XL芯片的功能和特点,对于工程师来说非常实用。 我有多作怪2023-07-28这份手册提供了详细的关于zynq7020芯片的信息,适合初学者了解和使用。

我有多作怪2023-07-28这份手册提供了详细的关于zynq7020芯片的信息,适合初学者了解和使用。

不觉明了

- 粉丝: 3101

- 资源: 5337

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功