没有合适的资源?快使用搜索试试~ 我知道了~

温馨提示

试读

17页

本文档详细描述了基于Xilinx Zynq 7020 SOC的自定义IP的实现,并带领大家一步步完成自定义用户逻辑IP与Zynq ARM通过AXI-Lite通讯的实验。教程非常详细包括FPGA部分和SDK软件部分的开发,以及自定义驱动文件的创建和使用等。 ZYNQ芯片的PL部分也就是FPGA部分,定义了一个用户逻辑的IP,实现将两个输入的32bit的数据相加。自定义的用户逻辑IP中设计了4个寄存器,其中3个配置寄存器(可读、可写)和一个状态寄存器(只读)。 ARM处理器通过写配置寄存器slv_reg0和slv_reg1分别写入两个输入数据,用户逻辑做加法运算,计算相加的结果放入slv_reg3寄存器中。slv_reg3寄存器作为自定义IP的状态寄存器使用,不能写,只能读。ARM处理器读取slv_reg3寄存器中的数据,并将结果显示在串口调试工具窗口中。

资源推荐

资源详情

资源评论

XILINX_ZYNQ7020_自

定义 IP 开发文档

Xilinx ZYNQ 嵌入式 Linux 开发系列

2020-2-26

IHEP

longw@ihep.ac.cn

目录

1 系统设计...............................................................................................................................2

2 使用自定义 IP........................................................................................................................2

3 Vivado 工程建立....................................................................................................................3

3.1 处理器 IP 的配置........................................................................................................3

3.2 创建自定 IP.................................................................................................................4

4 SDK 软件工程开发..............................................................................................................13

1 系统设计

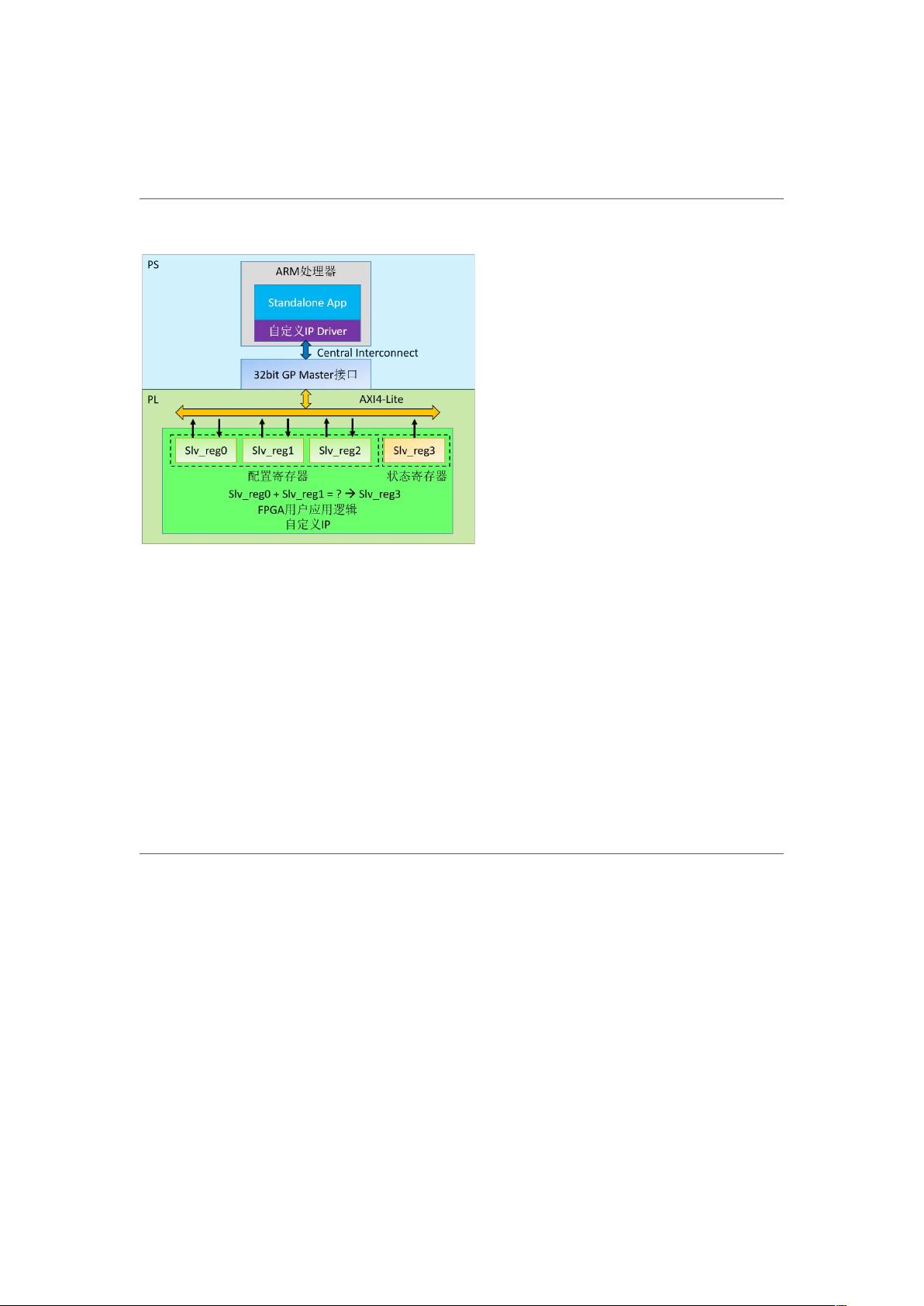

本文档中的示例实验的系统设计框图如下图所示。

ZYNQ 芯片的 PL 部分也就是 FPGA 部分,定义了一个用户逻辑的 IP,实现将两个输入的

32bit 的数据相加。自定义的用户逻辑 IP 中设计了 4 个寄存器,其中 3 个配置寄存器

(可读、可写)和一个状态寄存器(只读)。

ARM 处理器通过写配置寄存器 slv_reg0 和 slv_reg1 分别写入两个输入数据,用户逻辑

做加法运算,计算相加的结果放入 slv_reg3 寄存器中。slv_reg3 寄存器作为自定义 IP 的

状态寄存器使用,不能写,只能读。ARM 处理器读取 slv_reg3 寄存器中的数据,并将

结果显示在串口调试工具窗口中。

2 使用自定义 IP

Xilinx 官方提供了许多的 IP 核,在 Vivado 中我们通过 IP Catalog 可以管理、添加和查看

这些 IP 核。然后用户在构建自己的系统时,有时候需要使用自己的用户 IP 核。创建自

定义 IP 核将使系统设计层次结构和模块化结构更加的清晰;增加功能模块的设计复用

性,简化系统设计和缩短设计时间;可以在 IP 核中加入 license 有偿提供给别人使用。

在 ZYNQ 嵌入式开发中最常用的就是使用 AXI 总线将 PS 同 PL Fabric 的 IP 核连接起来。

本实验将为大家介绍如何在 Vivado 中创建一个 AXI 总线的自定义 IP,并且创建该 IP 的

驱动函数库,并在 SDK 应用程序中读写该自定义 IP 中的寄存器。

3 VIVADO 工程建立

3.1 处理器 IP 的配置

ALINX AX7020 的使用的是 Xilinx 公司的 Zynq7000 系列的 SOC 芯片。

SOC 芯片的型号为 XC7Z020-2CLG400I。

芯片上的 PS 系统集成了两个 ARM Cortex-A9 处理器。

FPGA 硬件工程师需要在工程中添加和配置好 PS 端 ARM 内核,以及 PS 端的外设。

步骤如下:

1. 新建一个 Vivado 工程,工程名“custom_ip”。

2. 创建一个 Block 设计,添加一个 ZYNQ7 Processing System 的 IP 核。根据开发板原理

图和用户手册配置参数。

3. 通过阅读原理图可以得知外设 IO 的 MIO 的 BANK0 的电平为 3.3V,BANK1 的电平为

1.8V,因此将 BANK0 配置为 LVCOMS3.3V,BANK1 配置为 LVCOMS1.8V。

4. 串口的 TX 和 RX 分别连接到 MIO48-MIO49,因此配置为 UART1(MIO48-MIO49)。

5. QSPI FLASH 的芯片型号为 W25Q256,配置 QSPI FLASH,选择 Single SS 4bit IO。

6. 开发板上有两个 4Gbis 的 DDR3 SDRAM,配置为兼容“MT41J128M16 RE-125”,总线

位宽为“32bit”。

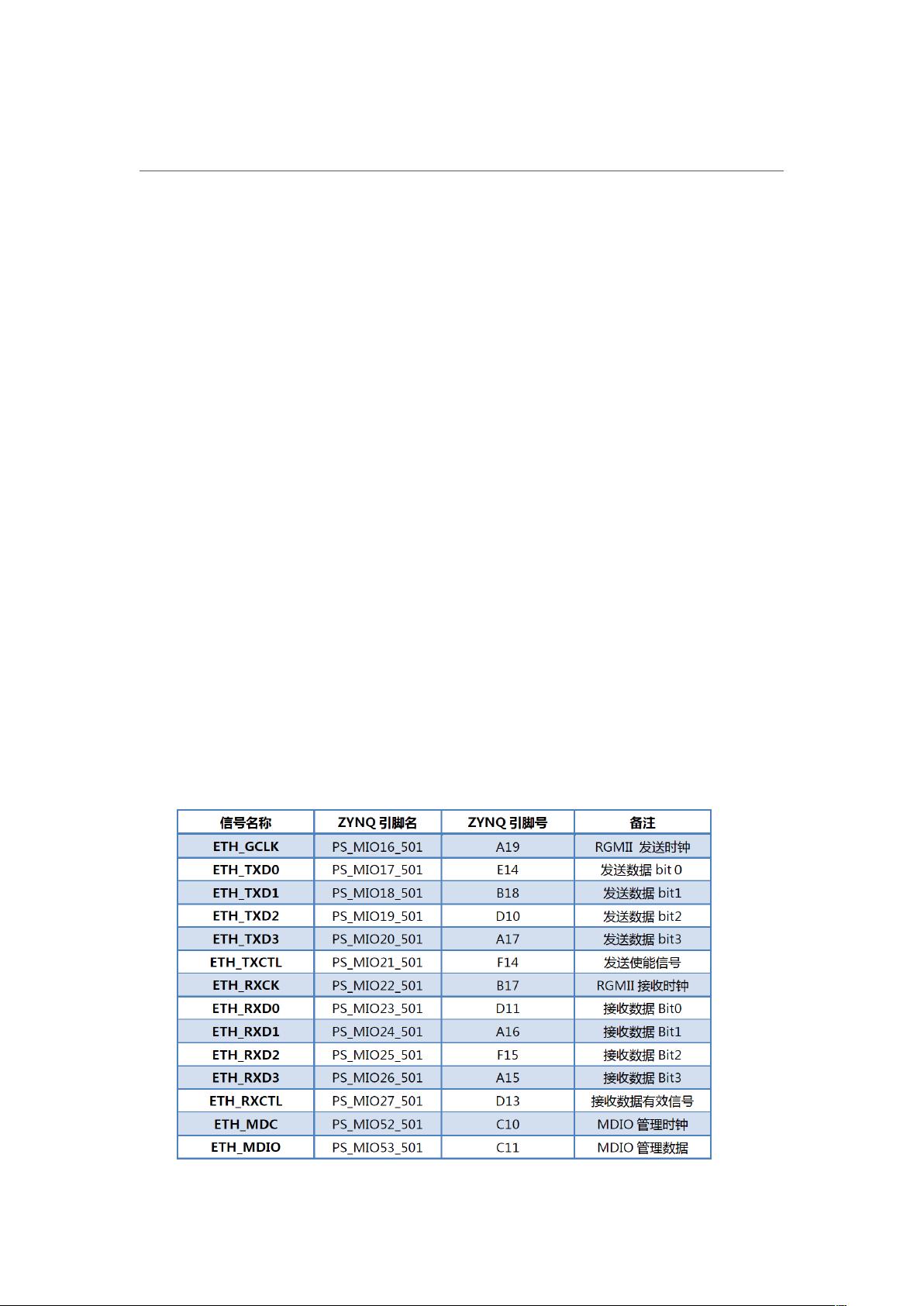

7. 千兆以太网的引脚接口如下:

剩余16页未读,继续阅读

资源评论

陈游泳2023-07-27这个文档对于Xilinx_ZYNQ7020自定义IP开发非常实用,内容丰富,适合广大开发者使用。

陈游泳2023-07-27这个文档对于Xilinx_ZYNQ7020自定义IP开发非常实用,内容丰富,适合广大开发者使用。 VashtaNerada2023-07-27文档中的示例代码简洁易懂,对于新手来说也很友好。

VashtaNerada2023-07-27文档中的示例代码简洁易懂,对于新手来说也很友好。 航知道2023-07-27文档中对于常见问题的解答也很到位,对于遇到问题的开发者来说是一个很好的参考。

航知道2023-07-27文档中对于常见问题的解答也很到位,对于遇到问题的开发者来说是一个很好的参考。 MsingD2023-07-27这份文档详细介绍了Xilinx_ZYNQ7020自定义IP的开发流程,能够帮助开发者快速上手。

MsingD2023-07-27这份文档详细介绍了Xilinx_ZYNQ7020自定义IP的开发流程,能够帮助开发者快速上手。 学习呀三木2023-07-27文档中的指导步骤清晰明了,让人能够轻松上手进行开发。

学习呀三木2023-07-27文档中的指导步骤清晰明了,让人能够轻松上手进行开发。

weixin_43354598

- 粉丝: 173

- 资源: 8

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 南京邮电大学数学实验:熟练掌握 Matlab 软件的基本命令和操作

- 2017校招真题校园招聘真题算法题(37道)Python源码.zip

- 基于单片机protues仿真的多功能自动饮水机系统设计(仿真图、源代码、演示视频)

- 二叉树7-1-1.cpp

- android 9.0 原生模拟器 签名文件

- 技术面试最后反问面试官的话 校招面试非技术问题有哪些 非技术问题如何回答.png

- NB-IOT-BC26全网通模块Altium+ CADENCE +PADS三种格式(原理图SCH+PCB封装库)文件.zip

- 基于微信小程序开发的校园失物招领系统源码毕业设计(优质项目源码).zip

- 词向量是一种将自然语言中的单词转换为数值向量的技术,它能够捕捉词义和上下文信息

- nmap与masscan的简单使用

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功